文章来源:数字站

在此之前我对原语的理解就跟IP核一样,只是更直接的调用底层组件,事实也确实如此,也没有使用过原语,全部通过IP手册然后调用相关IP即可,比如锁相环,FIFO,FIR,FFT,ROM,RAM这些常用IP。

但此次在编写HDMI接口驱动的时候,需要将单沿采样信号变为双沿采样的信号输出,还需要把单端信号转换为差分信号输出。实现这些功能可以调用SelectIO的IP,但是这个IP包含IDDR、ODDR、IDELAYE2等很多功能,单独调用个别功能还是比较麻烦。

此时使用原语就可以只调用需要的组件,不需要去考虑其余组件参数设置,就方便很多,借助此次机会就对IDDR、ODDR、IDELAYE2、ODELAYE2、IDELAYCRTL、ISERDESE、OSERDESE等几个原语做了简要了解,并对原语的各个模式进行了仿真,本文最初是介绍IDDR的,但在介绍IDDR这些原语之前,还需要了解一下7系列FPGA bank的分类和区别,所以就有了本文。

原语是什么

原语(Primitive)是Xilinx针对其器件特征开发的一系列常用模块的名称,涵盖了FPGA开发过程中的常用领域,方便用户直接调用FPGA的底层组件。

Xilinx FPGA的底层组件分为10类,计算组件、IO端口组件、寄存器/锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、slice/CLB组件以及G-tranceiver,相应的原语也分为10类。

举个例子,比如把FPGA的100MHz时钟信号转换为200MHz时钟信号使用,第一时间肯定想到使用锁相环进行倍频,然后就去调用锁相环的一个IP核,IP核的底层再去调用时钟组件的原语实现倍频。如果对锁相环的原语足够熟悉,那么用户就可以直接调用原语,省去中间Vivado/ise生成IP核的步骤,Vivado运行速度是很慢的,从而节省更多时间。

一个稍微复杂点的IP核包含参数很多的,只是常用的配置就那么几个,比如锁相环IP常用参数就配置输入时钟频率,输出时钟频率、相位、占空比就行了,但实际上这个IP核还有很多参数没有配置,只是使用了默认参数而已。在调用原语时,通常也只需要关注常用的参数配置即可,但是第一次使用相关原语,还是推荐查看手册,了解每个参数的含义,将参数使用方式整理,便于后续灵活使用。

对原语的调用可以理解为调用相同组件的IP。

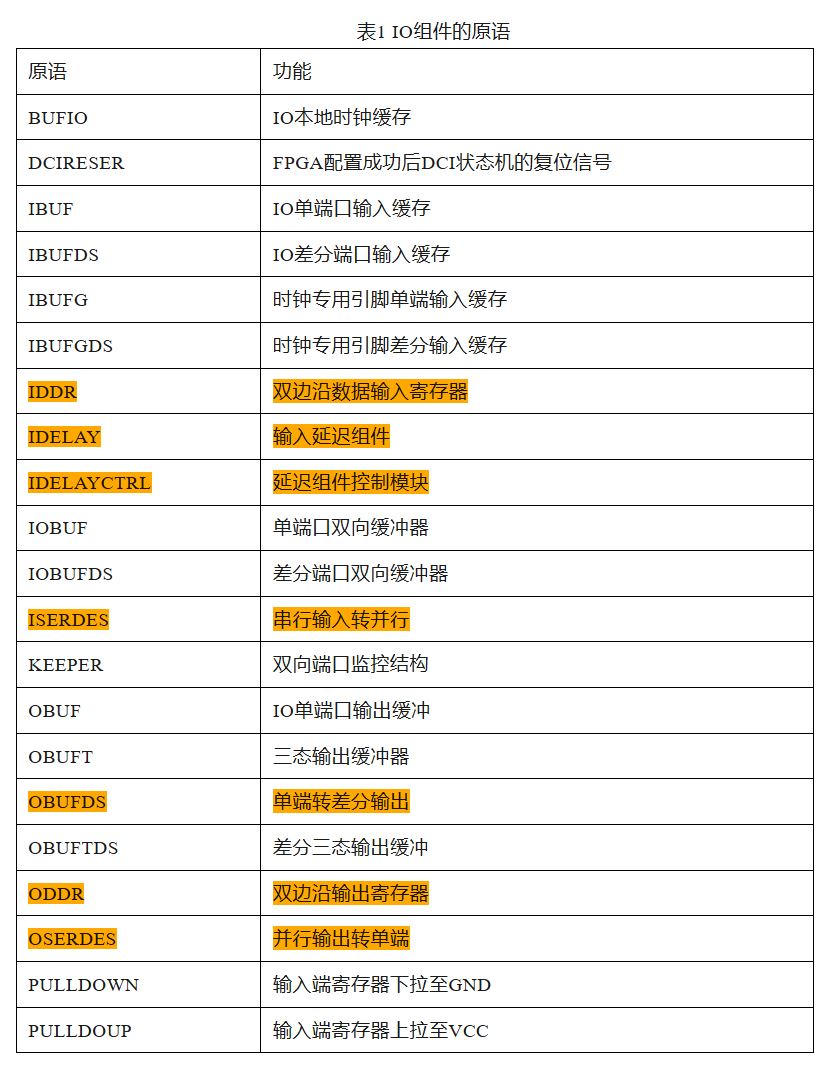

由于后续HDMI、千兆网相关接口需要用到一些原语,所以最近将相关原语手册(UG471)进行整理、仿真,便于后续使用,涉及原语有IDDR、ODDR、IDELAY、ODELAY、ISERDESE、OSERDESE等。这些原语都属于IO组件的原语,IO组件的原语如下表1所示。

zynq7000系列bank分布

xilinx7系列FPGA主要包括:Spartan®-7、Artix®-7、Kintex®-7、Virtex®-7,其性能/密度/价格也随着系列的不同而提升。S7、A7、K7、V7的实际工艺不同,又构成了不同的FPGA系列,如图1所示。

常见的zynq 7000就是采用28nm工艺生产的,如图2所示,该系列只有A7和K7两种,zynq 7030及以上的PL是K7,zynq 7020及以下都是A7。

Xilinx的FPGA bank主要分为三类,而zynq 7000系列只有HR(最大电压支持3.3V)和HP(最大电压支持1.8V)两种,HP的性能会比HR强,电压范围更窄。

下面来看下zynq 7000各个型号的bank类型,如图3所示,为zynq7010的bank类型图,PL部分只有两个HR类型的bank。

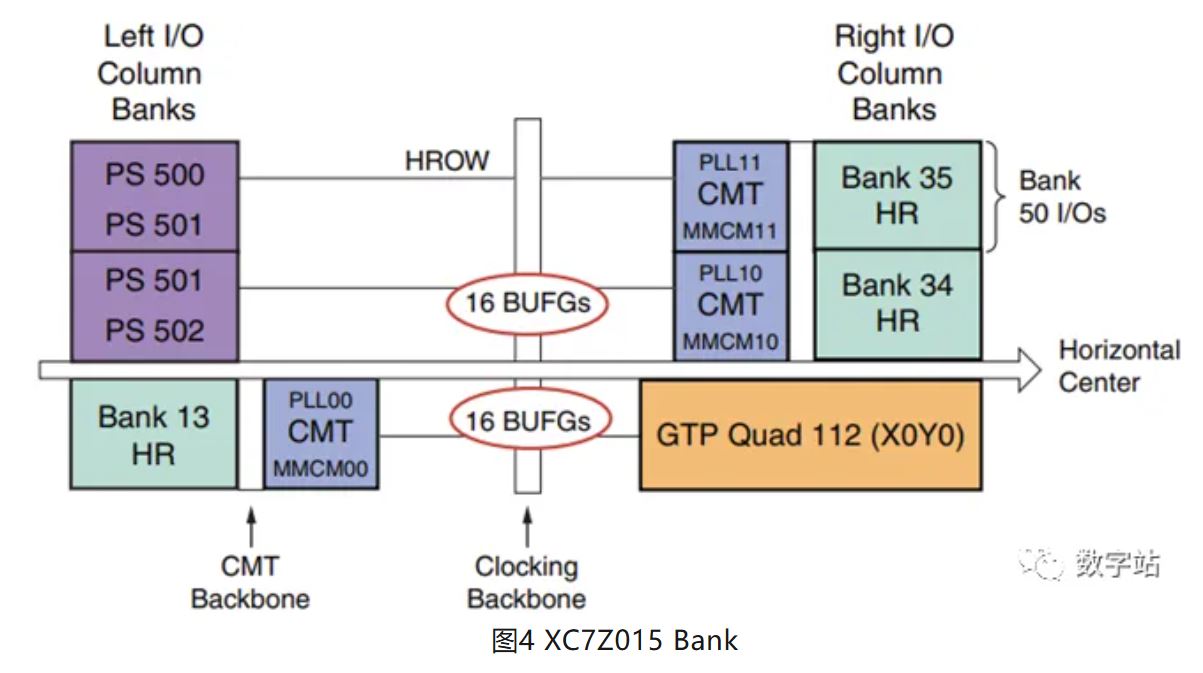

图4是zynq 7015的bank类型图,PL部分包含三个HR bank和一个高速收发器GTP bank,可以用于万兆以太网和PCIE的数据收发。

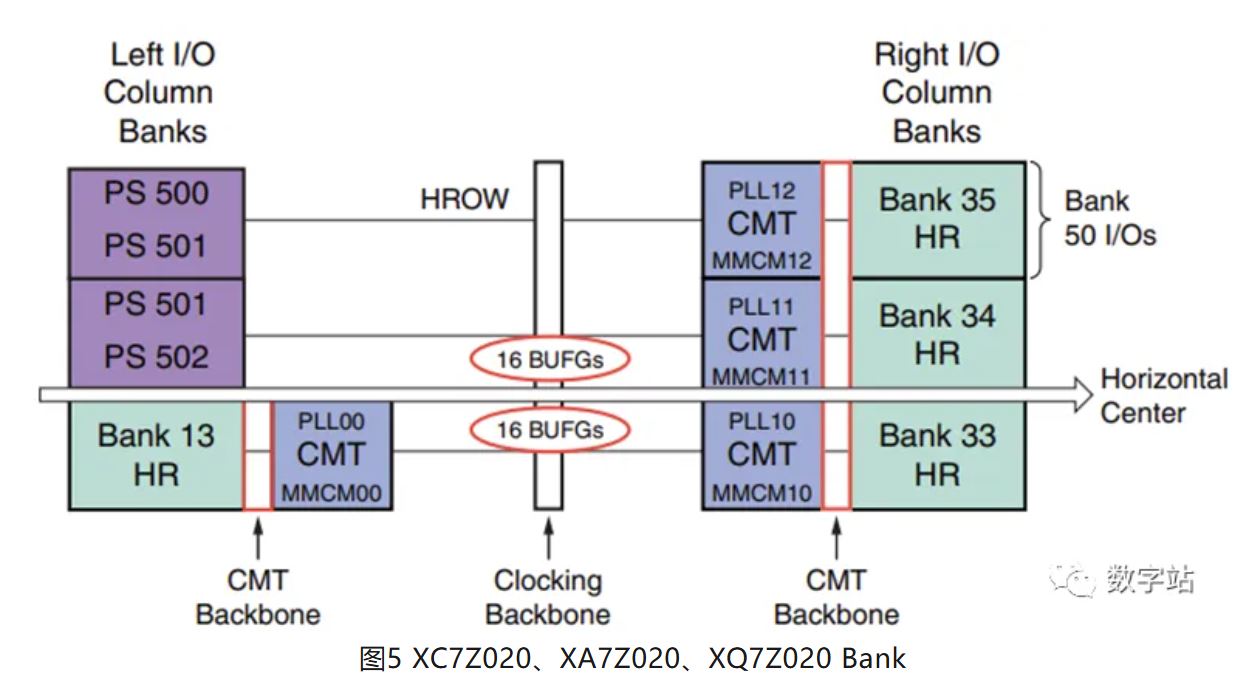

图5是zynq 7020的bank类型图,PL部分包括四个HR bank,没有高速收发器相关的bank。

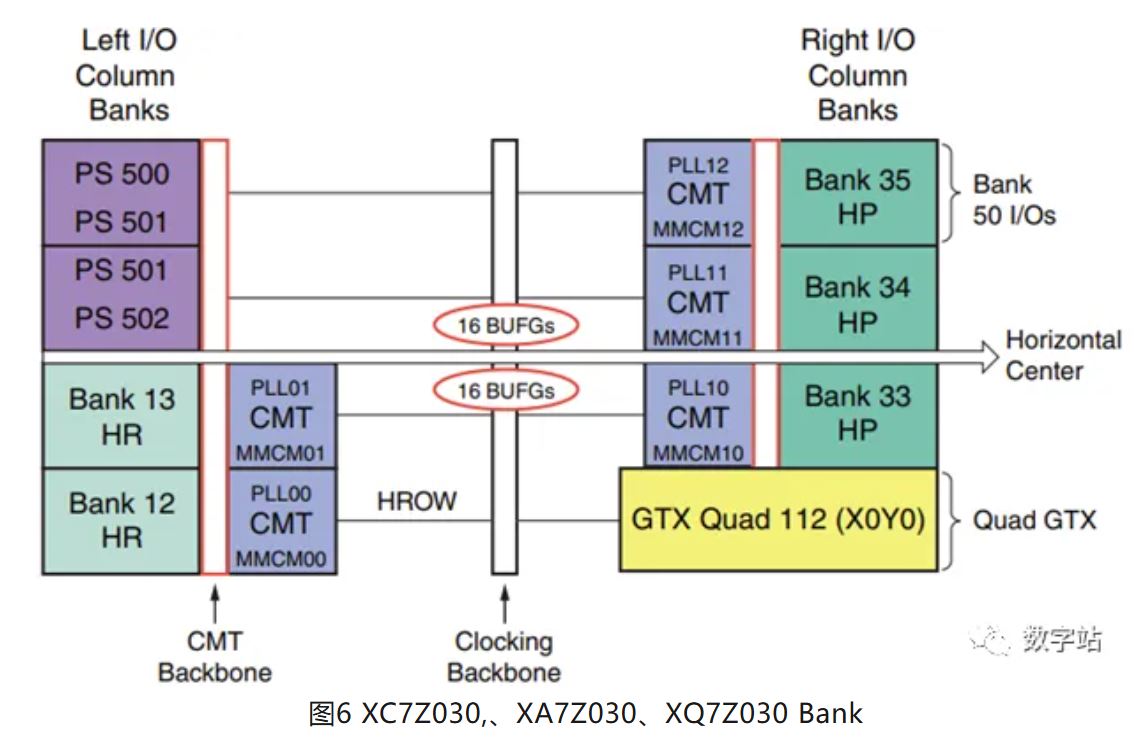

图6是zynq 7030的bank类型图,zynq7030属于K7系列,PS部分与前面的zynq都是一样的,PL部分有2个HR bank,还有3个HP bank,最后包括一个GTX的高速收发器bank。GTX最大速率接近GTP最大速率的2倍,提升比较明显。

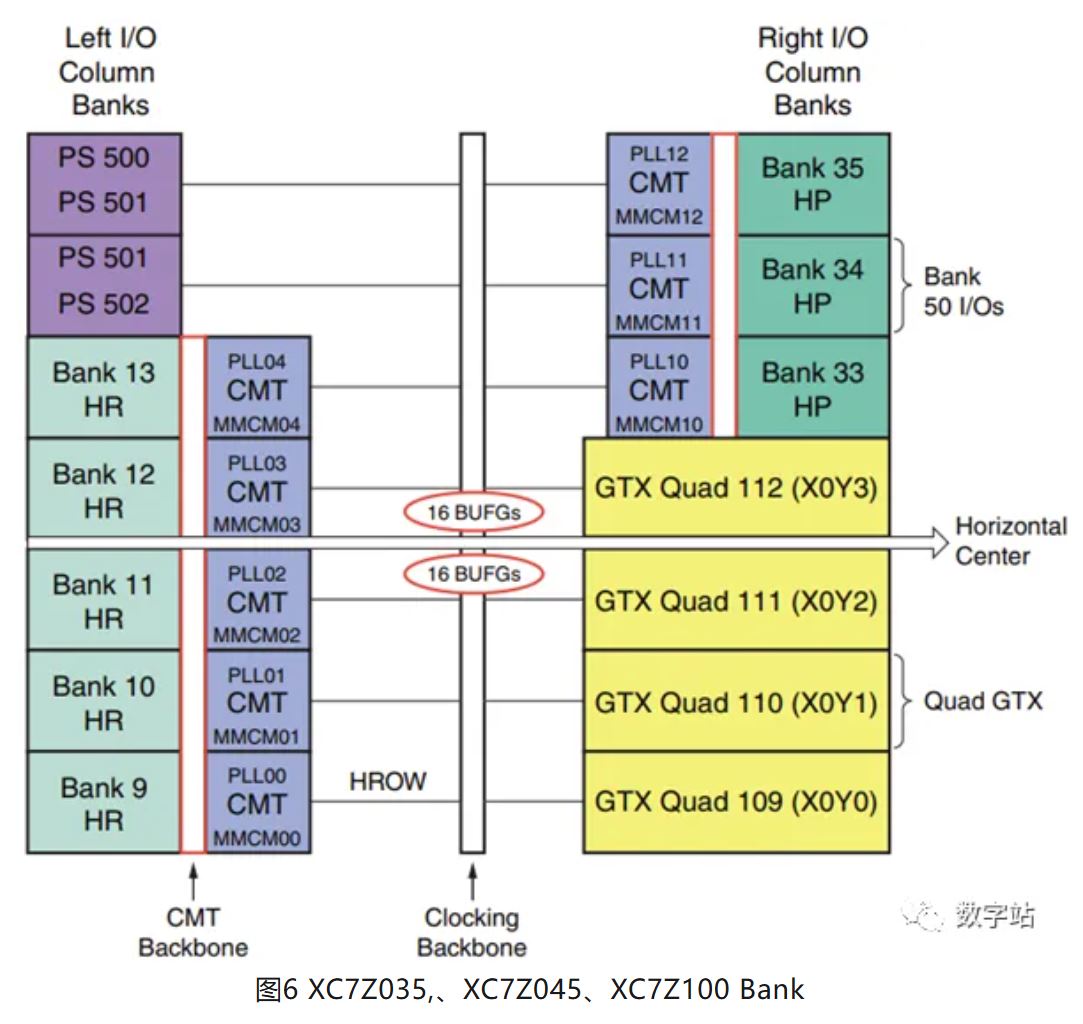

图7是zynq 7035、zynq 7045、zynq 7100的bank类型图,这几个芯片的区别在于逻辑资源的多少不同,bank类型一致,都包含5个HR bank,三个HP bank,四个高速收发器的bank。

通过上面几张图可知,A7系列只有HR bank,而K7有HP bank,还会包含高速收发器bank。

Xilinx 7系列的HR BANK与HP BANK

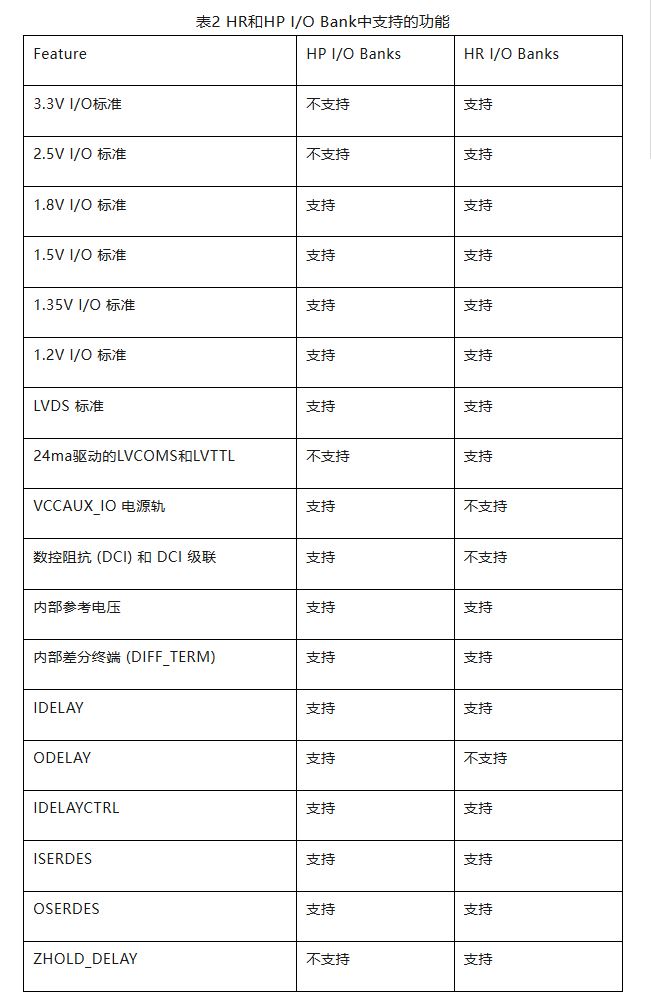

A7只有高范围(HR) I/O bank,支持更广泛的I/O电平标准,最高支持3.3V,而K7有高性能(HP) I/O bank,旨在满足高速内存和其他电压高达1.8V的芯片间接口的性能,表2是HR和HP I/O Bank中支持的功能。除逻辑资源不同外,另外的区别在于高速收发器的最大速率不同,A7的高速收发器是GTP,速率范围500Mb/s~6.6Gb/s,因此A7无法实现万兆网,而K7高速收发器是GTX,速率范围500Mb/s~12.5Gb/s,能够实现万兆网的收发速率。

注意上表中HR bank是不支持ODELAY原语的,没有相应的硬件支持。

除某些例外,每个I/O Bank包含50个SelectIO引脚,每个bank最末端的两个引脚只能作为单端I/O标准使用,其余48个引脚可用于单端或差分标准,使用两个SelectIO引脚组合在一起作为差分 (P/N) 对。每个SelectIO资源都包含输入、输出和三态驱动程序。

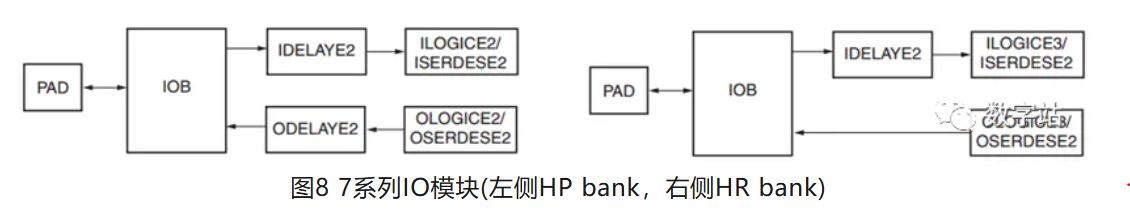

图8是HP bank与HR bank的IO模块,其中PAD是FPGA的金属管脚,IOB是输入、输出引脚的控制模块。FPGA的外部信号通过PAD进入FPGA,然后经过IOB,可能会经过IDELAY2延迟,进入ILOGICE2进行寄存或者双沿转单沿的处理,最后给FPGA内部。输出信号先在OLOGICE2进行寄存或者单沿转双沿信号,然后可能经过ODELAY2延时处理后输出到IOB模块,最后通过PAD引脚输出。

IDELAY2是输入数据的延时模块,可以调用原语实现,对于并行数据,可能信号的PCB走线并没有做等长处理,导致并行数据不同位到达管脚的延迟时间不同,此时就以PCB走线延迟最长位标准,将其余信号进行延迟,从而实现数据对齐。输出端口延迟的原理一致,只不过只有K7的HP bank才有ODELAYE2结构。

ILOGICE2和ILOGICE3的结构差不多,区别在于ILOGICE2没有零保持延迟元件(ZHOLD),不能调用ZHOLD_DELAY原语。ILOGICE2和ILOGICE3都可以实现组合逻辑输入、寄存器输入、以及DDR双沿采样(IDDR)输入,并不能通过原语直接调用ILOGICE2,只能通过原语调用IDDR去使用ILOGICE2资源。

ISERDESE2可以实现串行双沿采样转换为并行单沿采样,OSERDESE2与ISERDESE2功能刚好相反,比如实现HDMI接口时可以使用ODDR实现单沿转双沿,但是使用OSERDESE2会更方便,还能同时实现并行转串行,根据实际情况选择对应原语即可。

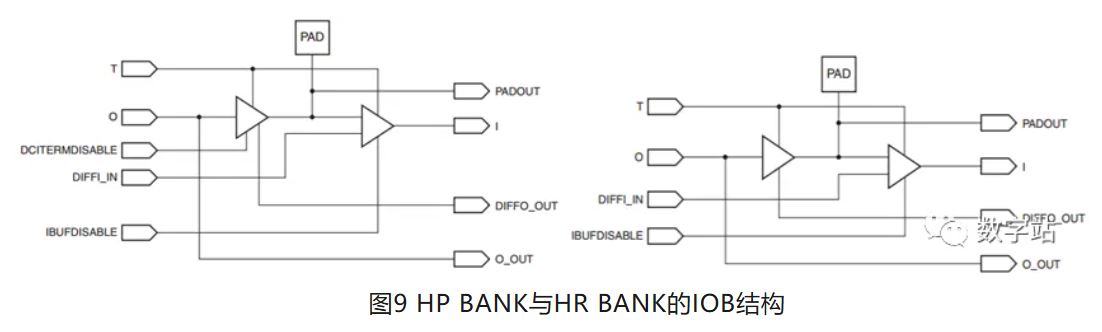

图9左侧是HP bank的IOB结构,右侧是HR bank的IOB结构,HP bank多一个可以控制数控阻抗(DCI)的信号DCITERMDISABLE,其余结构都一样。其中PAD是FPGA的金属管脚,该管脚可作为输入也可作为输出,通过I、O信号实现单端输入、输出,DIFF_IN和IDFFO_OUT实现差分输入、输出,但是差分信号需要两个管脚进行配合实现。

IOB是FPGA输入、输出控制模块,并没有直接对应的原语,但是IO可以实现单端转差分吗,差分转单端的功能,所以可以通过调用OBUFDS原语在IOB模块内实现单端转差分的输出功能。

本文主要对7系列FPGA的bank进行简单介绍,有利于后续几节内容详细讲解几个常用原语的参数及仿真。

文中的图来自xilinx的几个手册:

zynq-7000-product-selection-guide

ug471_7Series_SelectIO

ug865-Zynq-7000-Pkg-Pinout

后续还会用到的手册

ds181_Artix_7_Data_Sheet

这些手册可直接在官网获取。