文章来源:FPGA入门到精通

FPGA开发中IO约束是不可缺少的部分,正确的电平约束是确保电路稳定运行与兼容性的关键所在。

今天分享下IO约束中常用的电平标准,帮助大家快速理解和掌握。

一、 LVTTL系列

LVTTL全称为Low - Voltage Transistor - Transistor Logic,是一种低压数字逻辑电平标准,主要用于数字集成电路之间的信号传输。。

1、LVTTL33

3.3V 的低压 TTL 电平标准,常用于中低速数字电路接口。

输出信号,高电平(VOH)最小值通常为2.4V,低电平(VOL)最大值为 0.4V。

输入信号,高电平(VIH)最小值为 2.0V,低电平(VIL)最大值为 0.8V。

2、LVTTL25

2.5V 的低压 TTL 电平标准。

输出信号,高电平(VOH)最小值通常为 2.0V,低电平(VOL)最大值为 0.2V。

输入信号,高电平(VIH)最小值为 1.7V,低电平(VIL)最大值为 0.7V。

二、LVCMOS系列

LVCMOS全称为Low - Voltage Complementary Metal - Oxide - Semiconductor,是一种低电压的 CMOS 技术数字集成电路的单端信号 I/O 标准。

1、LVCMOS33

电源电压(VCC)为 3.3V。

输出信号,高电平输出(VOH)通常要求大于等于 3.2V,低电平输出(VOL)要求小于等于 0.1V。

输入信号,高电平输入(VIH)需大于等于 2.0V,低电平输入(VIL)需小于等于 0.7V。

2、LVCMOS25

电源电压为 2.5V。

输出信号,高电平输出(VOH)要大于等于 2.0V,低电平输出(VOL)小于等于 0.1V。

输入信号,高电平(VIH)大于等于 1.7V,低电平(VIL)小于等于 0.7V。

相比 3.3V LVCMOS,其电压更低,适用于对功耗有更高要求或与其他 2.5V 逻辑电平设备相连接的场景。

3、LVCMOS18

电源电压是 1.8V。

输出信号,高电平输出(VOH)一般大于等于 1.7V,低电平输出(VOL)通常小于等于 0.1V。

输入信号,高电平输入(VIH)大于等于 1.4V,低电平输入(VIL)小于等于 0.6V。

这是一种更低电压的标准,常用于对功耗要求极为严格的便携式电子设备或低功耗应用场景。

4、LVCMOS15

电源电压(VCC)为1.5V。

输出信号,高电平输出(VOH)大于1.5V,低电平输出(VOL)则要尽可能接近0V。

输入信号,高电平输入(VIH)通常大于等于0.975V(0.65×VCC),低电平输入(VIL)小于等于0.525V(0.35×VCC)。

5、LVCMOS12

电源电压(VCC)为1.2V。

输出信号,高电平输出(VOH)要接近1.2V,低电平输出(VOL)接近0V。

输入信号,高电平输入(VIH)大于等于0.78V(0.65×VCC),低电平输入(VIL)小于等于0.42V(0.35×VCC)。

适用于对低电压、低功耗有较高要求的场景。

三、HSTL系列

HSTL全称为High - Speed Transceiver Logic,是由 JEDEC 在 1995 年正式制定的一种电路逻辑标准。它是一种高速总线标准,适用于高速数字电路和高速接口设计,常用于高速存储器接口等场景。

芯片的功率供电电压 VDD 没有在 JEDEC 规范中明确统一,常见值有 3.3V、2.5V、1.8V、1.5V 等,具体取决于芯片设计和应用需求。

芯片输出 Buffer 供电电压 VDDQ 典型值为 1.5V,决定了输出电压的摆幅范围为0~1.5V。

常见的电平标准有HSTL_I、HSTL_I_12、HSTL_I_18、HSTL_I_DCI、HSTL_I_12_DCI

、HSTL_I_18_DCI等。

其中DCI是Digitally Controlled Impedance ,即数字控制阻抗。这种标准在 HSTL 的基础上增加了数字控制阻抗的功能,能够更精确地控制信号的阻抗匹配,从而减少信号反射和失真,提高信号的完整性和传输质量。

四、SSTL系列

SSTL全称为Stub - Series Terminated Logic,是为了保证存储器系统更高的数据吞吐率而定义的,它的优点就是能够驱动多个负载,提供更小的信号摆幅、更快的信号边沿。

专门为高速存储器的应用开发而制定,特别针对于单双沿采样的SDRAM,如DDR SDRAM、DDR2、DDR3等。

1、SSTL25

电源电压(VCC)为2.5V。

输出信号,高电平输出(VOH)最小值为2.0V,低电平输出(VOL)最大值为0.2V。

输入信号,高电平输入(VIH)最小值为1.7V,低电平输入(VIL)最大值为0.7V。

常用于DDR SDRAM存储器接口;

2、SSTL18

电源电压(VCC)为1.8V。

输出信号,高电平(VOH)最小值为1.62V,低电平(VOL)最大值为0.45V。

输入信号,高电平输入(VIH)最小值为1.17V,低电平输入(VIL)最大值为0.63V。

常用于DDR2 SDRAM存储器接口;

3、SSTL15

电源电压(VCC)为1.5V。

输出信号,高电平(VOH)最小值为1.35V,低电平(VOL)最大值为0.45V。

输入信号,高电平输入(VIH)最小值为1.125V,低电平输入(VIL)最大值为0.375V。

常用于DDR3 SDRAM存储器接口;

4、其它

SSTL15的电压标准常用于DDR4 SDRAM存储器接口;

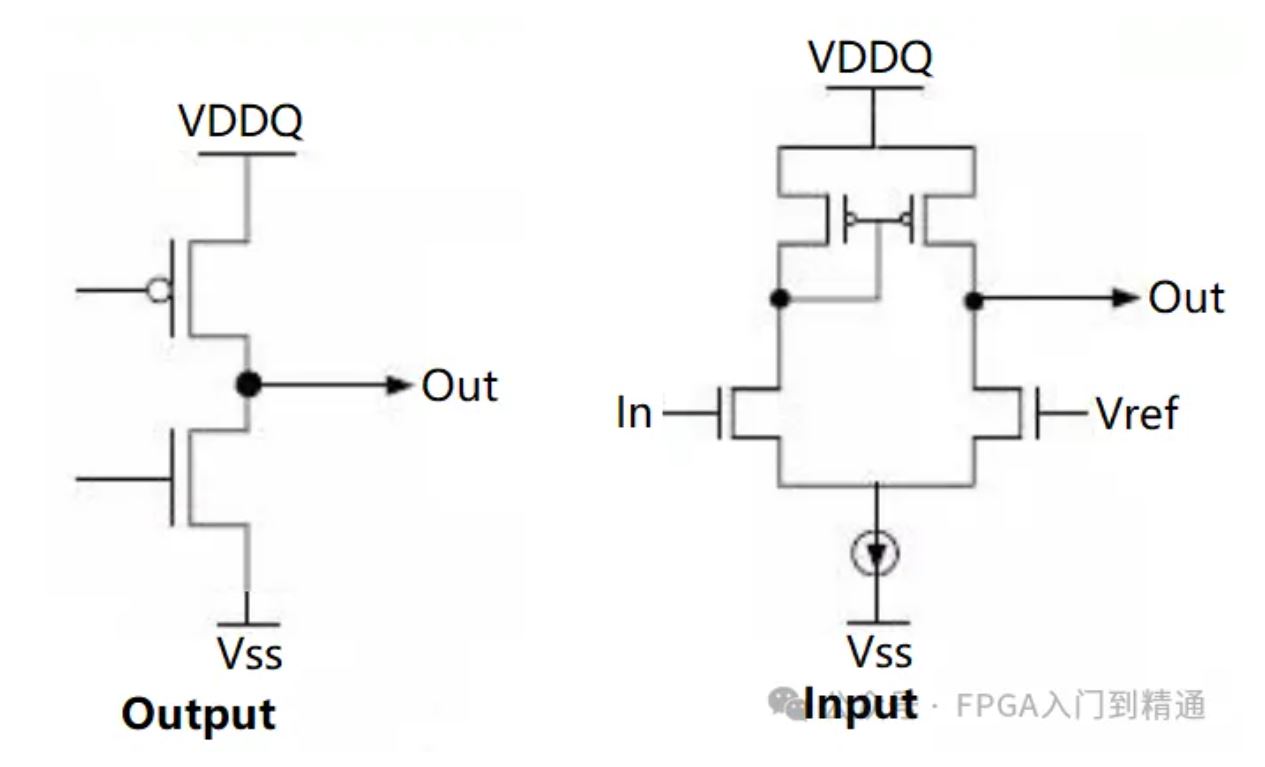

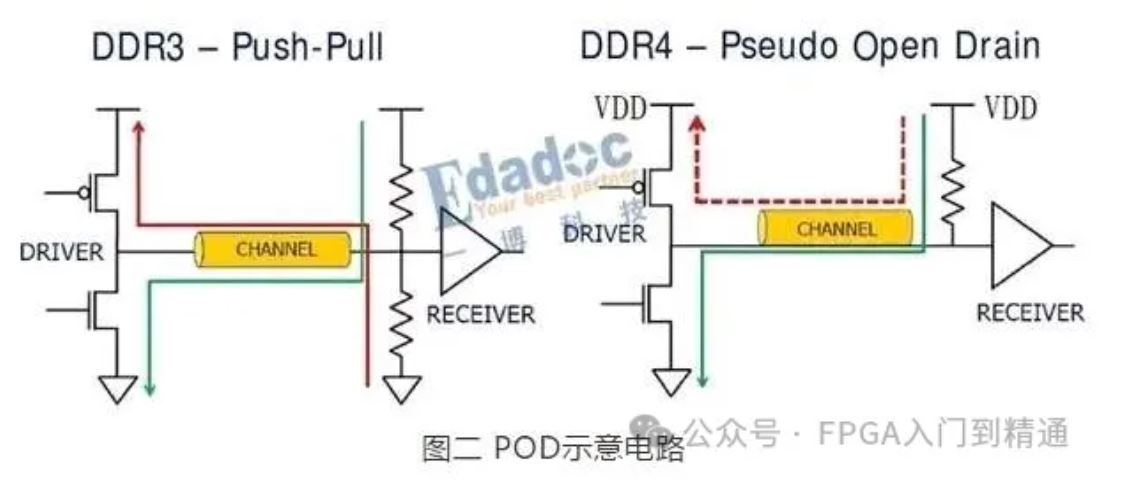

五、POD系列

POD电平标准是DDR4内存接口中采用的一种电平标准,全称为Pseudo Open Drain(伪开漏)。这种电平标准与传统的SSTL(Serial Interface Protocol)电平标准有所不同,SSTL电平标准在DDR3内存中使用,而POD电平标准则是DDR4内存所特有的。

POD电平标准的主要特点如下:

1、工作电压

POD电平标准的供电电压为1.2V,这是相对于DDR3内存的SSTL电平标准来说的,SSTL电平标准的供电电压通常为1.5V。

2、电流流向

在输出低电平时,POD电平标准的电流流向是从输出端口流向轨电压,而SSTL电平标准的电流则是从输出端口流向接收端。在输出高电平时,POD电平标准的电流流向是从轨电压流向输出端口,而SSTL电平标准的电流则是从接收端流向输出端口。

3、功耗

POD电平标准在输出高电平时,由于驱动端的上拉电路导通,回路上没有电流流过,这样的设计减少了功耗。相比之下,SSTL电平标准在输出高电平时仍然会有电流流过,因此功耗相对较高。

4、寄生引脚电容

POD电平标准可以降低寄生引脚电容,从而提高信号的传输速度和效率。

5、I/O终端功耗

POD电平标准的I/O终端功耗相对较低,这有助于降低系统的整体功耗。

6. 兼容性

POD电平标准与SSTL电平标准不兼容,因此POD电平标准只能用于DDR4内存,而不能用于DDR3内存。

总的来说,POD电平标准是一种针对DDR4内存设计的电平标准,它通过改进电流流向和功耗等特性,提高了内存的性能和效率。

五、差分信号系列

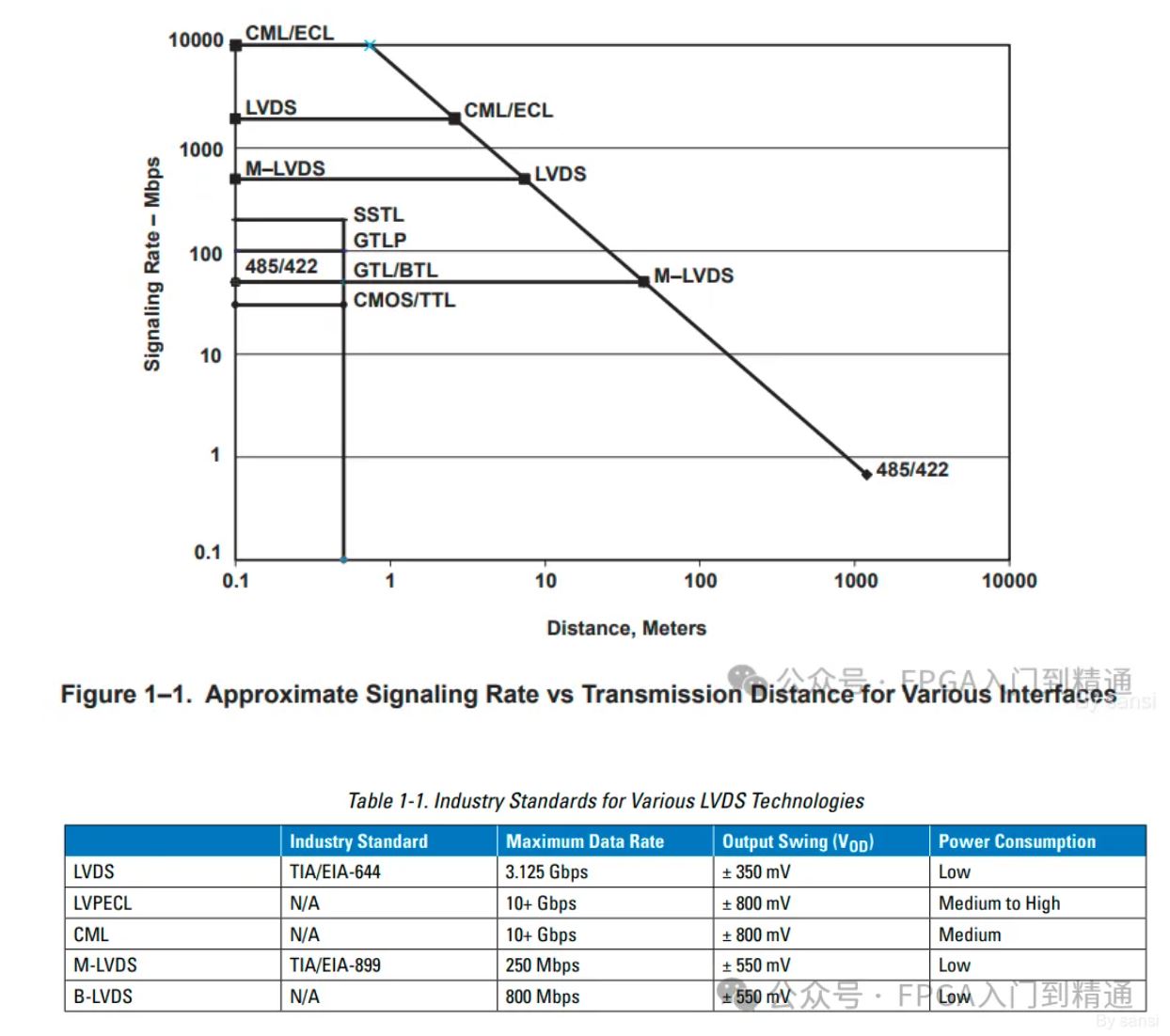

高速传输一般都是使用差分信号进行数据传输,这里也有不同的电平标准,传输速率和传输距离如下。

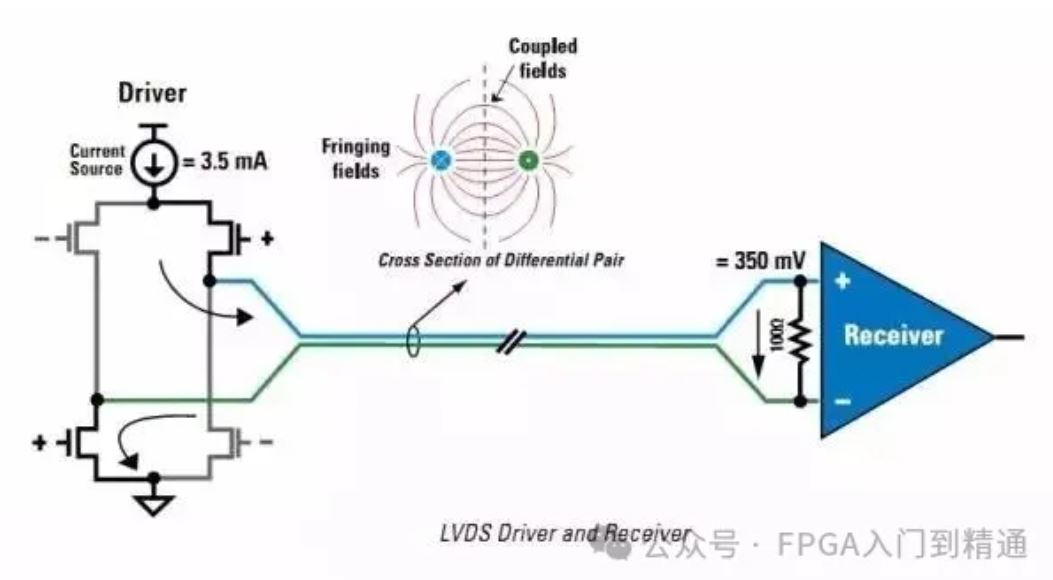

1、LVDS

LVDS(Low - Voltage Differential Signaling) :一种低电压差分信号标准,利用一对差分信号线来传输数据,两根线上的信号幅度相等、极性相反,典型电压摆幅在 350mV 左右。常用于高速、长距离数据传输,例如视频传输系统。

2、CML

CML(Current - Mode Logic) :以电流模式工作的差分信号电平标准,在高速通信领域能实现更高的数据传输速率,信号完整性方面表现出色,常用于高速网络通信芯片与 FPGA 的连接。

2、BLVDS

BLVDS(Bus - LVDS) :用于多通道差分信号传输,可在总线上实现高速数据通信。

3、MLVDS

MLVDS(Multipoint - LVDS) :支持多点之间的低电压差分信号传输,适用于多节点数据交互场景。

4、其它

在vivado约束中,还有DIFF_POD10、DIFF_POD10_DCI、DIFF_POD12、DIFF_POD12_DCI、DIFF_SSTL12、DIFF_SSTL12_DCI等等。