文章来源:FPGA技术联盟

1、什么是`timescale指令?

`timescale指令我相信大家应该都不陌生,或多或少都见过,可能绝大部分人都能运用,但其实这个常用指令用起来还是有一些需要注意的。

`timescale是Verilog语法中的一条预编译指令,通常用来指定仿真中时间的单位与精度。

2、`timescale的用法

`timescale包含时间单位和时间精度两部分,设定格式为`timescale timeunit / timeprecision。

timeunit 表示仿真时间单位,而timeprecision则表示仿真时间精度。

例如:`timescale 1ns/1ps 或者 `timescale 1us/1ns 等等。

注意:

时间单位和时间精度只能是1、10和100这3个整数中的某个

单位可以是s、ms、us、ns、ps和fs

时间精度必须小于或等于时间单位

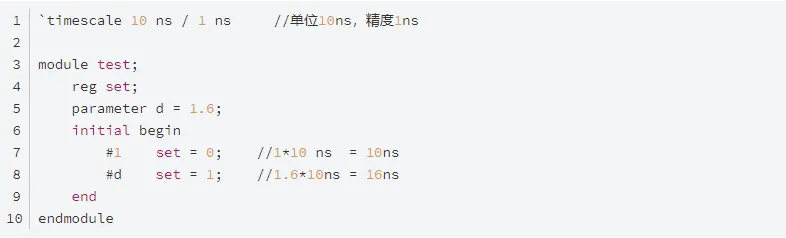

下面看一个简单的例子来了解下`timescale的使用方法:

时间单位设置为10ns,精度设置为1ns

第1次在#1时对set赋值0,此时延时时间为10ns,因为时间单位为10ns,#1表示延时1个时间单位

第2次在#d时对set赋值1,此时延时时间为16+10ns,因为时间单位为10ns,#d表示延时1.6个时间单位,即16ns

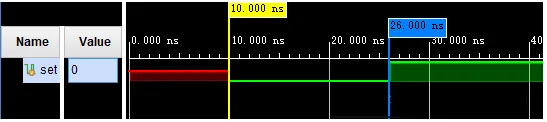

仿真波形图如下:

set未给初值,所以为不定态;在10ns处赋值0,在26ns处赋值1,且测量尺度的最小单位为1ns,即精度1ns。以上均满足推断。

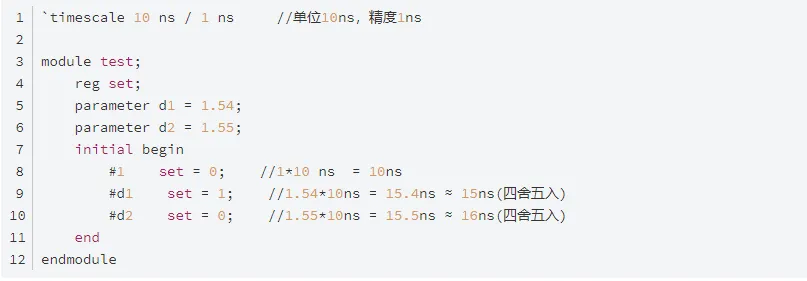

通过上面的例子可以了解时间单位的使用,但是无法看出来时间精度的设置是如何影响延时的,接下来我们把上面的TB代码稍微改一下,如下:

时间单位设置为10ns,精度设置为1ns

第1次在#1时对set赋值0,此时延时时间为10ns,因为时间单位为10ns,#1表示延时1个时间单位

第2次在#d1时对set赋值1,此时延时时间为15+10ns,因为时间单位为10ns,#d1表示延时1.54个时间单位,即15.4ns,因为时间精度为1ns,所以其无法表示15.4ns,就会四舍五入到15ns

第3次在#d2时对set赋值0,此时延时时间为16+15+10ns,因为时间单位为10ns,#d2表示延时1.55个时间单位,即15.5ns,因为时间精度为1ns,所以其无法表示15.5ns,就会四舍五入到16ns

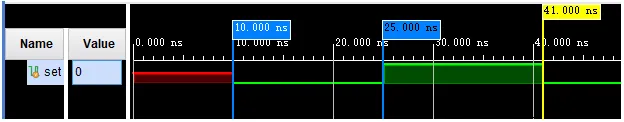

仿真波形图如下:

set未给初值,所以为不定态;在10ns处赋值0,在25ns处赋值1,又在41ns处赋值0,且测量尺度的最小单位为1ns,即精度1ns。以上均满足推断。

3、需要注意的

`timescale指令用起来并不难,但还是有些需要注意的地方。

3.1、不要设置无意义的高精度

时间精度越高,仿真所消耗的资源和时间就越多,根据Clifford E. Cummings的文章《VERILOG CODING STYLES FOR IMPROVED SIMULATION EFFICIENCY》第8节所述,设置`timescale 1ns/1ps消耗的资源是设置`timescale 1ns/1ns的256%,而仿真所消耗的时间则是将近2倍。

我经常看到一些代码上来直接就是`timescale 1ns/1ps,但是仿真过程中其实根据就不需要看到ps级别的结果,完全就是图省事。在RTL不是很大的情况下,其所带来的的影响很难直观察觉出来,但是随着设计的复杂化和大型化,这无疑会成为一个灾难。

所以以后在写TB的时候,不妨问问自己:“你真的需要这么高的精度吗?”

3.2、注意多个`timescale的编译顺序

`timescale是Verilog语法的预编译指令,而预编译指令通常都是顺序执行的,这意味着,一旦`timescale被编译后,则会对其后的所有仿真时间与精度都产生影响,直到遇到了另一条`timescale指令(即上一条指令被覆盖,重新对时间与精度进行预编译)或者`resetall指令(重置所有预编译指令)。

当然了,我还是建议你统一使用一条`timescale指令,以便于工程管理和避免不必要的麻烦。