作者:熊猫君Hello Panda,来源:ZYNQ分享客

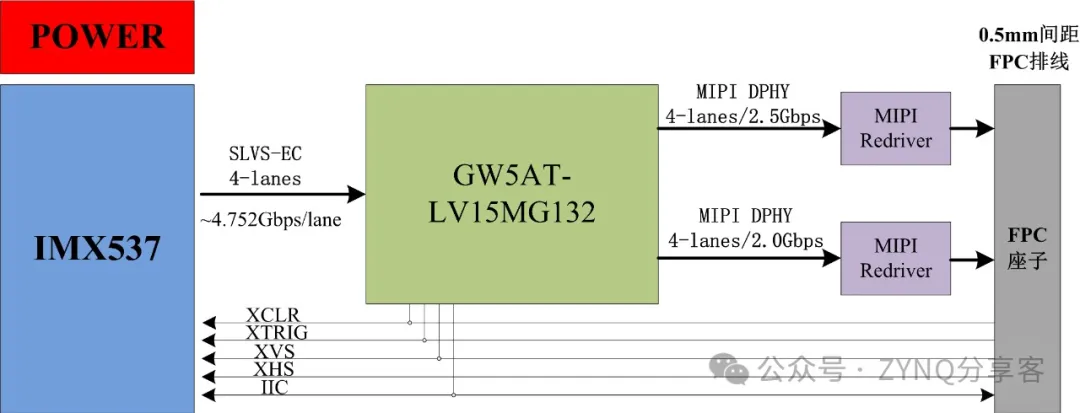

设计一个4Lanes SLVS-EC桥接到2组4lanes MIPI DPHY接口的电路模块:

(1)CMOS芯片:IMX537-AAMJ-C,输出4lanes SLVS-EC 4.752Gbps Lane速率;

(2)FPGA:高云GW5AT-LV15MG132C1/I0;

(3)输出:MIPI D-PHY 4lanes 2.5Gbps一组+MIPI D-PHY 2.0Gbps一组,左右画幅输出;

(4)CMOS板电路尺寸:40mm×43mm,预留CS相机座安装接口;

(5)透传模式,CMOS配置由后端主控完成,只桥数据。

硬件结构如下图2.1所示。

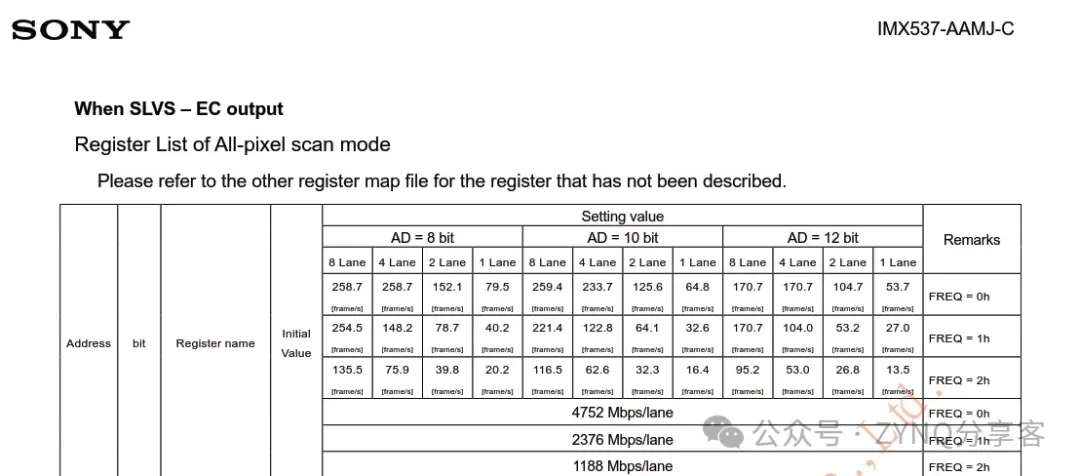

结合IMX537的数据手册(见下图2.2)可知,在设置AD位数为12bit,SLVS-EC工作在4lanes且lane速率为4.752Gbps时可以达到全画幅最大帧率170.7Hz。此时,透传有效数据带宽为2472×2128×12bit×170.7Hz = 10.78Gbps,因此,使用两组MIPI D-PHY完全可以实现无损透传。

同理,可以计算得到AD位数为10bit时,也可以实现透传设计目标。

硬件设计镜头座安装位,镜头采用CS口标准镜头。

电路板对外为42Pin FPC排线,其线序定义如下表2.1所示。

FPGA软件基于Gowin FPGA Design Version V1.9.10.02或更新版本开发,实现主要功能如下:

(1)SLVS-EC数据采集;

(2)左右画幅拆分;

(3)MIPI D-PHY数据发送。

FPGA软件的框架如下图3.1所示。

图3.1 FPGA软件设计框图

如上图所示,SLVS-EC接收以后分成左右画幅(video splite模块)以MIPI CSI-2的链路格式发给物理层IP,链路层IP再发给D-PHY物理层并串转换从IO上输出。

FPGA全速率运行时,整板设计功耗3W(包括电源效率损耗、CMOS芯片和FPGA芯片耗电)。

四、其它

(1)电路设计为透传模式,FPGA不关系主控如何配置CMOS芯片的帧率、分辨率、AD位数等信息,只将SLVS-EC接口输入的视频数据流桥接为MIPI即可;

(2)因使用GW5AT-15的FPGA资源利用率很高,已经无法添加其它的数据流处理相关的功能模块;

(3)同等功能可通过Lattice Crosslink-NX系列的LIFCL-40-7MG289I实现,可以真正实现4-Lanes SLVS-EC 4.752Gbps(总带宽约19Gbps)到2组4-Lanes

MIPI D-PHY的转换(总带宽20Gbps);

(4)对一些超大分辨率或超高帧率的图像传感器芯片,必须使用8-lanes的SLVS-EC Spec2.0方可达到最高其设计最高性能的,桥接方案已经非常不经济且需要桥接为至少是PCIe Gen3×4(或PCIe Gen4×4),应为PCIe是基于地址映射直接对内存访问,由于存在同时的读和写操作,至少需要一组DDR4-1600 64bit位宽的DDR,而且还会带来额外延迟。此类桥接方案建议选用Xilinx Artix UltraScale+系列的器件。

今天的方案分享到此结束,大家有好的想法可以联系熊猫君共同讨论、实施,让技术的明天更好。