作者:FPGA技术实战

引言:本文介绍PCIe IP核时钟结构、PCIe板卡时钟方案及复位设计相关内容。

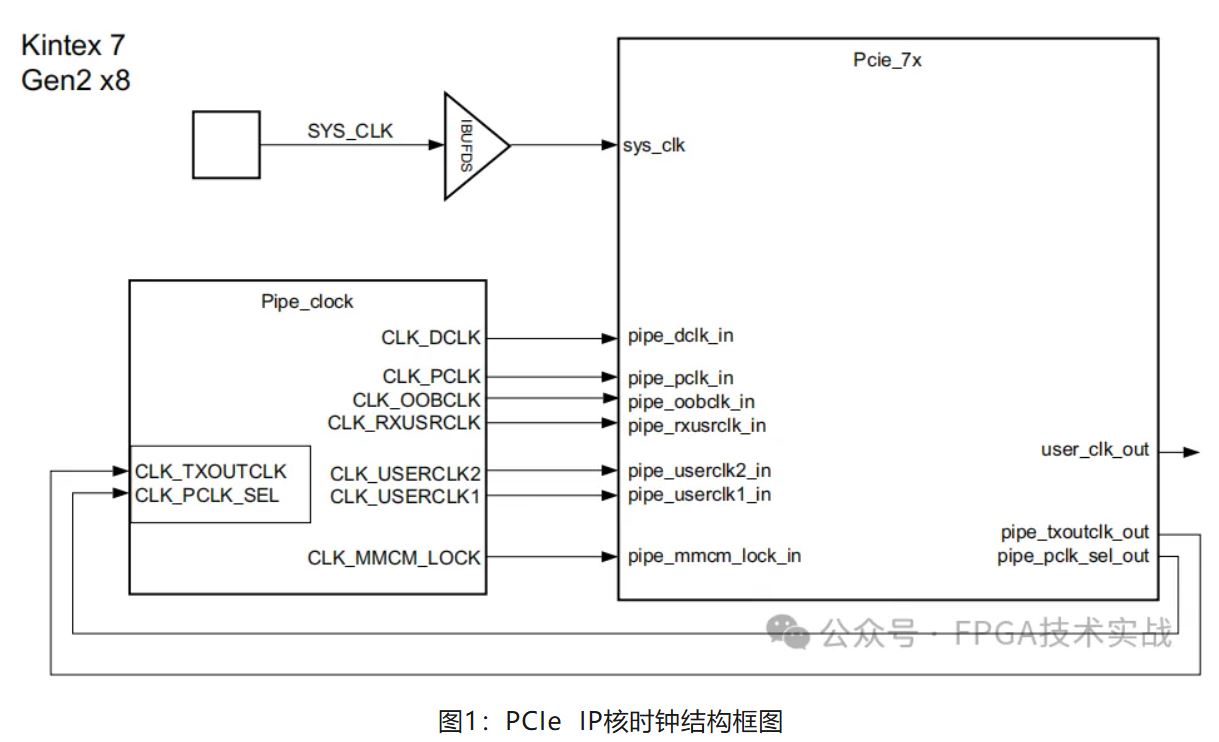

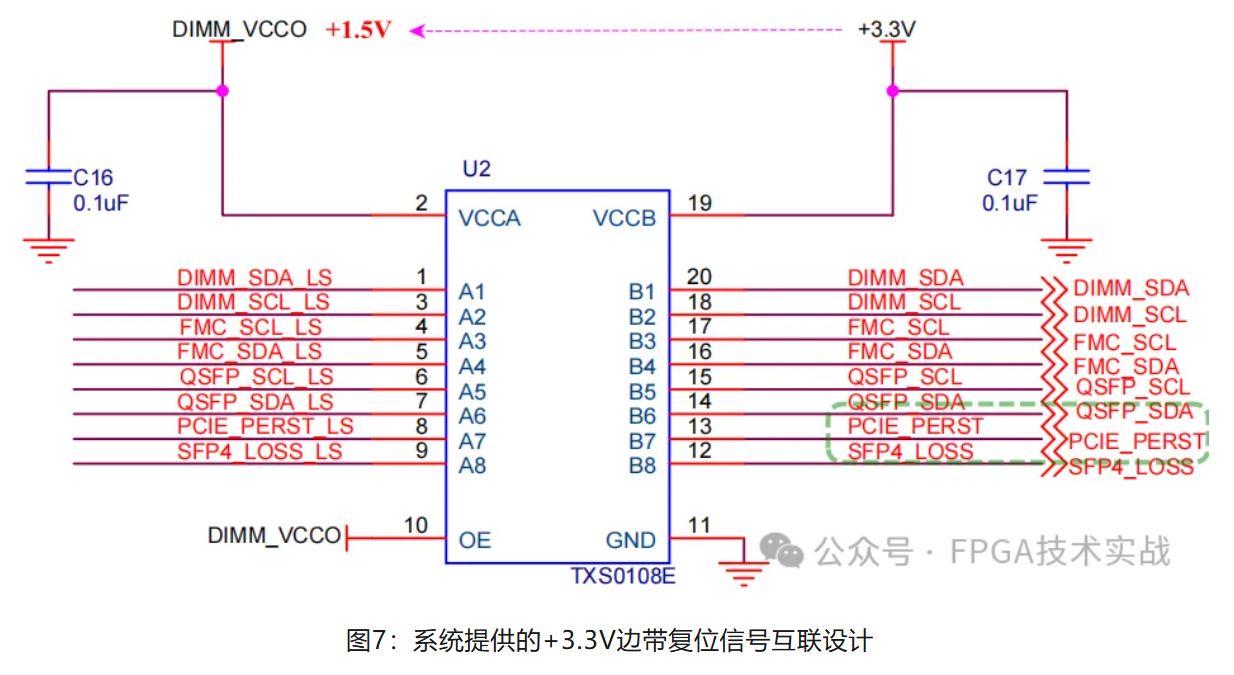

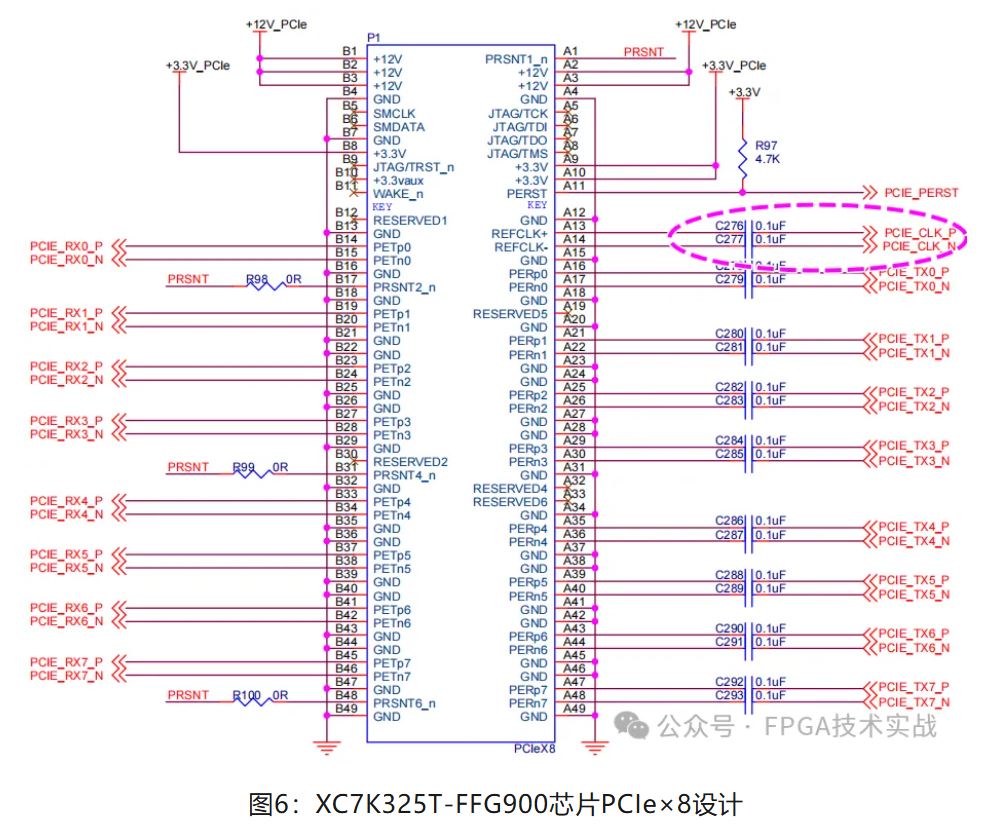

图1以 Kintex 7 Gen2×8为例,显示了PCIe集成块时钟结构框图。

集成块输入系统时钟信号称为sys_clk,该时钟频率必须为100MHz、125MHz或250MHz。使用的时钟频率必须与Vivado IDE中的时钟频率选择相匹配。

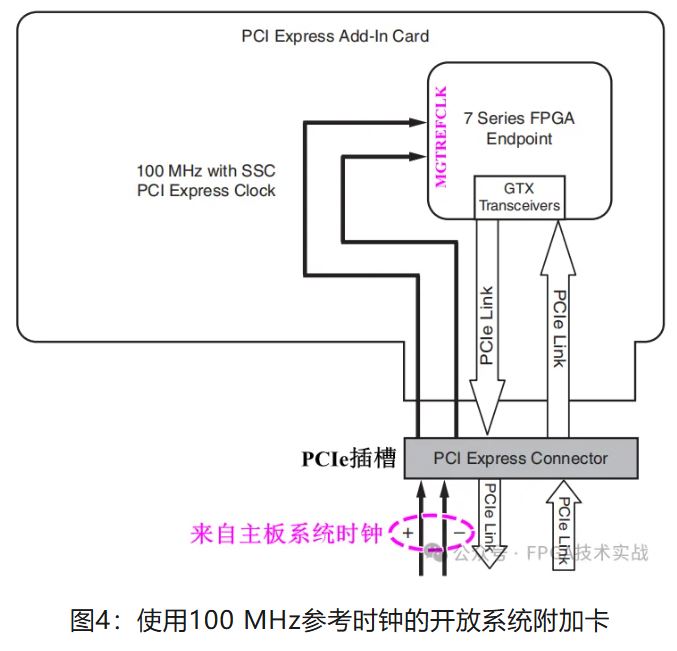

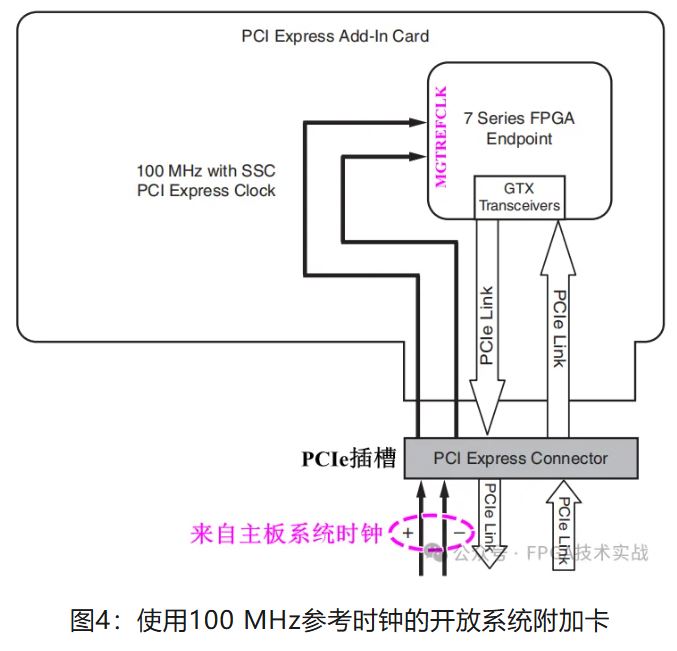

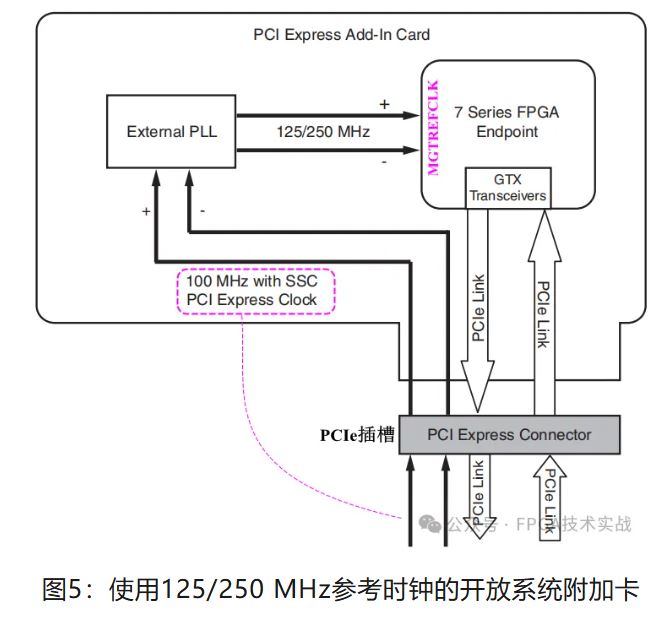

有两种方法可以为PCI Express系统提供时钟: 建议:推荐使用核心时使用同步时钟。由于所提供的参考时钟的特性,所有附加卡设计都必须使用同步时钟。对于使用插槽时钟的设备,必须在Vivado IDE中启用链路状态寄存器中的插槽时钟配置设置。

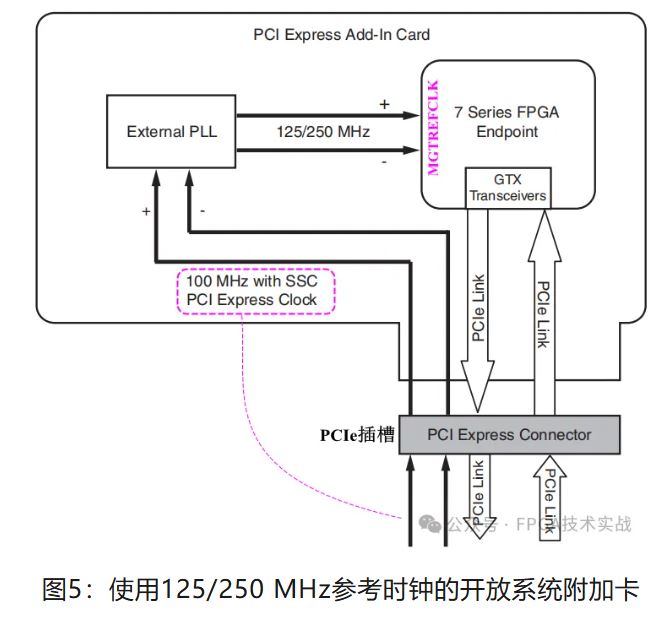

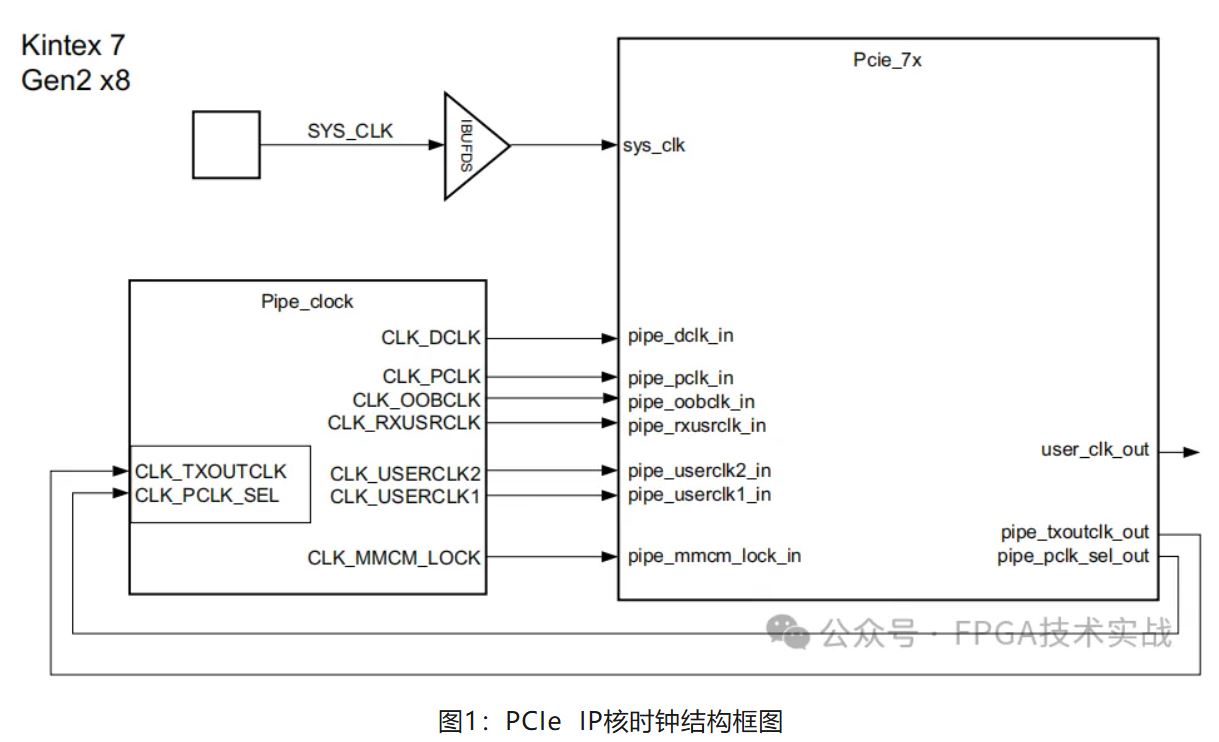

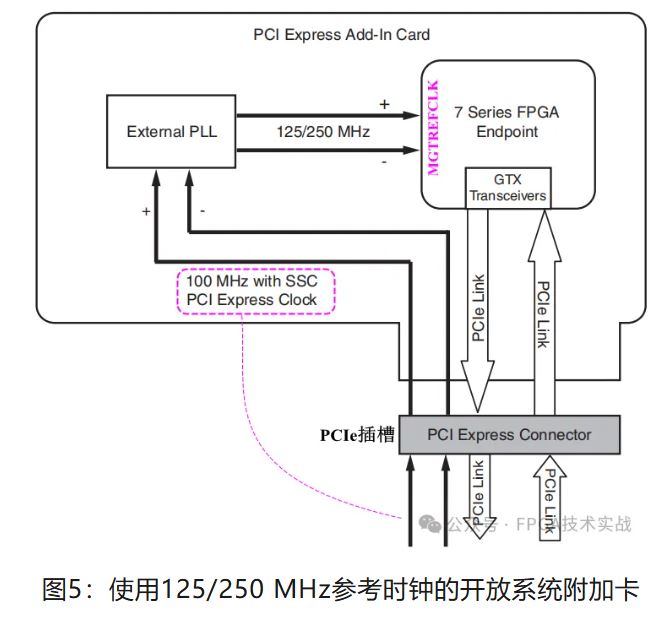

对于同步时钟系统,每个链路伙伴设备共享相同的时钟源。图2和图3显示了使用100MHz参考时钟的嵌入式系统。当使用125MHz或250MHz参考时钟选项时,必须使用外部PLL进行5/4和5/2的乘法,将100MHz时钟分别转换为125 MHz和250 MHz。此外,即使设备是嵌入式系统的一部分,如果系统使用商用PCIe根复合体或交换机以及典型的主板时钟方案,仍应使用同步时钟。

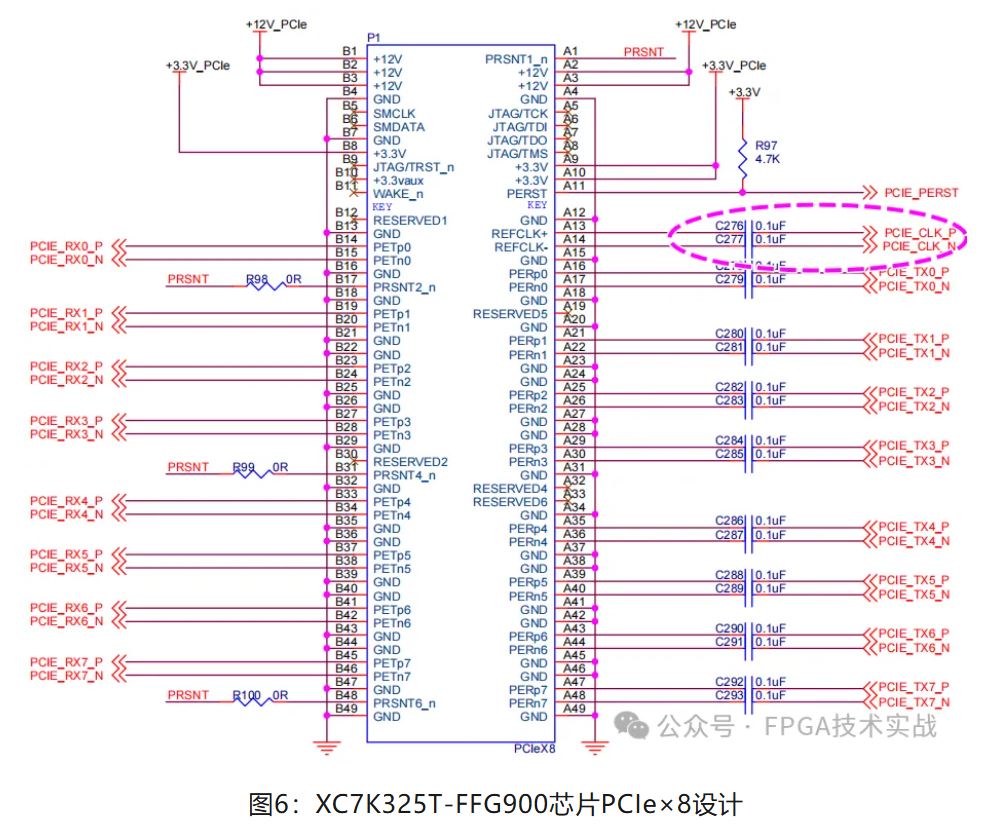

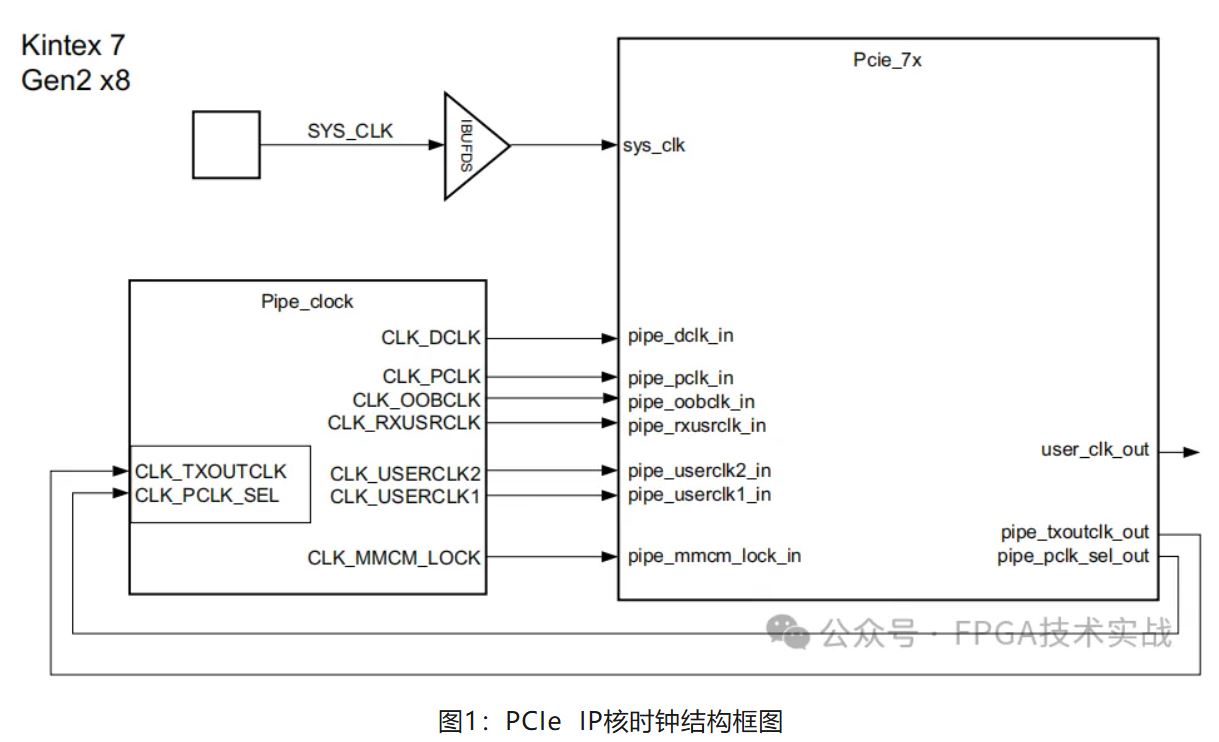

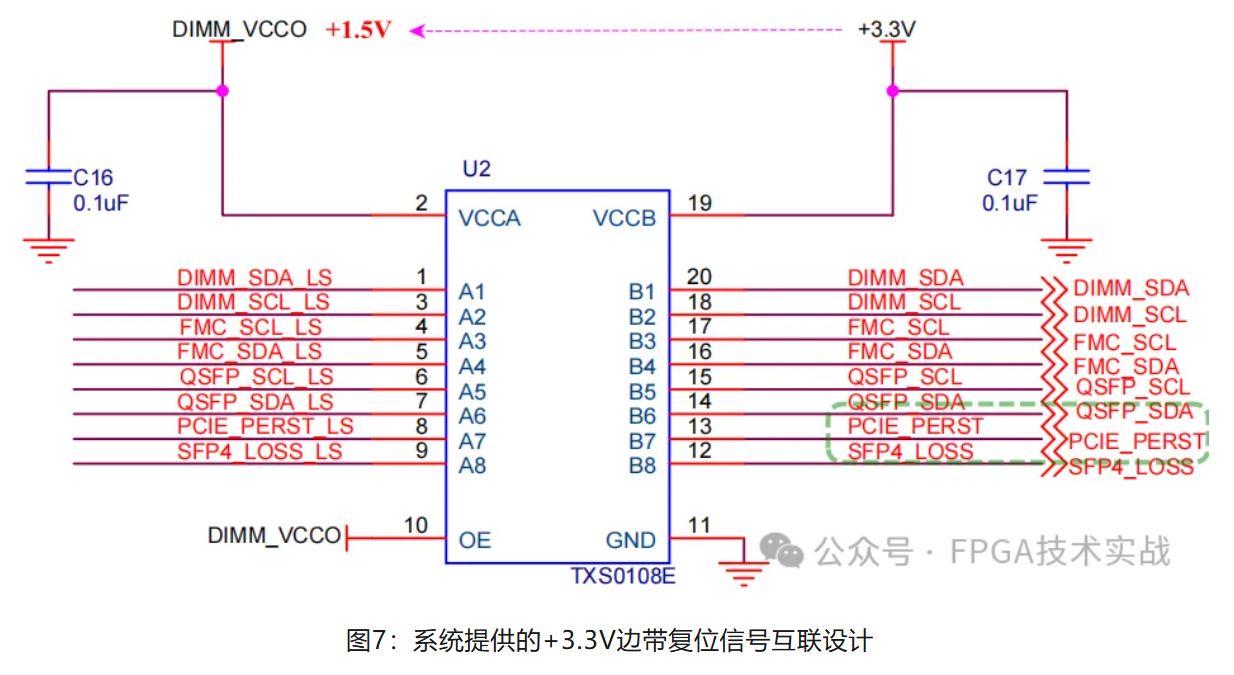

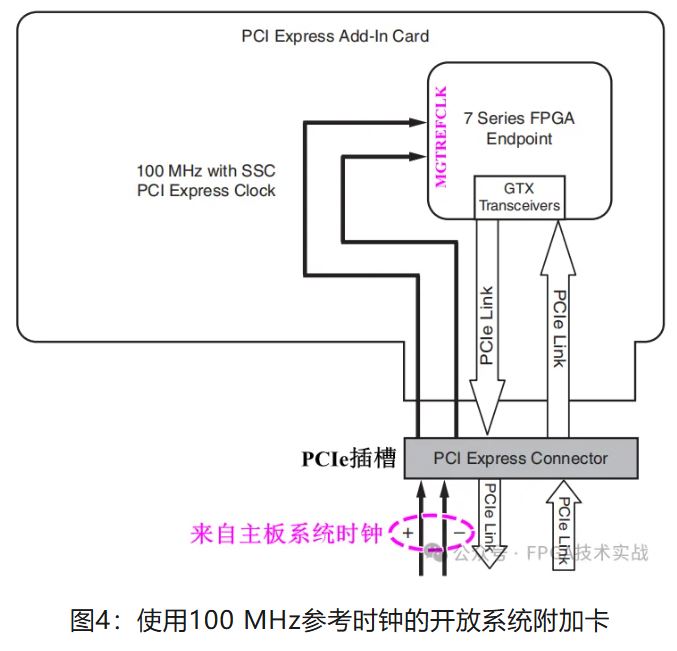

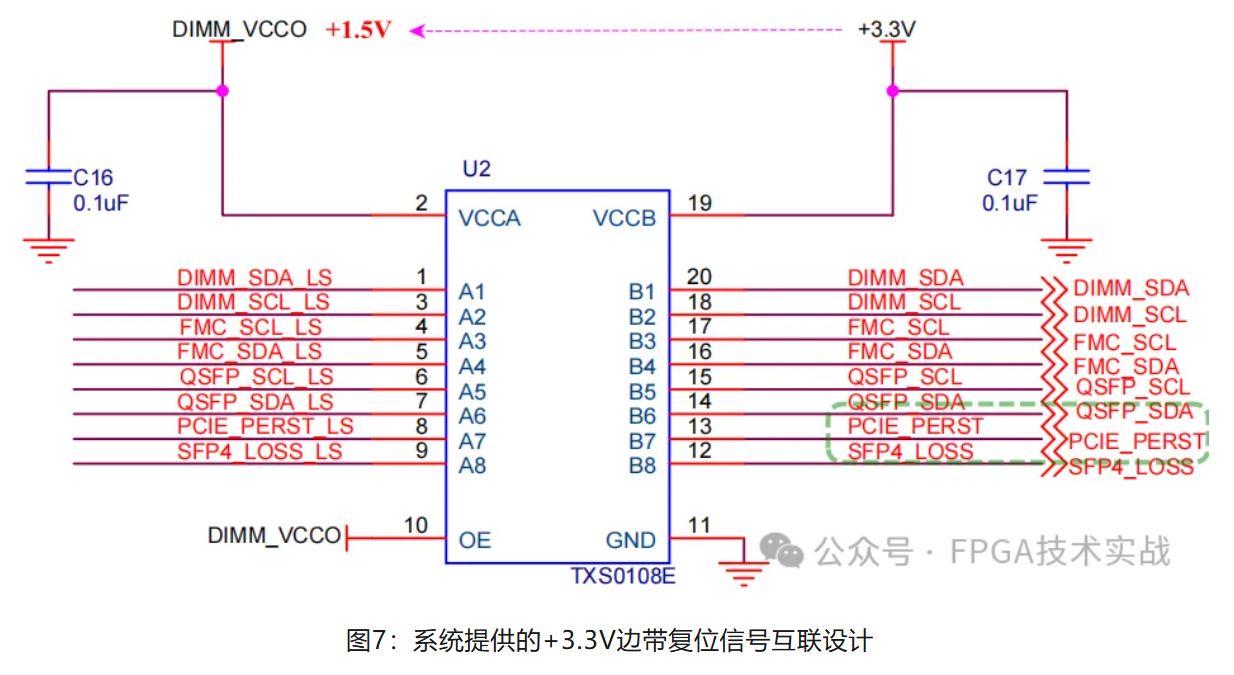

PCIe IP核使用sys_rst_n复位系统,它是异步、低有效复位信号。插入此信号会导致整个IP核(包括GTX收发器)的硬复位。复位解除后,IP核试图连接训练并恢复正常运行。在典型的端点应用程序中,例如附加卡,通常存在边带(sideband)复位信号,应将其连接到sys_rst_n。对于没有边带系统复位信号的端点应用,应在本地生成初始硬件复位。PCI Express中可能发生三个重置事件:●冷复位(cold reset):在通电时发生的上电复位,信号sys_rst_n被插入会导致IP核的冷复位; ●热复位(warm reset):由硬件触发的基本复位,无需移除和重新施加电源。sys_rst_n信号被插入以导致内核的热复位; ●热复位(hot reset):通过协议在PCIe链路上带内发送复位,在这种情况下,不使用sys_rst_n。在该复位的情况下,接收到的_Hot_Reset信号被断言以指示复位的来源。IP核的用户应用程序界面有一个名为user_reset_out的输出信号。此信号相对于user_clk_out同步停用。信号user_reset_out在以下任何一种情况下都会被断言: ●基本复位:由于sys_rst_n的断言而发生(冷或热); ●IP核内的PLL:失锁,表明时钟输入的稳定性存在问题;●收发器PLL锁定丢失:任何收发器都失去锁定,表明PCIe链路存在问题。 在上述所有条件得到解决后,user_reset_out信号与user_clk_out同步解除,允许IP核尝试训练并恢复正常运行。需要注意的是:根据PCIe电气规范设计的系统提供边带复位信号使用3.3V信号电平,当该信号接入FPGA IO接口时,要考虑电平兼容性问题,如图7所示,显示了来自系统提供的+3.3V边带复位信号PCIE_PERST与FPGA DDR Bank互联时,需将电平转换为+1.5V。

文章来源:FPGA技术实战