文章来源:OpenFPGA

FPGA 开发的目标是按时、按质交付项目。

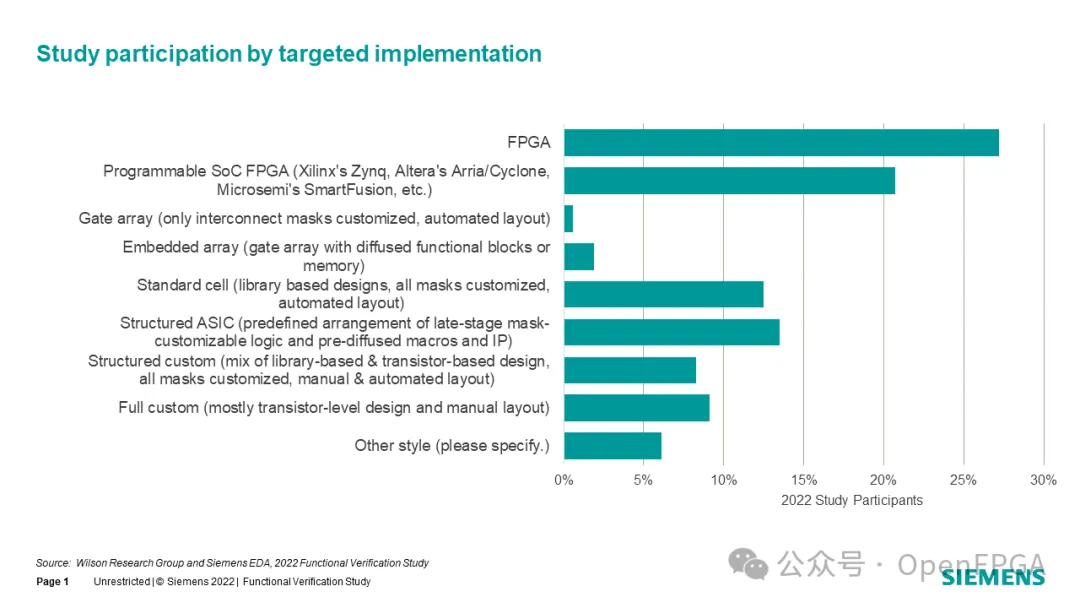

然而,这一目标说起来简单,实现起来老费劲了。根据业内最广泛的调查之一,西门子威尔逊集团 2022 年的调查(https://blogs.sw.siemens.com/verificationhorizons/2022/10/10/prologue-th...),70% 的 FPGA 项目落后于计划,12% 的项目落后计划 50% 以上。

为此,很多FPGA厂商都在自己EDA工具里嵌入IP减少FPGA项目的开发周期,使用 IP 是一种有助于实现按时、高质量且经济高效的项目交付的方法。

我们现在处于一个比较好的时期,例如,Vivado 2024.1 提供了 681 个 IP,使用这些IP可以快速的搭建FPGA系统,比如XDMA IP可以快速搭建基于PCIe的应用。当然,这些 IP 核的适用性取决于目标设备系列和设备的所需功能。

利用这些 IP 模块可以加快开发速度,并通过利用经过验证的组件降低技术风险。此外,这些 IP 核通常附带示例和测试平台,这有助于我们了解它们的操作和用法。

然而,这些IP并不能提供我们设计中需要的所有功能。在这种情况下,我们可能需要开发定制解决方案、购买第三方 IP 或使用开源IP库。

接下来,我们介绍几个高质量开源库来支持我们的设计:

FPGA_Library

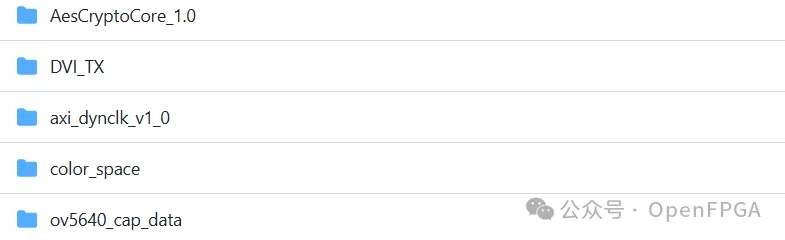

https://github.com/suisuisi/FPGA_Library

该库包含诸多IP,包括图像处理、数字信号处理、接口等。

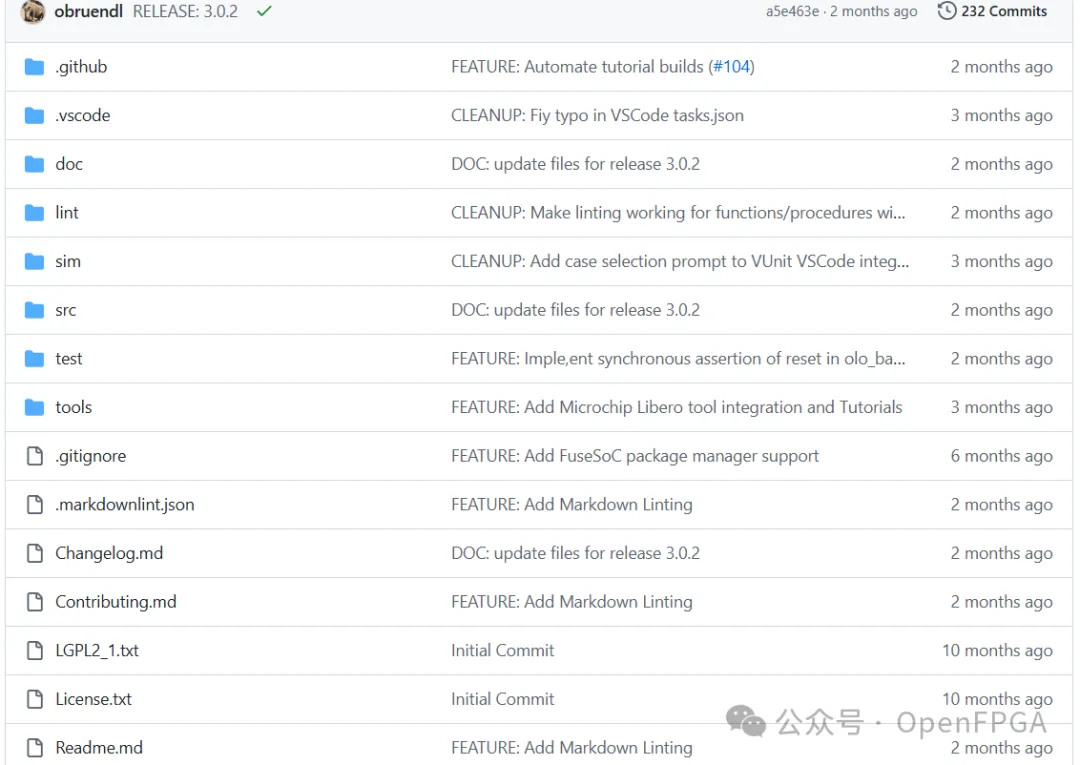

Open Logic

https://github.com/open-logic/open-logic

这个开源 VHDL 库提供了各种专注于 IP 外设创建的 IP 核。它提供了用于CDC、内存、FIFO、仲裁器、时分复用和其他功能(如 PRBS、延迟和桶形移位器)的模块。对于 AXI 支持,Open Logic 包括 AXI 主设备、从设备和流水线。它还提供用于 UART、SPI、I2C 等的接口 IP,使其成为 AXI 端点的宝贵资源。

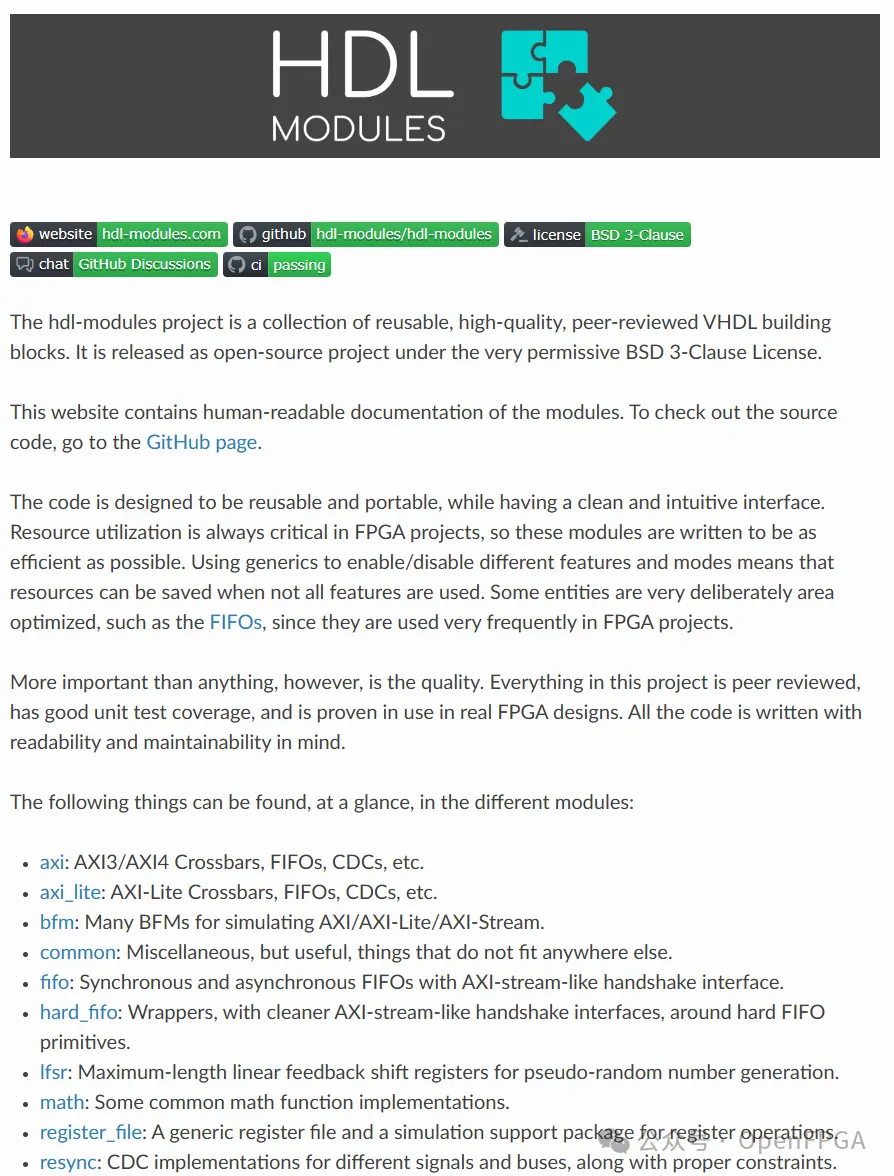

HDL 模块

https://hdl-modules.com/index.html

该库提供一系列 AXI IP,包括interconnects 和 crossbars,以及 FIFO 等基本基础设施。为了支持仿真,HDL 模块还包括总线功能模型和通用组件,例如环形缓冲区、LFSR、数学函数和正弦发生器。通过阅读文档可以很好地了解它。

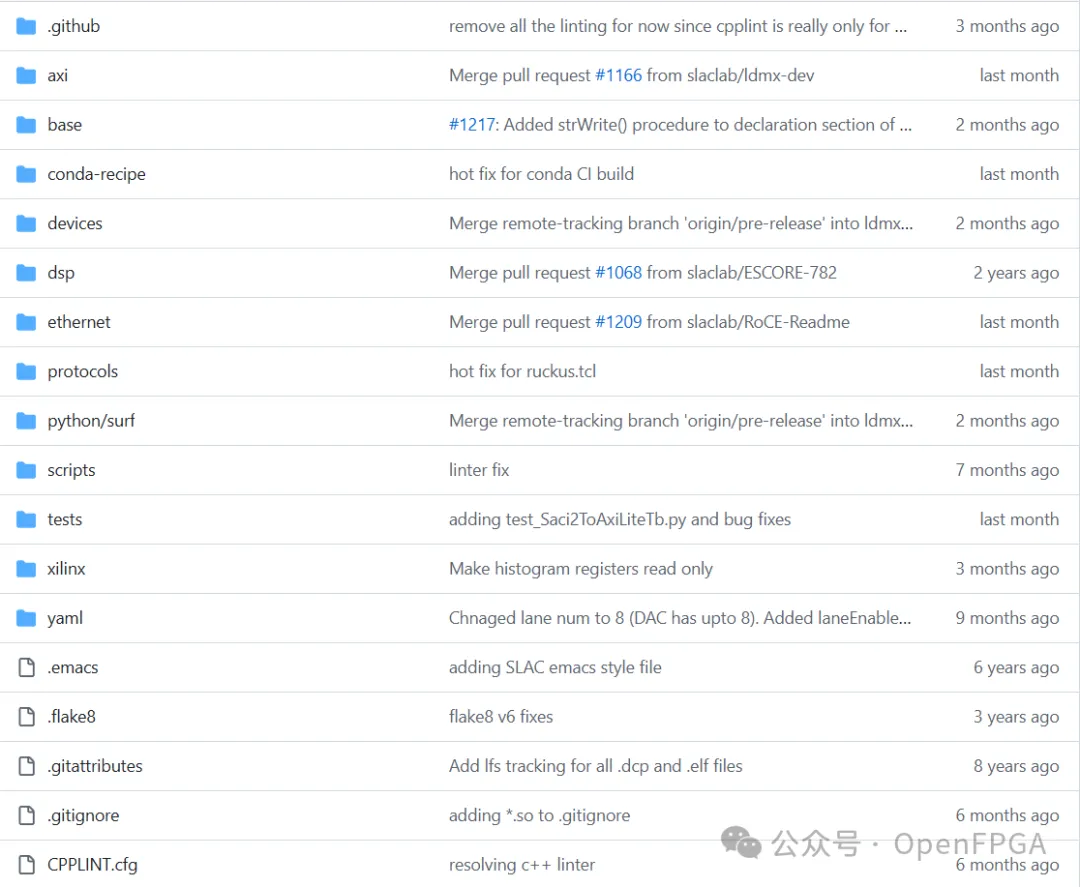

SURF(SLAC 终极 RTL 框架):

https://github.com/slaclab/surf

SURF 提供 AXI、以太网和设备库。设备库特别有用,带有 ADC 和 DAC 等外围设备的驱动程序。SURF 使用 CocoTB 和 GHDL 进行验证,使流程变得简单。

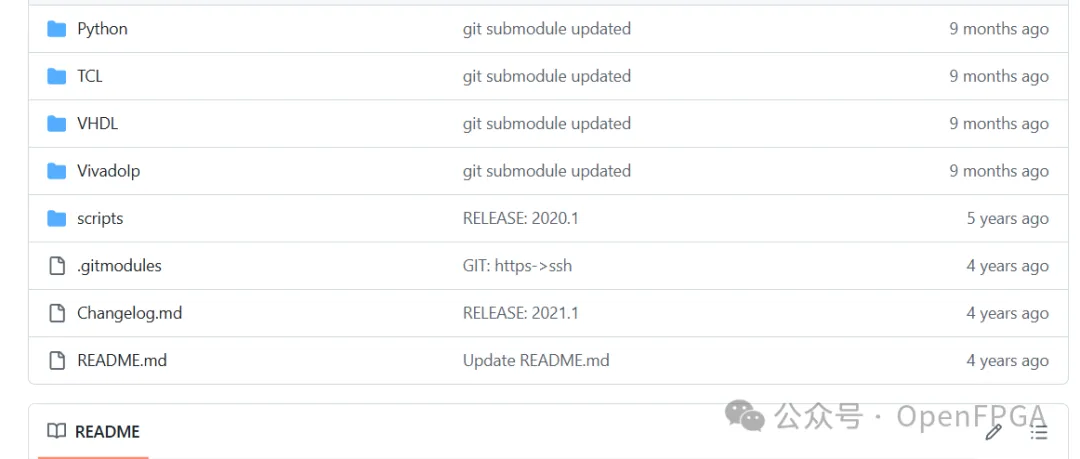

PSI Lib

https://github.com/paulscherrerinstitute/psi_fpga_all

由 Paul Scherrer 研究所开发,该库提供内存、FIFO、跨时钟域、时分复用、AXI 接口和其他常见模块的 IP 模块。

PoC Lib(Pile of Cores)

https://github.com/VLSI-EDA/PoC

由Technical University of Dresden大学提供,PoC 专注于内存、FIFO 和 I/O 控制器。它利用了 CocoTB、OSVVM、UVVM 和 VUnit 进行验证。

以上这些只是一些常用的库,可以结合之前推荐的开源库一起使用:

这些开源库可以帮助开发解决方案,而无需从头开始。其中许多库与 Vivado 完美集成,简化了它们的使用。

当然,这些库并不权威,需要结合使用场景进行修改和优化。

最后要注意的是:使用这些开源库时,请确保阅读、理解并遵守其开源许可证,以避免潜在的麻烦。