版权声明:本文为CSDN博主「巨大八爪鱼」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/ZLK1214/article/details/113201726

阅读本文前,请先阅读:

(1)【教程】Xilinx Vivado/Vitis 2020.1创建最简单的MicroBlaze工程运行Hello World C语言程序(不使用外部DDR3内存),并固化到SPI Flash

https://blog.csdn.net/ZLK1214/article/details/111824576

(2)Xilinx 2020.1 MIG核读写DDR3内存,新建工程时配置MIG核的完整步骤

https://blog.csdn.net/ZLK1214/article/details/111349678

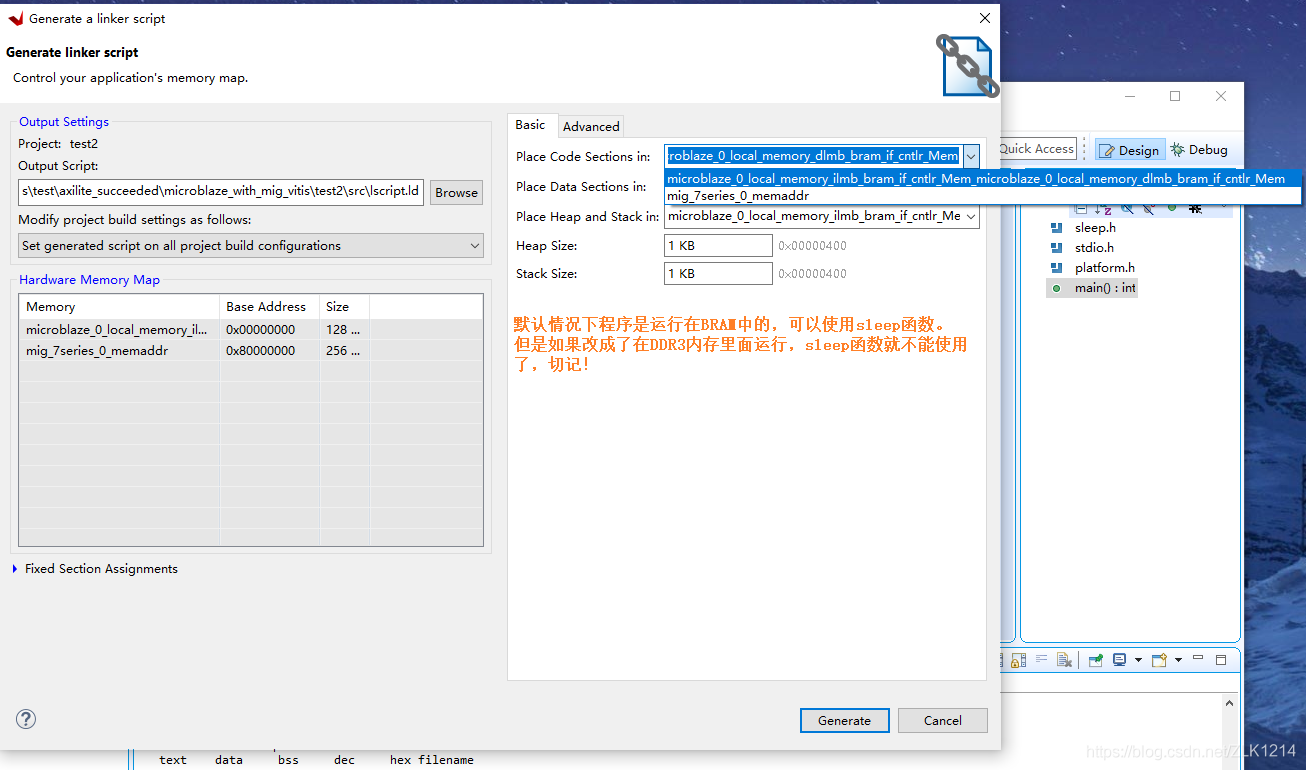

添加了DDR3内存以后,程序既可以运行在BRAM里面,也可以运行在DDR3内存里面。但如果运行在DDR3内存里面,固化起来会比较麻烦,需要借助SREC SPI Bootloader。

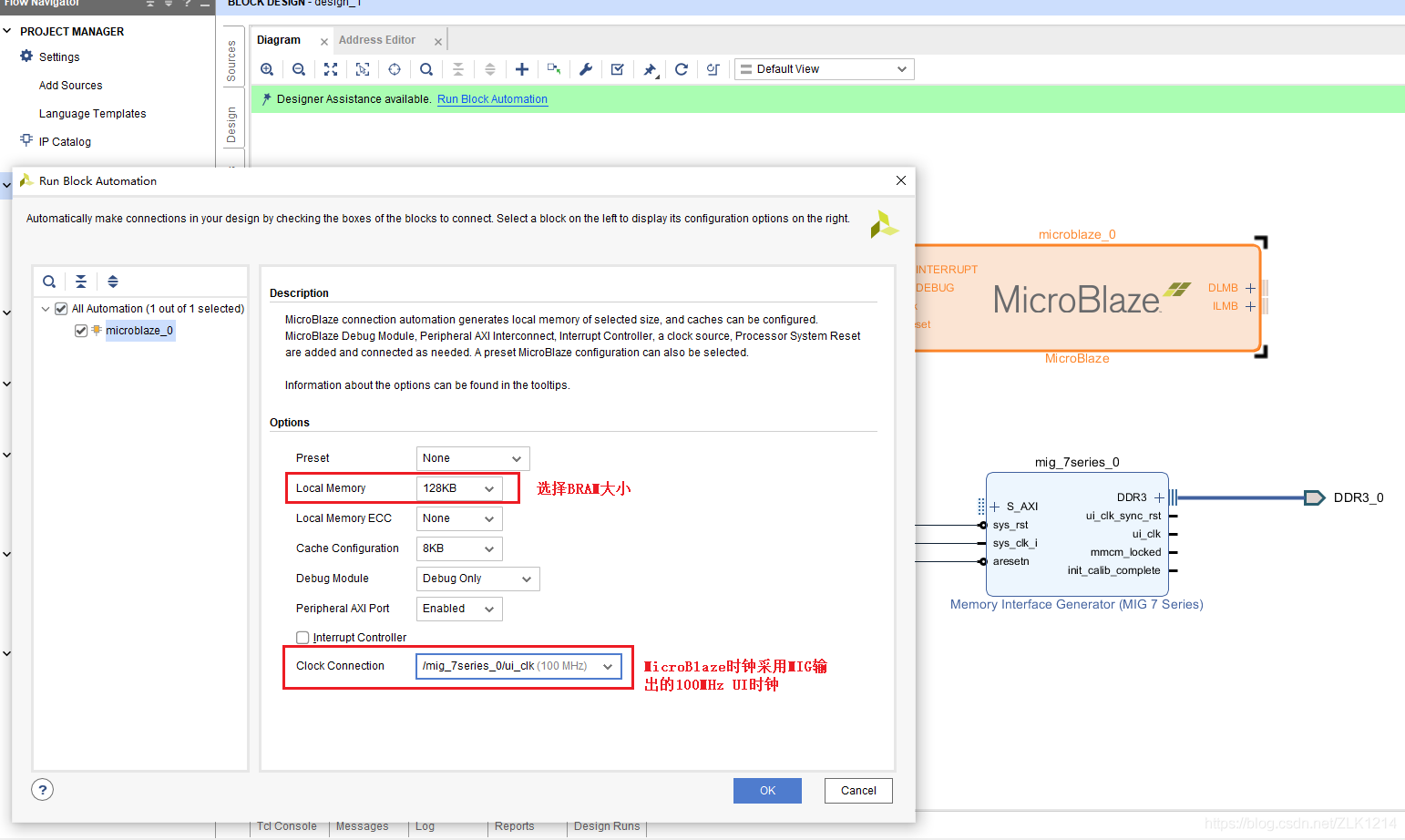

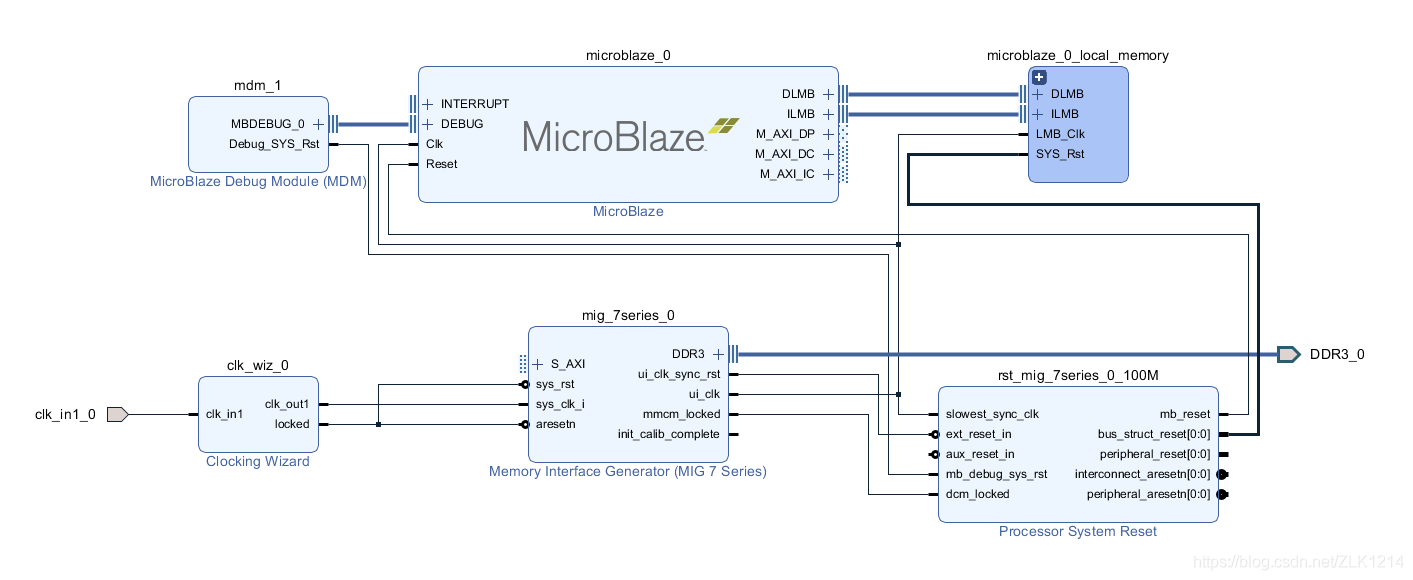

建立带DDR3内存的MicroBlaze工程的方法很简单:以不带DDR3的工程(1)为基础,只需要在Clocking Wizard和Processor System Reset之间插入一个MIG IP核就可以了。

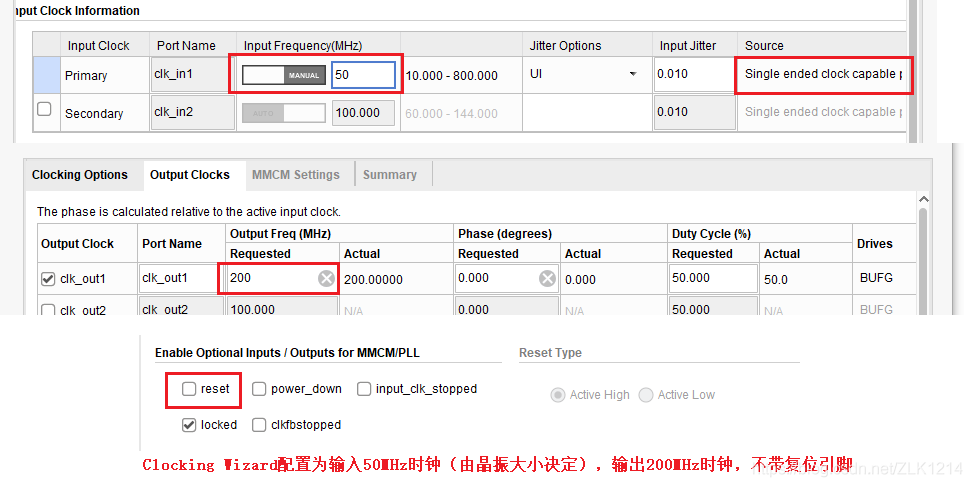

原本,Clocking Wizard输出的时钟是100MHz,是直接接到Processor System Reset上的。

修改后,两者中间插入了一个MIG。Clocking Wizard的时钟输出变成了200MHz,给MIG提供时钟。在MIG的内部由PLL倍频到400MHz驱动外部DDR3内存,然后再分频到100MHz从ui_clk引脚输出出来,给Processor System Reset提供时钟。

修改后,MicroBlaze的运行频率没有变,仍然是100MHz。

建立工程的时候一定要小心使用Vivado的自动连线的功能,操作不当的话很容易产生两个Processor System Reset。

下面详细说明一下工程的建立步骤。

首先在空白Block Design里面添加Clocking Wizard和MIG IP核:

修改Clocking Wizard的配置:

MIG的详细配置请参考上面的文章(2),关键配置单独挑出来说明一下:

现在可以添加MicroBlaze核了,添加后点击Run Block Automation,请注意时钟的选择:

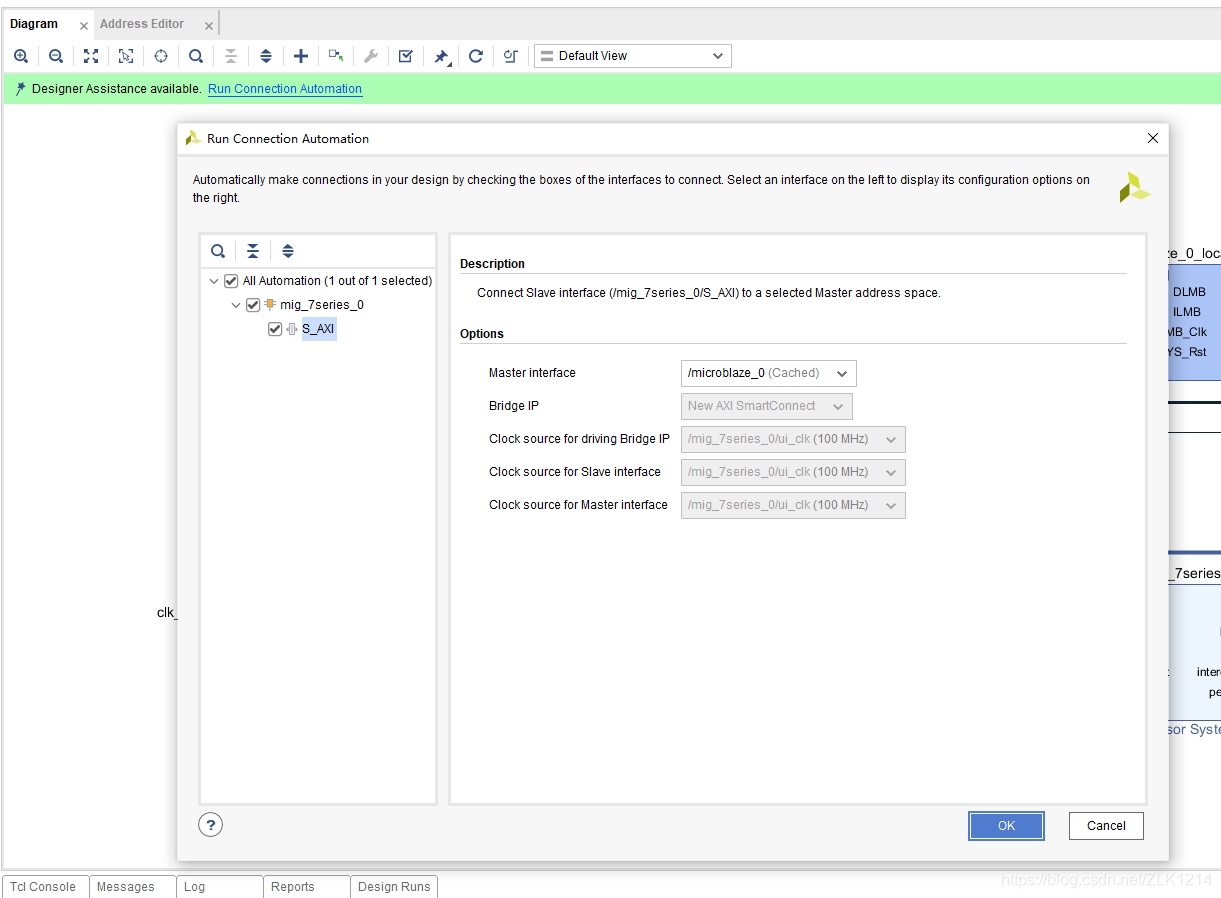

点击Run Connection Automation,通过一个新建的AXI SmartConnect将MIG的S_AXI和MicroBlaze连接起来:

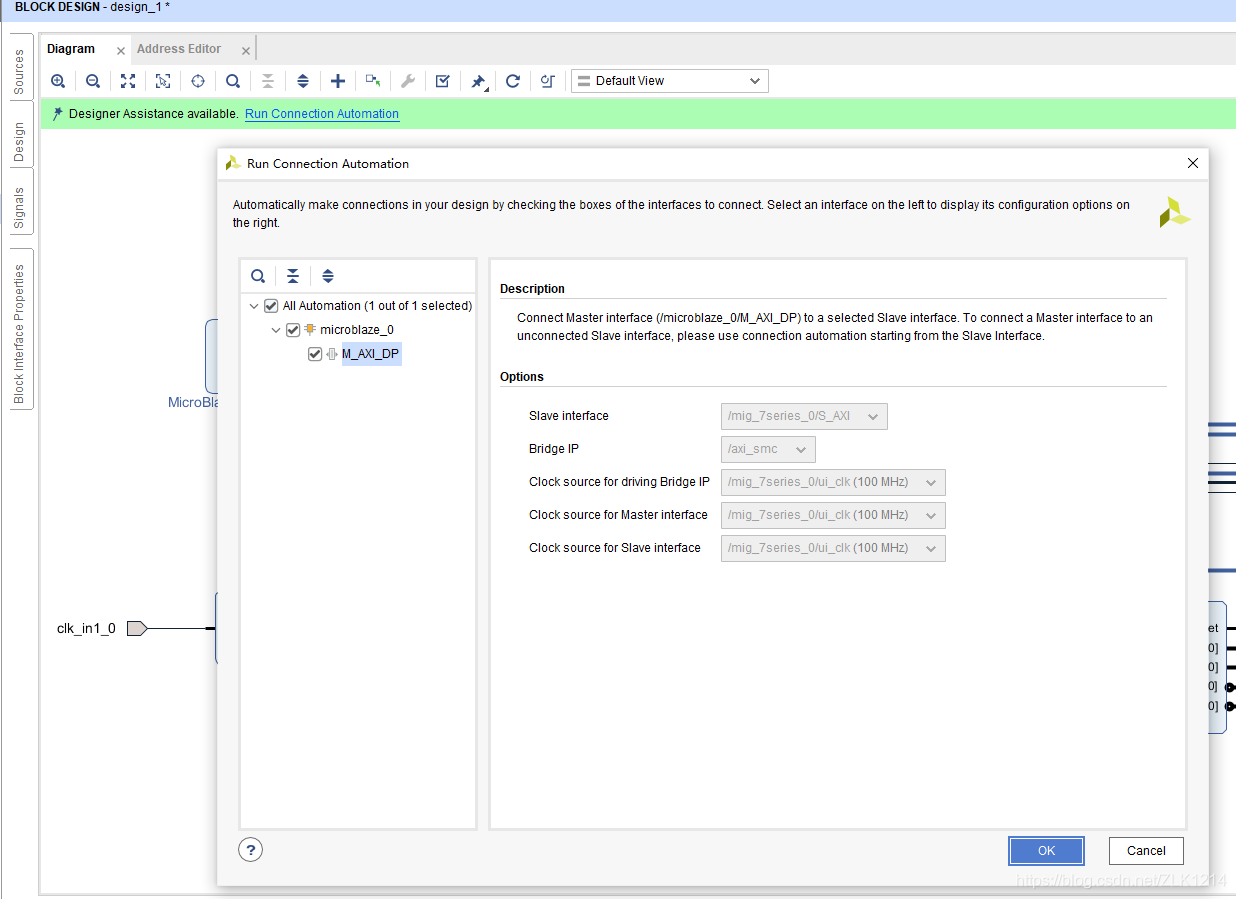

自动连接剩余的接口:

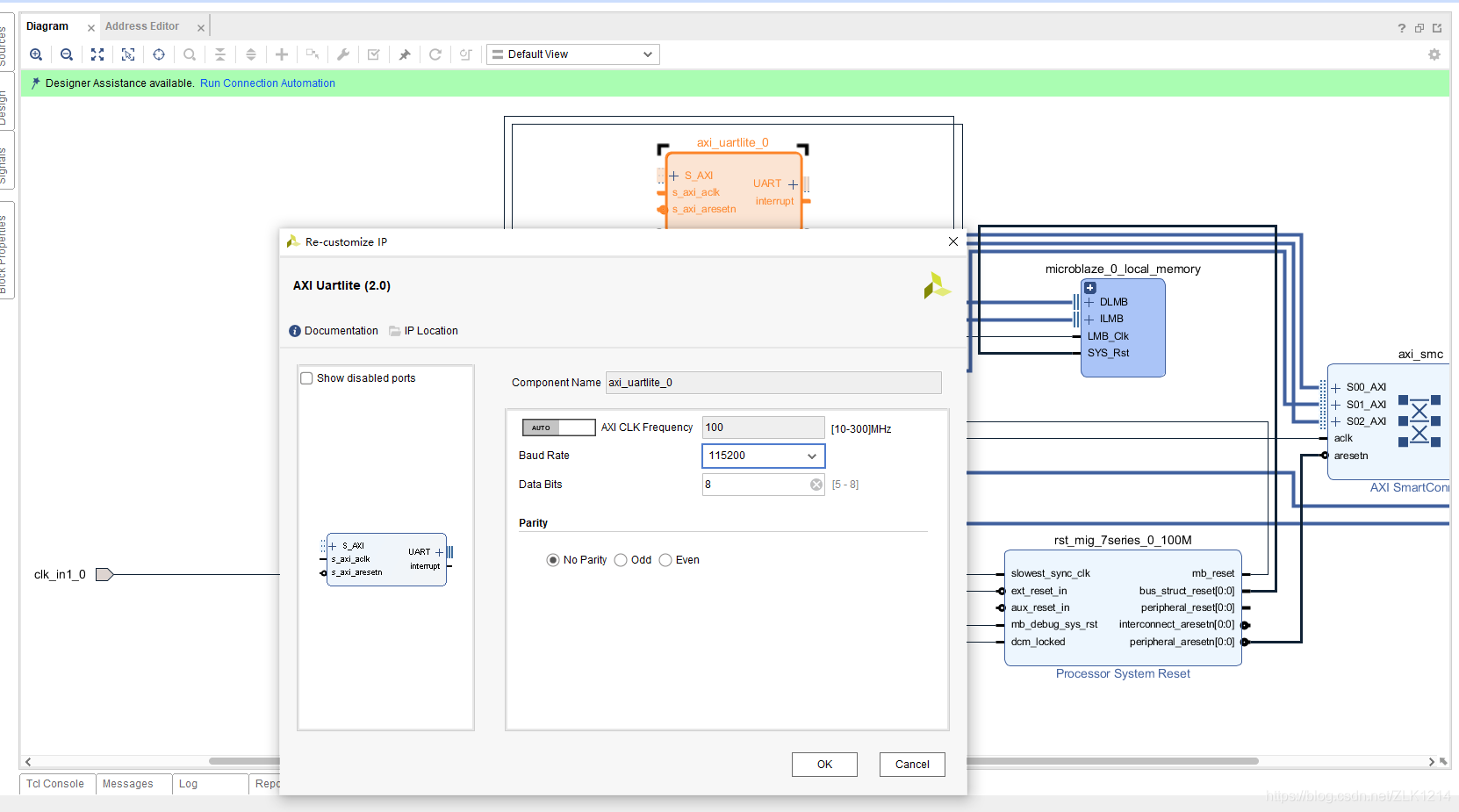

添加AXI Uartlite串口,用于printf打印:

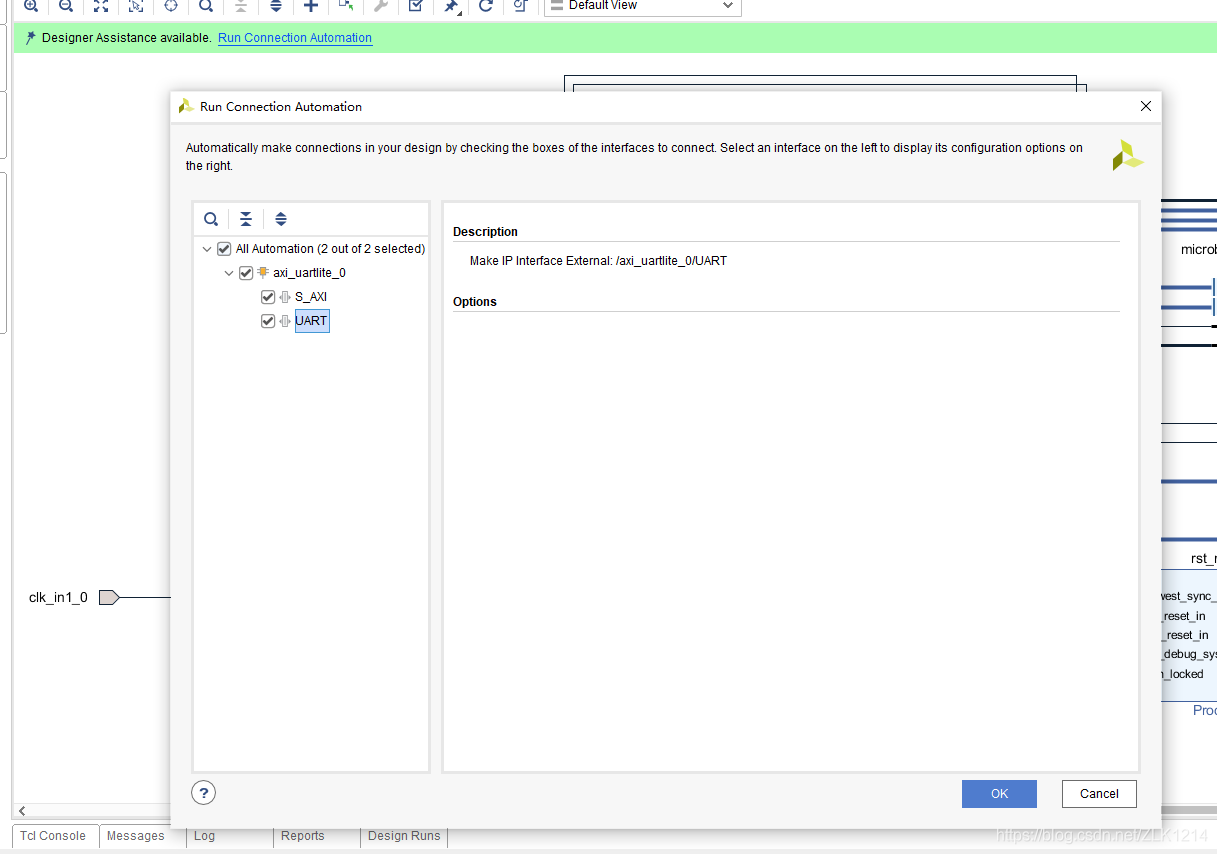

Run Connection Automation,将Uartlite与MicroBlaze连在一起:

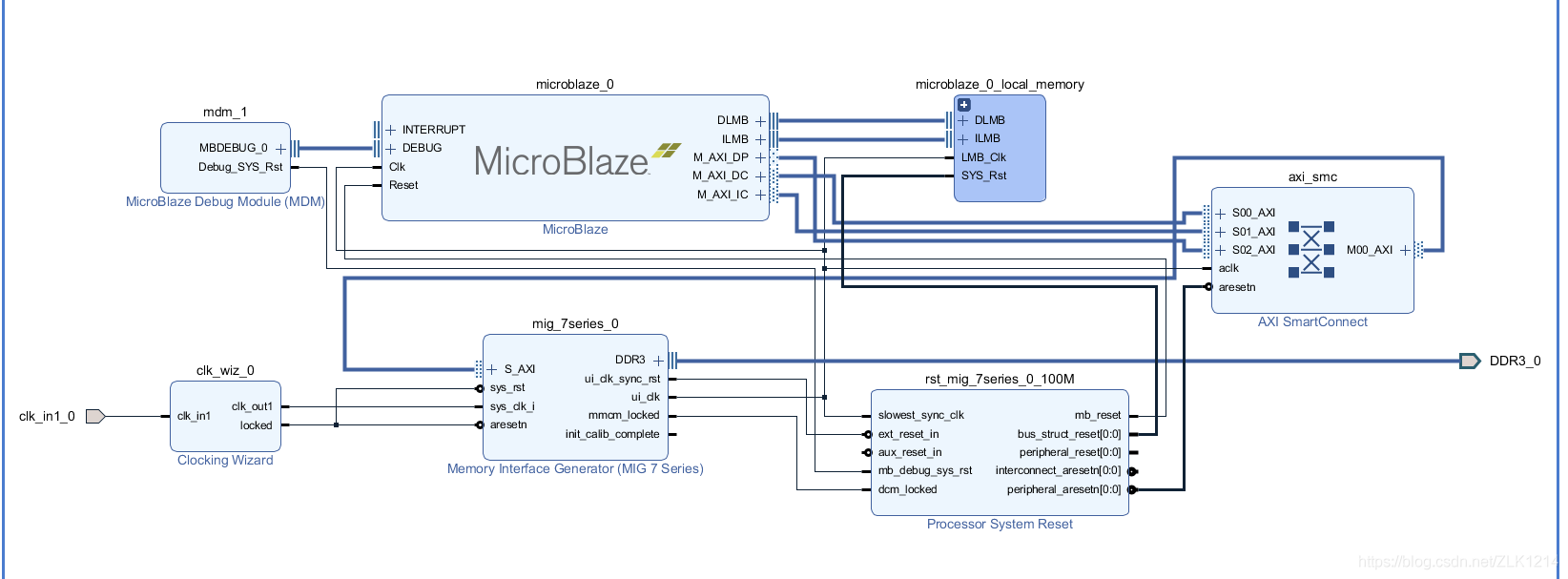

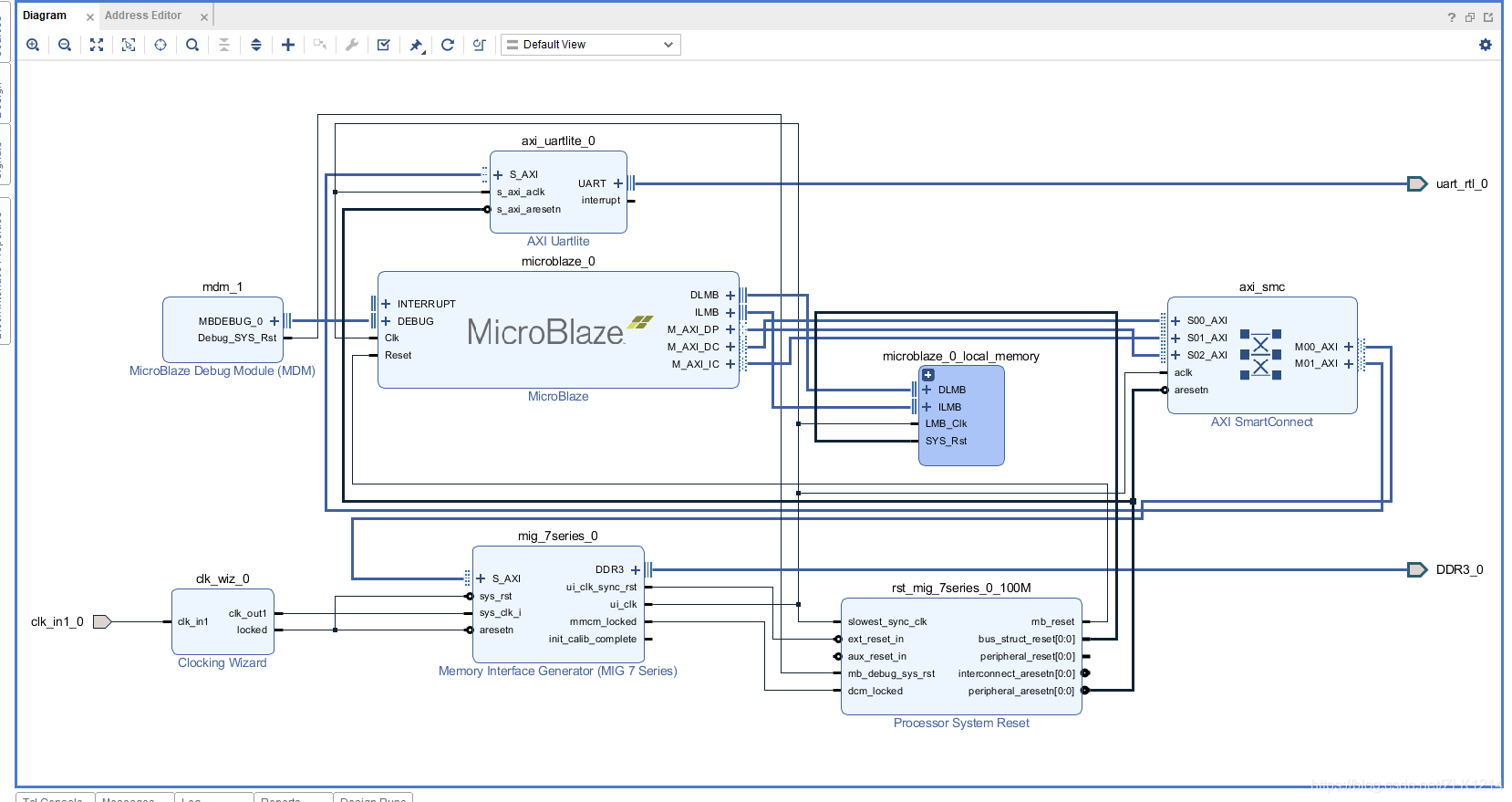

最终连线结果:

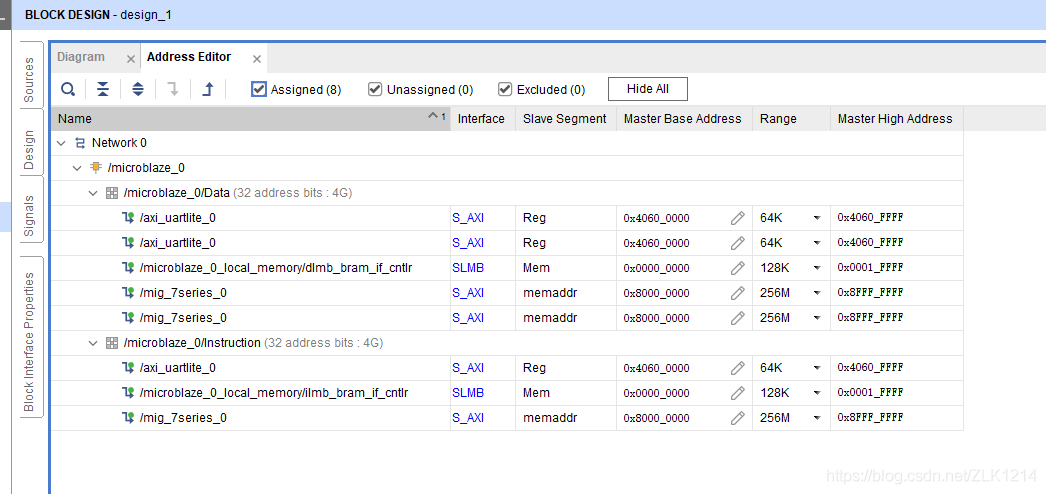

地址分配:

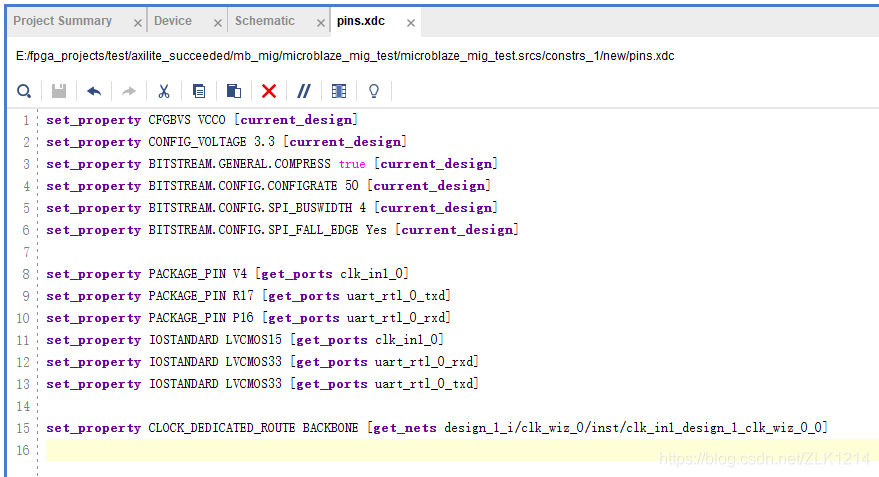

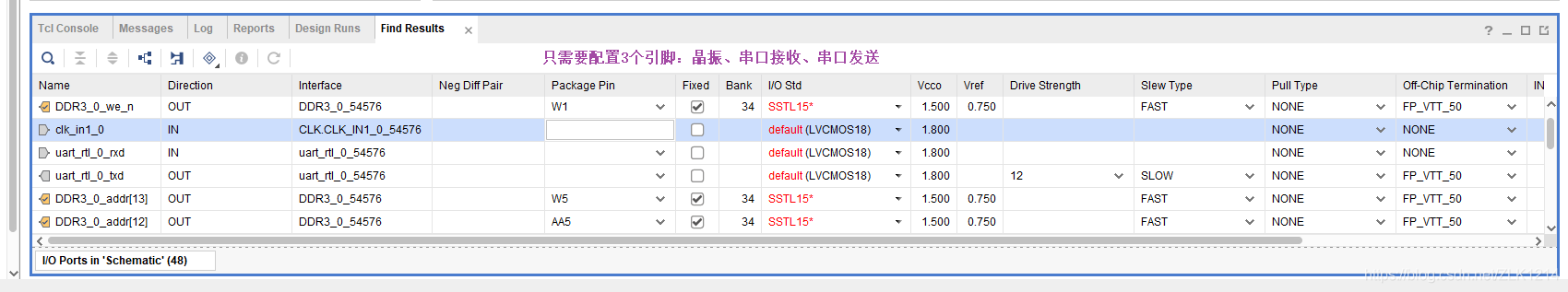

引脚配置:

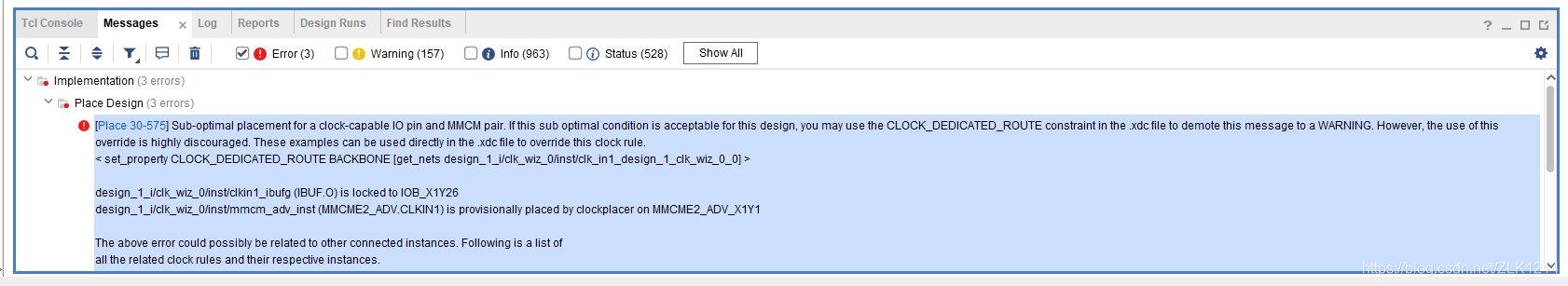

综合时会提示BANKBONE错误:

[Place 30-575] Sub-optimal placement for a clock-capable IO pin and MMCM pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE BACKBONE [get_nets design_1_i/clk_wiz_0/inst/clk_in1_design_1_clk_wiz_0_0] >

design_1_i/clk_wiz_0/inst/clkin1_ibufg (IBUF.O) is locked to IOB_X1Y26

design_1_i/clk_wiz_0/inst/mmcm_adv_inst (MMCME2_ADV.CLKIN1) is provisionally placed by clockplacer on MMCME2_ADV_X1Y1

The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.

Clock Rule: rule_mmcm_bufg

Status: PASS

Rule Description: An MMCM driving a BUFG must be placed on the same half side (top/bottom) of the device

design_1_i/clk_wiz_0/inst/mmcm_adv_inst (MMCME2_ADV.CLKFBOUT) is provisionally placed by clockplacer on MMCME2_ADV_X1Y1

and design_1_i/clk_wiz_0/inst/clkf_buf (BUFG.I) is provisionally placed by clockplacer on BUFGCTRL_X0Y31

将错误信息中提示的代码加入xdc文件就可以屏蔽掉此错误: