作者:付汉杰,hankf@xilinx.com,文章转载自:博客园

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。

在ZCU106单板上,有312个Block RAM,有96个Ultra RAM。客户需要1MB存储空间。实现MicroBlaze时,也使用Block RAM实现Cache,和Local Memory。剩下的个Block RAM不够做1MB的AXI BRAM。为了实现1MB空间,可以用Block RAM实现512KB AXI BRAM、256KB AXI BRAM;再使用Ultra RAM实现256KB AXI BRAM。为这三个AXI BRAM分配连续的地址空间,从而使软件感觉到这是一个存储器。其中,Block RAM和Ultra RAM还可以根据实际情况调整,比如用Block RAM实现512KB AXI BRAM;用Ultra RAM实现512KB AXI BRAM,两个存储器也可以实现1MB存储空间。

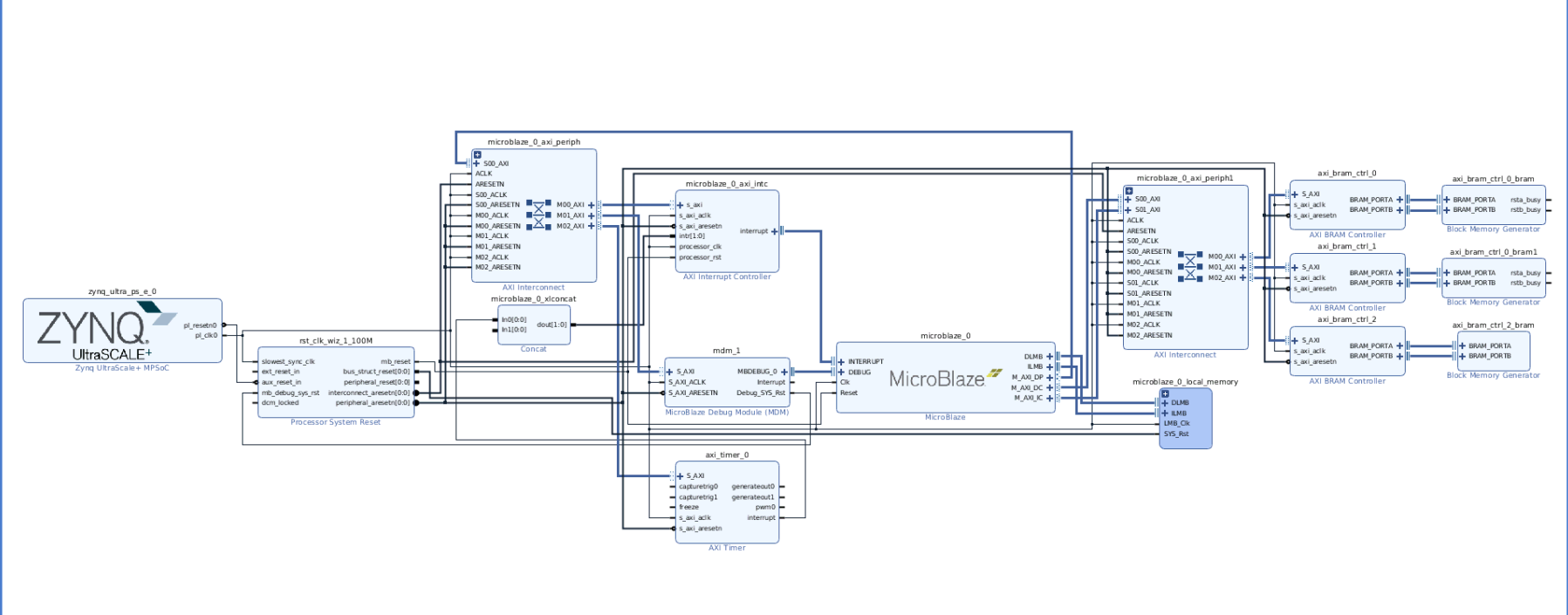

Vivado的Block设计

Vivado的地址分配

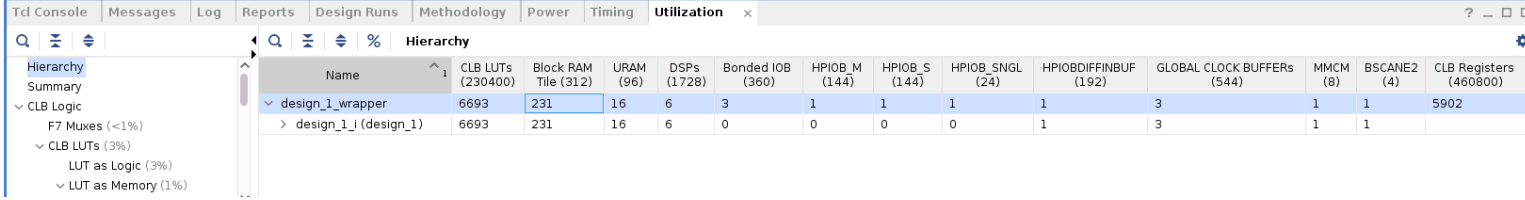

Vivado的器件资源使用情况

下面是Vivado IP Integrator的TCL脚本。

################################################################

# This is a generated script based on design: design_1

#

# Though there are limitations about the generated script,

# the main purpose of this utility is to make learning

# IP Integrator Tcl commands easier.

################################################################

namespace eval _tcl {

proc get_script_folder {} {

set script_path [file normalize [info script]]

set script_folder [file dirname $script_path]

return $script_folder

}

}

variable script_folder

set script_folder [_tcl::get_script_folder]

################################################################

# Check if script is running in correct Vivado version.

################################################################

set scripts_vivado_version 2018.3

set current_vivado_version [version -short]

if { [string first $scripts_vivado_version $current_vivado_version] == -1 } {

puts ""

common::send_msg_id "BD_TCL-1002" "WARNING" "This script was generated using Vivado <$scripts_vivado_version> without IP versions in the create_bd_cell commands, but is now being run in <$current_vivado_version> of Vivado. There may have been major IP version changes between Vivado <$scripts_vivado_version> and <$current_vivado_version>, which could impact the parameter settings of the IPs."

}

################################################################

# START

################################################################

# To test this script, run the following commands from Vivado Tcl console:

# source design_1_script.tcl

# If there is no project opened, this script will create a

# project, but make sure you do not have an existing project

# <./myproj/project_1.xpr> in the current working folder.

set list_projs [get_projects -quiet]

if { $list_projs eq "" } {

create_project project_1 myproj -part xczu7ev-ffvc1156-2-e

set_property BOARD_PART xilinx.com:zcu106:part0:2.3 [current_project]

}

# CHANGE DESIGN NAME HERE

variable design_name

set design_name design_1

# If you do not already have an existing IP Integrator design open,

# you can create a design using the following command:

# create_bd_design $design_name

# Creating design if needed

set errMsg ""

set nRet 0

set cur_design [current_bd_design -quiet]

set list_cells [get_bd_cells -quiet]

if { ${design_name} eq "" } {

# USE CASES:

# 1) Design_name not set

set errMsg "Please set the variable <design_name> to a non-empty value."

set nRet 1

} elseif { ${cur_design} ne "" && ${list_cells} eq "" } {

# USE CASES:

# 2): Current design opened AND is empty AND names same.

# 3): Current design opened AND is empty AND names diff; design_name NOT in project.

# 4): Current design opened AND is empty AND names diff; design_name exists in project.

if { $cur_design ne $design_name } {

common::send_msg_id "BD_TCL-001" "INFO" "Changing value of <design_name> from <$design_name> to <$cur_design> since current design is empty."

set design_name [get_property NAME $cur_design]

}

common::send_msg_id "BD_TCL-002" "INFO" "Constructing design in IPI design <$cur_design>..."

} elseif { ${cur_design} ne "" && $list_cells ne "" && $cur_design eq $design_name } {

# USE CASES:

# 5) Current design opened AND has components AND same names.

set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."

set nRet 1

} elseif { [get_files -quiet ${design_name}.bd] ne "" } {

# USE CASES:

# 6) Current opened design, has components, but diff names, design_name exists in project.

# 7) No opened design, design_name exists in project.

set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."

set nRet 2

} else {

# USE CASES:

# 8) No opened design, design_name not in project.

# 9) Current opened design, has components, but diff names, design_name not in project.

common::send_msg_id "BD_TCL-003" "INFO" "Currently there is no design <$design_name> in project, so creating one..."

create_bd_design $design_name

common::send_msg_id "BD_TCL-004" "INFO" "Making design <$design_name> as current_bd_design."

current_bd_design $design_name

}

common::send_msg_id "BD_TCL-005" "INFO" "Currently the variable <design_name> is equal to \"$design_name\"."

if { $nRet != 0 } {

catch {common::send_msg_id "BD_TCL-114" "ERROR" $errMsg}

return $nRet

}

set bCheckIPsPassed 1

##################################################################

# CHECK IPs

##################################################################

set bCheckIPs 1

if { $bCheckIPs == 1 } {

set list_check_ips "\

xilinx.com:ip:axi_bram_ctrl:*\

xilinx.com:ip:blk_mem_gen:*\

xilinx.com:ip:axi_timer:*\

xilinx.com:ip:clk_wiz:*\

xilinx.com:ip:mdm:*\

xilinx.com:ip:microblaze:*\

xilinx.com:ip:axi_intc:*\

xilinx.com:ip:xlconcat:*\

xilinx.com:ip:proc_sys_reset:*\

xilinx.com:ip:lmb_bram_if_cntlr:*\

xilinx.com:ip:lmb_v10:*\

"

set list_ips_missing ""

common::send_msg_id "BD_TCL-006" "INFO" "Checking if the following IPs exist in the project's IP catalog: $list_check_ips ."

foreach ip_vlnv $list_check_ips {

set ip_obj [get_ipdefs -all $ip_vlnv]

if { $ip_obj eq "" } {

lappend list_ips_missing $ip_vlnv

}

}

if { $list_ips_missing ne "" } {

catch {common::send_msg_id "BD_TCL-115" "ERROR" "The following IPs are not found in the IP Catalog:\n $list_ips_missing\n\nResolution: Please add the repository containing the IP(s) to the project." }

set bCheckIPsPassed 0

}

}

if { $bCheckIPsPassed != 1 } {

common::send_msg_id "BD_TCL-1003" "WARNING" "Will not continue with creation of design due to the error(s) above."

return 3

}

##################################################################

# DESIGN PROCs

##################################################################

# Hierarchical cell: microblaze_0_local_memory

proc create_hier_cell_microblaze_0_local_memory { parentCell nameHier } {

variable script_folder

if { $parentCell eq "" || $nameHier eq "" } {

catch {common::send_msg_id "BD_TCL-102" "ERROR" "create_hier_cell_microblaze_0_local_memory() - Empty argument(s)!"}

return

}

# Get object for parentCell

set parentObj [get_bd_cells $parentCell]

if { $parentObj == "" } {

catch {common::send_msg_id "BD_TCL-100" "ERROR" "Unable to find parent cell <$parentCell>!"}

return

}

# Make sure parentObj is hier blk

set parentType [get_property TYPE $parentObj]

if { $parentType ne "hier" } {

catch {common::send_msg_id "BD_TCL-101" "ERROR" "Parent <$parentObj> has TYPE = <$parentType>. Expected to be <hier>."}

return

}

# Save current instance; Restore later

set oldCurInst [current_bd_instance .]

# Set parent object as current

current_bd_instance $parentObj

# Create cell and set as current instance

set hier_obj [create_bd_cell -type hier $nameHier]

current_bd_instance $hier_obj

# Create interface pins

create_bd_intf_pin -mode MirroredMaster -vlnv xilinx.com:interface:lmb_rtl:1.0 DLMB

create_bd_intf_pin -mode MirroredMaster -vlnv xilinx.com:interface:lmb_rtl:1.0 ILMB

# Create pins

create_bd_pin -dir I -type clk LMB_Clk

create_bd_pin -dir I -type rst SYS_Rst

# Create instance: dlmb_bram_if_cntlr, and set properties

set dlmb_bram_if_cntlr [ create_bd_cell -type ip -vlnv xilinx.com:ip:lmb_bram_if_cntlr dlmb_bram_if_cntlr ]

set_property -dict [ list \

CONFIG.C_ECC {1} \

] $dlmb_bram_if_cntlr

# Create instance: dlmb_v10, and set properties

set dlmb_v10 [ create_bd_cell -type ip -vlnv xilinx.com:ip:lmb_v10 dlmb_v10 ]

# Create instance: ilmb_bram_if_cntlr, and set properties

set ilmb_bram_if_cntlr [ create_bd_cell -type ip -vlnv xilinx.com:ip:lmb_bram_if_cntlr ilmb_bram_if_cntlr ]

set_property -dict [ list \

CONFIG.C_ECC {1} \

] $ilmb_bram_if_cntlr

# Create instance: ilmb_v10, and set properties

set ilmb_v10 [ create_bd_cell -type ip -vlnv xilinx.com:ip:lmb_v10 ilmb_v10 ]

# Create instance: lmb_bram, and set properties

set lmb_bram [ create_bd_cell -type ip -vlnv xilinx.com:ip:blk_mem_gen lmb_bram ]

set_property -dict [ list \

CONFIG.Memory_Type {True_Dual_Port_RAM} \

CONFIG.use_bram_block {BRAM_Controller} \

] $lmb_bram

# Create interface connections

connect_bd_intf_net -intf_net microblaze_0_dlmb [get_bd_intf_pins DLMB] [get_bd_intf_pins dlmb_v10/LMB_M]

connect_bd_intf_net -intf_net microblaze_0_dlmb_bus [get_bd_intf_pins dlmb_bram_if_cntlr/SLMB] [get_bd_intf_pins dlmb_v10/LMB_Sl_0]

connect_bd_intf_net -intf_net microblaze_0_dlmb_cntlr [get_bd_intf_pins dlmb_bram_if_cntlr/BRAM_PORT] [get_bd_intf_pins lmb_bram/BRAM_PORTA]

connect_bd_intf_net -intf_net microblaze_0_ilmb [get_bd_intf_pins ILMB] [get_bd_intf_pins ilmb_v10/LMB_M]

connect_bd_intf_net -intf_net microblaze_0_ilmb_bus [get_bd_intf_pins ilmb_bram_if_cntlr/SLMB] [get_bd_intf_pins ilmb_v10/LMB_Sl_0]

connect_bd_intf_net -intf_net microblaze_0_ilmb_cntlr [get_bd_intf_pins ilmb_bram_if_cntlr/BRAM_PORT] [get_bd_intf_pins lmb_bram/BRAM_PORTB]

# Create port connections

connect_bd_net -net SYS_Rst_1 [get_bd_pins SYS_Rst] [get_bd_pins dlmb_bram_if_cntlr/LMB_Rst] [get_bd_pins dlmb_v10/SYS_Rst] [get_bd_pins ilmb_bram_if_cntlr/LMB_Rst] [get_bd_pins ilmb_v10/SYS_Rst]

connect_bd_net -net microblaze_0_Clk [get_bd_pins LMB_Clk] [get_bd_pins dlmb_bram_if_cntlr/LMB_Clk] [get_bd_pins dlmb_v10/LMB_Clk] [get_bd_pins ilmb_bram_if_cntlr/LMB_Clk] [get_bd_pins ilmb_v10/LMB_Clk]

# Restore current instance

current_bd_instance $oldCurInst

}

# Procedure to create entire design; Provide argument to make

# procedure reusable. If parentCell is "", will use root.

proc create_root_design { parentCell } {

variable script_folder

variable design_name

if { $parentCell eq "" } {

set parentCell [get_bd_cells /]

}

# Get object for parentCell

set parentObj [get_bd_cells $parentCell]

if { $parentObj == "" } {

catch {common::send_msg_id "BD_TCL-100" "ERROR" "Unable to find parent cell < $parentCell>!"}

return

}

# Make sure parentObj is hier blk

set parentType [get_property TYPE $parentObj]

if { $parentType ne "hier" } {

catch {common::send_msg_id "BD_TCL-101" "ERROR" "Parent <$parentObj> has TYPE = <$parentType>. Expected to be <hier>."}

return

}

# Save current instance; Restore later

set oldCurInst [current_bd_instance .]

# Set parent object as current

current_bd_instance $parentObj

# Create interface ports

set user_si570_sysclk [ create_bd_intf_port -mode Slave -vlnv xilinx.com:interface:diff_clock_rtl:1.0 user_si570_sysclk ]

set_property -dict [ list \

CONFIG.FREQ_HZ {300000000} \

] $user_si570_sysclk

# Create ports

set reset [ create_bd_port -dir I -type rst reset ]

set_property -dict [ list \

CONFIG.POLARITY {ACTIVE_HIGH} \

] $reset

# Create instance: axi_bram_ctrl_0, and set properties

set axi_bram_ctrl_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_bram_ctrl axi_bram_ctrl_0 ]

# Create instance: axi_bram_ctrl_0_bram, and set properties

set axi_bram_ctrl_0_bram [ create_bd_cell -type ip -vlnv xilinx.com:ip:blk_mem_gen axi_bram_ctrl_0_bram ]

set_property -dict [ list \

CONFIG.Memory_Type {True_Dual_Port_RAM} \

] $axi_bram_ctrl_0_bram

# Create instance: axi_timer_0, and set properties

set axi_timer_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_timer axi_timer_0 ]

# Create instance: clk_wiz_1, and set properties

set clk_wiz_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:clk_wiz clk_wiz_1 ]

set_property -dict [ list \

CONFIG.CLK_IN1_BOARD_INTERFACE {user_si570_sysclk} \

CONFIG.PRIM_SOURCE {Differential_clock_capable_pin} \

CONFIG.RESET_BOARD_INTERFACE {reset} \

CONFIG.USE_BOARD_FLOW {true} \

] $clk_wiz_1

# Create instance: mdm_1, and set properties

set mdm_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:mdm mdm_1 ]

set_property -dict [ list \

CONFIG.C_ADDR_SIZE {32} \

CONFIG.C_M_AXI_ADDR_WIDTH {32} \

CONFIG.C_USE_UART {1} \

] $mdm_1

# Create instance: microblaze_0, and set properties

set microblaze_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:microblaze microblaze_0 ]

set_property -dict [ list \

CONFIG.C_DEBUG_ENABLED {1} \

CONFIG.C_D_AXI {1} \

CONFIG.C_D_LMB {1} \

CONFIG.C_I_LMB {1} \

CONFIG.G_TEMPLATE_LIST {10} \

] $microblaze_0

# Create instance: microblaze_0_axi_intc, and set properties

set microblaze_0_axi_intc [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_intc microblaze_0_axi_intc ]

set_property -dict [ list \

CONFIG.C_HAS_FAST {1} \

] $microblaze_0_axi_intc

# Create instance: microblaze_0_axi_periph, and set properties

set microblaze_0_axi_periph [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_interconnect microblaze_0_axi_periph ]

set_property -dict [ list \

CONFIG.NUM_MI {3} \

CONFIG.NUM_SI {1} \

] $microblaze_0_axi_periph

# Create instance: microblaze_0_axi_periph1, and set properties

set microblaze_0_axi_periph1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_interconnect microblaze_0_axi_periph1 ]

set_property -dict [ list \

CONFIG.NUM_MI {1} \

CONFIG.NUM_SI {2} \

] $microblaze_0_axi_periph1

# Create instance: microblaze_0_local_memory

create_hier_cell_microblaze_0_local_memory [current_bd_instance .] microblaze_0_local_memory

# Create instance: microblaze_0_xlconcat, and set properties

set microblaze_0_xlconcat [ create_bd_cell -type ip -vlnv xilinx.com:ip:xlconcat microblaze_0_xlconcat ]

# Create instance: rst_clk_wiz_1_100M, and set properties

set rst_clk_wiz_1_100M [ create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset rst_clk_wiz_1_100M ]

set_property -dict [ list \

CONFIG.RESET_BOARD_INTERFACE {reset} \

CONFIG.USE_BOARD_FLOW {true} \

] $rst_clk_wiz_1_100M

# Create interface connections

connect_bd_intf_net -intf_net axi_bram_ctrl_0_BRAM_PORTA [get_bd_intf_pins axi_bram_ctrl_0/BRAM_PORTA] [get_bd_intf_pins axi_bram_ctrl_0_bram/BRAM_PORTA]

connect_bd_intf_net -intf_net axi_bram_ctrl_0_BRAM_PORTB [get_bd_intf_pins axi_bram_ctrl_0/BRAM_PORTB] [get_bd_intf_pins axi_bram_ctrl_0_bram/BRAM_PORTB]

connect_bd_intf_net -intf_net microblaze_0_M_AXI_DC [get_bd_intf_pins microblaze_0/M_AXI_DC] [get_bd_intf_pins microblaze_0_axi_periph1/S00_AXI]

connect_bd_intf_net -intf_net microblaze_0_M_AXI_IC [get_bd_intf_pins microblaze_0/M_AXI_IC] [get_bd_intf_pins microblaze_0_axi_periph1/S01_AXI]

connect_bd_intf_net -intf_net microblaze_0_axi_dp [get_bd_intf_pins microblaze_0/M_AXI_DP] [get_bd_intf_pins microblaze_0_axi_periph/S00_AXI]

connect_bd_intf_net -intf_net microblaze_0_axi_periph1_M00_AXI [get_bd_intf_pins axi_bram_ctrl_0/S_AXI] [get_bd_intf_pins microblaze_0_axi_periph1/M00_AXI]

connect_bd_intf_net -intf_net microblaze_0_axi_periph_M02_AXI [get_bd_intf_pins axi_timer_0/S_AXI] [get_bd_intf_pins microblaze_0_axi_periph/M02_AXI]

connect_bd_intf_net -intf_net microblaze_0_debug [get_bd_intf_pins mdm_1/MBDEBUG_0] [get_bd_intf_pins microblaze_0/DEBUG]

connect_bd_intf_net -intf_net microblaze_0_dlmb_1 [get_bd_intf_pins microblaze_0/DLMB] [get_bd_intf_pins microblaze_0_local_memory/DLMB]

connect_bd_intf_net -intf_net microblaze_0_ilmb_1 [get_bd_intf_pins microblaze_0/ILMB] [get_bd_intf_pins microblaze_0_local_memory/ILMB]

connect_bd_intf_net -intf_net microblaze_0_intc_axi [get_bd_intf_pins microblaze_0_axi_intc/s_axi] [get_bd_intf_pins microblaze_0_axi_periph/M00_AXI]

connect_bd_intf_net -intf_net microblaze_0_interrupt [get_bd_intf_pins microblaze_0/INTERRUPT] [get_bd_intf_pins microblaze_0_axi_intc/interrupt]

connect_bd_intf_net -intf_net microblaze_0_mdm_axi [get_bd_intf_pins mdm_1/S_AXI] [get_bd_intf_pins microblaze_0_axi_periph/M01_AXI]

connect_bd_intf_net -intf_net user_si570_sysclk_1 [get_bd_intf_ports user_si570_sysclk] [get_bd_intf_pins clk_wiz_1/CLK_IN1_D]

# Create port connections

connect_bd_net -net ARESETN_1 [get_bd_pins microblaze_0_axi_periph/ARESETN] [get_bd_pins microblaze_0_axi_periph1/ARESETN] [get_bd_pins rst_clk_wiz_1_100M/interconnect_aresetn]

connect_bd_net -net axi_timer_0_interrupt [get_bd_pins axi_timer_0/interrupt] [get_bd_pins microblaze_0_xlconcat/In0]

connect_bd_net -net clk_wiz_1_locked [get_bd_pins clk_wiz_1/locked] [get_bd_pins rst_clk_wiz_1_100M/dcm_locked]

connect_bd_net -net mdm_1_debug_sys_rst [get_bd_pins mdm_1/Debug_SYS_Rst] [get_bd_pins rst_clk_wiz_1_100M/mb_debug_sys_rst]

connect_bd_net -net microblaze_0_Clk [get_bd_pins axi_bram_ctrl_0/s_axi_aclk] [get_bd_pins axi_timer_0/s_axi_aclk] [get_bd_pins clk_wiz_1/clk_out1] [get_bd_pins mdm_1/S_AXI_ACLK] [get_bd_pins microblaze_0/Clk] [get_bd_pins microblaze_0_axi_intc/processor_clk] [get_bd_pins microblaze_0_axi_intc/s_axi_aclk] [get_bd_pins microblaze_0_axi_periph/ACLK] [get_bd_pins microblaze_0_axi_periph/M00_ACLK] [get_bd_pins microblaze_0_axi_periph/M01_ACLK] [get_bd_pins microblaze_0_axi_periph/M02_ACLK] [get_bd_pins microblaze_0_axi_periph/S00_ACLK] [get_bd_pins microblaze_0_axi_periph1/ACLK] [get_bd_pins microblaze_0_axi_periph1/M00_ACLK] [get_bd_pins microblaze_0_axi_periph1/S00_ACLK] [get_bd_pins microblaze_0_axi_periph1/S01_ACLK] [get_bd_pins microblaze_0_local_memory/LMB_Clk] [get_bd_pins rst_clk_wiz_1_100M/slowest_sync_clk]

connect_bd_net -net microblaze_0_intr [get_bd_pins microblaze_0_axi_intc/intr] [get_bd_pins microblaze_0_xlconcat/dout]

connect_bd_net -net reset_1 [get_bd_ports reset] [get_bd_pins clk_wiz_1/reset] [get_bd_pins rst_clk_wiz_1_100M/ext_reset_in]

connect_bd_net -net rst_clk_wiz_1_100M_bus_struct_reset [get_bd_pins microblaze_0_local_memory/SYS_Rst] [get_bd_pins rst_clk_wiz_1_100M/bus_struct_reset]

connect_bd_net -net rst_clk_wiz_1_100M_mb_reset [get_bd_pins microblaze_0/Reset] [get_bd_pins microblaze_0_axi_intc/processor_rst] [get_bd_pins rst_clk_wiz_1_100M/mb_reset]

connect_bd_net -net rst_clk_wiz_1_100M_peripheral_aresetn [get_bd_pins axi_bram_ctrl_0/s_axi_aresetn] [get_bd_pins axi_timer_0/s_axi_aresetn] [get_bd_pins mdm_1/S_AXI_ARESETN] [get_bd_pins microblaze_0_axi_intc/s_axi_aresetn] [get_bd_pins microblaze_0_axi_periph/M00_ARESETN] [get_bd_pins microblaze_0_axi_periph/M01_ARESETN] [get_bd_pins microblaze_0_axi_periph/M02_ARESETN] [get_bd_pins microblaze_0_axi_periph/S00_ARESETN] [get_bd_pins microblaze_0_axi_periph1/M00_ARESETN] [get_bd_pins microblaze_0_axi_periph1/S00_ARESETN] [get_bd_pins microblaze_0_axi_periph1/S01_ARESETN] [get_bd_pins rst_clk_wiz_1_100M/peripheral_aresetn]

# Create address segments

create_bd_addr_seg -range 0x00080000 -offset 0x80000000 [get_bd_addr_spaces microblaze_0/Data] [get_bd_addr_segs axi_bram_ctrl_0/S_AXI/Mem0] SEG_axi_bram_ctrl_0_Mem0

create_bd_addr_seg -range 0x00080000 -offset 0x80000000 [get_bd_addr_spaces microblaze_0/Instruction] [get_bd_addr_segs axi_bram_ctrl_0/S_AXI/Mem0] SEG_axi_bram_ctrl_0_Mem0

create_bd_addr_seg -range 0x00010000 -offset 0x41C00000 [get_bd_addr_spaces microblaze_0/Data] [get_bd_addr_segs axi_timer_0/S_AXI/Reg] SEG_axi_timer_0_Reg

create_bd_addr_seg -range 0x00010000 -offset 0x00000000 [get_bd_addr_spaces microblaze_0/Data] [get_bd_addr_segs microblaze_0_local_memory/dlmb_bram_if_cntlr/SLMB/Mem] SEG_dlmb_bram_if_cntlr_Mem

create_bd_addr_seg -range 0x00010000 -offset 0x00000000 [get_bd_addr_spaces microblaze_0/Instruction] [get_bd_addr_segs microblaze_0_local_memory/ilmb_bram_if_cntlr/SLMB/Mem] SEG_ilmb_bram_if_cntlr_Mem

create_bd_addr_seg -range 0x00001000 -offset 0x41400000 [get_bd_addr_spaces microblaze_0/Data] [get_bd_addr_segs mdm_1/S_AXI/Reg] SEG_mdm_1_Reg

create_bd_addr_seg -range 0x00010000 -offset 0x41200000 [get_bd_addr_spaces microblaze_0/Data] [get_bd_addr_segs microblaze_0_axi_intc/S_AXI/Reg] SEG_microblaze_0_axi_intc_Reg

# Restore current instance

current_bd_instance $oldCurInst

validate_bd_design

save_bd_design

}

# End of create_root_design()

##################################################################

# MAIN FLOW

##################################################################

create_root_design ""软件测试过程

xsct% connect

attempting to launch hw_server

****** Xilinx hw_server v2018.3

**** Build date : Dec 7 2018-00:40:27

** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

INFO: hw_server application started

INFO: Use Ctrl-C to exit hw_server application

****** Xilinx hw_server v2018.3

**** Build date : Dec 7 2018-00:40:27

** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

INFO: hw_server application started

INFO: Use Ctrl-C to exit hw_server application

INFO: To connect to this hw_server instance use url: TCP:127.0.0.1:3121

target

1* PS TAP

2 PMU

3 PL

13 MicroBlaze Debug Module at USER2

14 MicroBlaze #0 (Running)

xsct% target 14

xsct% rst -proc

Info: MicroBlaze #0 (target 14) Stopped at 0x10 (Stop)

xsct% target

1 PS TAP

2 PMU

3 PL

13 MicroBlaze Debug Module at USER2

14* MicroBlaze #0 (Stop)

xsct% rrd

r0: 00000000 r1: 00000000 r2: 00000000 r3: 00000000 r4: 00000000

r5: 00000000 r6: 00000000 r7: 00000000 r8: 00000000 r9: 00000000

r10: 00000000 r11: 00000000 r12: 00000000 r13: 00000000 r14: 00000000

r15: 00000000 r16: 00000000 r17: 00000000 r18: 00000000 r19: 00000000

r20: 00000000 r21: 00000000 r22: 00000000 r23: 00000000 r24: 00000000

r25: 00000000 r26: 00000000 r27: 00000000 r28: 00000000 r29: 00000000

r30: 00000000 r31: 00000000 pc: 00000010 msr: 00000400 ear: 00000000

esr: 00000000 fsr: 00000000 btr: 00000000 pvr mmu

dcr: 00000009 dsr: 21010001

xsct% mrd 0x80000000 0x10

80000000: 00000000

80000004: 00000000

80000008: 00000000

8000000C: 00000000

80000010: 00000000

80000014: 00000000

80000018: 00000000

8000001C: 00000000

80000020: 00000000

80000024: 00000000

80000028: 00000000

8000002C: 00000000

80000030: 00000000

80000034: 00000000

80000038: 00000000

8000003C: 00000000

xsct% mwr 0x80000000 0x12345678

xsct% mrd 0x80000000 0x10

80000000: 12345678

80000004: 00000000

80000008: 00000000

8000000C: 00000000

80000010: 00000000

80000014: 00000000

80000018: 00000000

8000001C: 00000000

80000020: 00000000

80000024: 00000000

80000028: 00000000

8000002C: 00000000

80000030: 00000000

80000034: 00000000

80000038: 00000000

8000003C: 00000000