作者:小牛1022 文章来源:FPGA杂记微信公众号

今天记录一下Xilinx的Float point IP核。首先看一下这个核的简介:Float point IP可以用来进行浮点数计算,这在FPGA中是很重要的一个功能。通过阅读IP手册可以知道,该IP支持的很多种浮点数计算,今天主要介绍最简单的加法操作。通过加法的介绍,可以明白数据在IP核中是如何表达的(这个是本文的重点内容),举一反三可以理解其他操作。

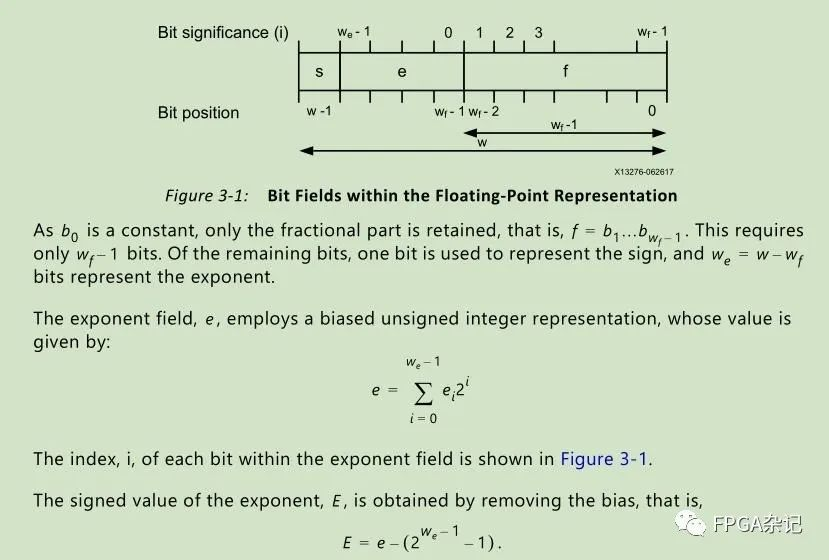

下图是手册中关于浮点数的描述:

需要注意的是:E和e的区别,这一点很重要否则算出的数据肯定是错误的。其次需要表达式v中符号部分、整数部分和小数部分都是相乘的关系。下面通过“在半精度形式下2.5的表达形式为16‘h4100”这个例子来详细说明。16'h4100的符号位为1'b0,整数部分为5'b10000,小数部分为11'b01000000000。根据手册我们计算出s=0;E=2^4-(2^4-1)=1;小数部分为1+0*2^(-1)+1*2^(-2)+0+...+0=1.25。所以最终的结果值为1*2^1*1.25=2.5。

2、仿真。vivado生成该IP核之后没有对应的example design,所以不能用自带的仿真例程。但是如果直接将数据输入进去验证正确性需要很多的计算。经过查看IP核目录文件,在demo_tb文件中有自带了仿真文件,将该文件加入到工程中就可以直接仿真这个IP核了,并且tb中会将对应的小数显示出来。仔细阅读相应的tb文件会更加深入的了解数据的表达形式。