SDR是一种无线电广播通信技术,它基于软件定义的无线通信协议而非通过硬连线实现。频带、空中接口协议和功能可通过软件下载和更新来升级,而不用完全更换硬件。恰如其名,SDR具有通过软件或可重定义逻辑改变自身功能的能力,从而通过动态加载新的波形和协议可使用不同的波形和协议操作。

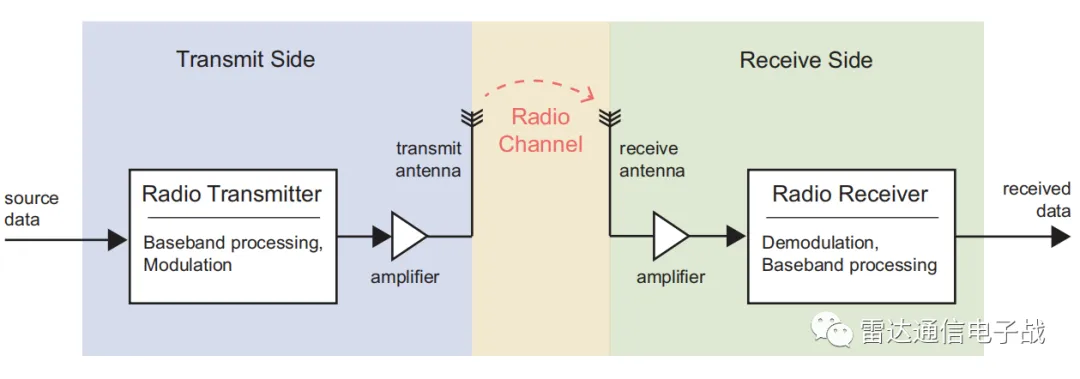

传统的商用基站体积较大,需要设计很多专用的硬件电路;而SDR基站体积较小,大部分通信功能由软件实现。SDR架构舍去了传统无线电电路中所有硬件单元包括变频、混频、滤波器、放大器、检波器、解调器等,完全是一种新的架构和技术。

SDR技术在军用和商用无线电领域早已广泛使用。随着通信技术的快速发展,更轻松、更灵活地对通信设备进行测试和测量变得越来越重要,尤其是在军事应用中。基于软件定义无线电技术的测试设备为推进这些通信提供了成本效益、灵活性和能力。

ZYNQ+AD9361

ZYNQ+AD9361是一种基于Xilinx Zynq FPGA和ADI公司的AD9361 RF捷变收发器的开源SDR硬件平台。Zynq FPGA集成了ARM处理器和FPGA逻辑,可以实现高性能的数字信号处理。AD9361是一种高度集成的RF捷变收发器,能够在70 MHz至6 GHz 的频率范围内工作,支持多种调制方式。

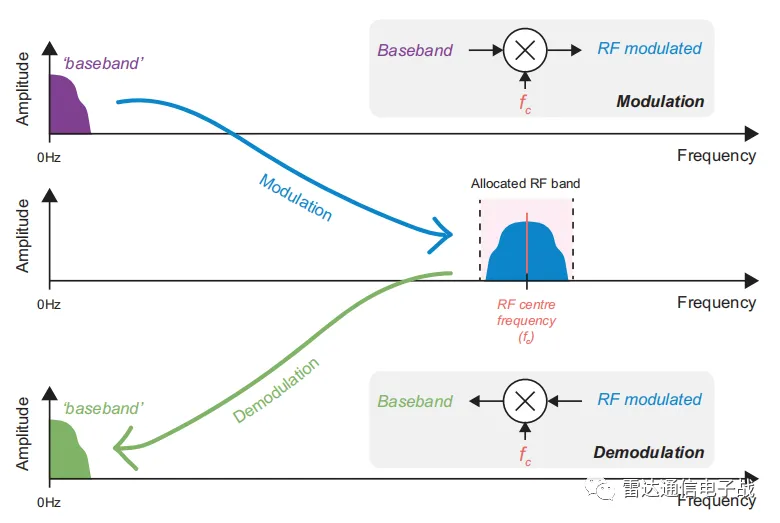

通过将Zynq FPGA和AD9361 RF捷变收发器相结合,可以实现一个完整的 SDR系统。Zynq FPGA 可以用来实现数字下变频、数字上变频、信道滤波、解调和调制等数字信号处理功能。

AD9361 RF捷变收发器负责将射频信号转换为中频或基带信号,以便进行数字信号处理,也负责将处理后的基带或中频信号转换为射频信号并发送出去。信号处理采用正交调制和解调将信号分为同相分量(I路)和正交分量(Q路)分别调制,再叠加在一起发送;接收时将I/Q混合信号分离后,再解调处理。

Zynq FPGA 和AD9361 RF 捷变收发器之间通常通过LVDS接口连接。Zynq FPGA可以通过AXI接口与ARM处理器进行通信,实现数据交换和控制。ARM 处理器可以运行嵌入式操作系统,如Linux或FreeRTOS,用于实现上层协议栈和应用程序。

Zynq UltraScale+ RFSoC平台

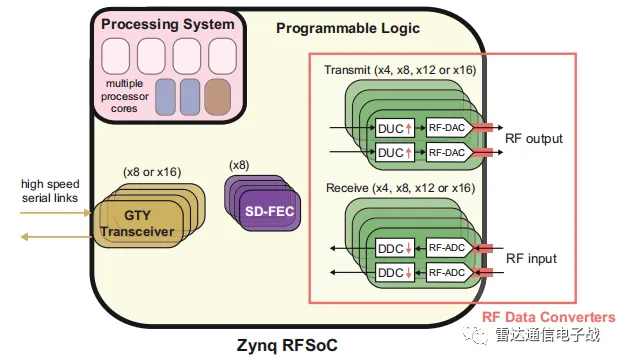

使用Zynq UltraScale+ RFSoC平台(以下简称为“RFSoC”)是专门针对射频(RF)应用的片上系统(SoC)。RFSoC是AMD(前身为Xilinx,于2022年被AMD收购)开发的第三个主要Zynq SoC,第一个是2010年初的Zynq-7000 SoC,Y也就是上面架构中使用的ZYNQ。这里的Zynq UltraScale+多处理器SoC (MPSoC)先于RFSoC,除了无线电的特定功能外,它与MPSoc几乎一样。

所有三种SoC类型都由用于运行软件的处理系统(PS)、现场可编程门阵列(FPGA)的可编程逻辑(PL)以及两部分之间的高速互连等部分组成。RFSoC器件架构的如图所示。请注意PS和PL部分,特别是PL包含一些对SDR应用特别重要的突出显示功能。

方案对比

可以看出,ZYNQ+AD9361是一种低成本的方案,而Zynq UltraScale+ RFSoC平台则相对高很多,但是无论PS还是PL的性能都是有很大的提升。另外一种折中的方式便是MPSoc+AD9361。

点击下载《Software Define Radio with Zynq UltraScale+ RFSoC》

文章来源:雷达通信电子战