【视频】Xilinx Virtex UltraScale+ VU19P FPGA

judy 在 周二, 08/27/2019 - 09:58 提交

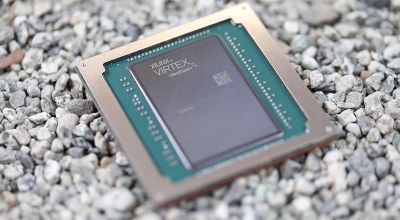

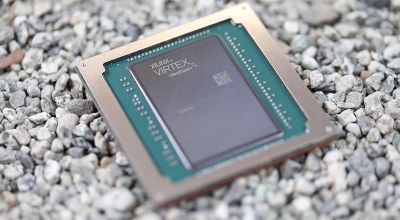

Xilinx 推出全球容量最大的 FPGA - Virtex® UltraScale+™ VU19P,不仅能实现当今最先进 ASIC 和 SoC 技术的原型与模拟设计,还能支持各种复杂的新兴算法。

Virtex® UltraScale™ FPGA 是赛灵思(Xilinx)推出的一种高性能 FPGA 系列,采用先进的 UltraScale 架构。该系列 FPGA 具有卓越的性能和灵活性,广泛应用于各种高性能计算、数据中心、通信和其他领域。

Virtex UltraScale FPGA 系列为设计人员提供了强大的工具和资源,以满足对高性能、低功耗、灵活性和可扩展性的需求。

Xilinx 推出全球容量最大的 FPGA - Virtex® UltraScale+™ VU19P,不仅能实现当今最先进 ASIC 和 SoC 技术的原型与模拟设计,还能支持各种复杂的新兴算法。

经常听到有媒体问ASIC是否取代FPGA这类问题,看看ASIC设计流程,其中的数字前端中的仿真和验证是离不开FPGA的,所以FPGA和ASIC是共生关系,有了更大的FPGA ,才能在数字IC仿真原型设计效率上大大提升,才可以支持和设计更复杂更大的ASIC,近10年来,赛灵思一直保持着最大业内FPGA的记录,今天,赛灵思再次刷新最大FPGA的新记录

自适应和智能计算的全球领先企业赛灵思公司今天宣布推出全球最大容量的 FPGA – Virtex UltraScale+ VU19P,从而进一步扩展了旗下 16 纳米 (nm) Virtex UltraScale+ 产品系列。VU19P拥有 350 亿个晶体管,拥有有史以来单颗芯片最高逻辑密度和最大I/O 数量,可用以支持未来最先进 ASIC 和 SoC 技术的仿真与原型设计。

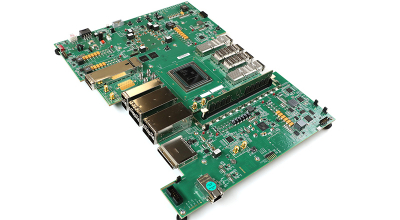

VCU129 开发板整合了集成 PAM4 收发器的 Virtex® UltraScale+™ 58G PAM4 VU29P FPGA,可实现新一代网络平台。VCU129 评估套件展示了 Xilinx SerDes 技术的领先地位,可充分利用 Xilinx 无盖封装方法的低成本散热设计。VCU129 具有多种通用高速互连、板载内存和 PCIe®Gen 3 接口。

VCU128 开发板采用全新 Xilinx VU37P HBM FPGA,利用堆叠芯片互连将 HBM 裸片添加到封装基板上的 FPGA 裸片旁边。支持高带宽存储器(HBM) 的 Xilinx FPGA 是计算带宽问题(与在 PCB 上使用 DDR4 等并行内存相关)的明确解决方案。

VCU128 评估套件现已推出量产 Virtex UltraScale + HBM FPGA。VCU128 评估套件集成了全新的赛灵思 Virtex UltraSacle+ VU37P HBM FPGA,可在 FPGA 裸片旁边集成 8GB HBM DRAM,从而实现大容量存储器带宽以及更小的 PCB 封装尺寸。

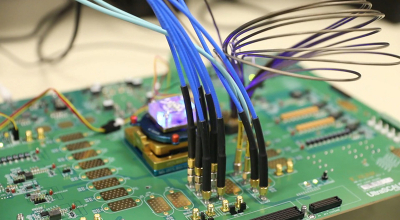

通过 Xilinx 58G 驱动 GTM 收发器和 Virtex® UltraScale+™ 集成强化 100G 以太网子系统,在两个通道上演示 100G 以太网。 该视频概述了 GTM 收发器如何使传统硬件支持 58G PAM4

在 DesignCon 2019 上,Xilinx 和 TE 展示了一对演示。首先,UltraScale + FPGA 中的 32G Xilinx GTY NRZ SERDES 通过 TE Sliver 连接器运行。 接下来,Virtex UltraScale + GTM PAM4 收发器通过 TE SFP-DD 连接器和直接连接铜缆发送数据

在 DesignCon 2019 上,Xilinx 和 Molex 展示了一组演示。 首先,Virtex UltraScale + FPGA 中的 Xilinx GTM 58G PAM4 SERDES 运行于超过 3 米的 QSFP-DD 直接连接铜缆,由Molex Near-Stack 高速连接解决方案提供支持。

云服务和5G的推出推动了数据流量的大幅增长,这为满足网络日益增长的带宽要求带来了挑战,路由器和交换机接线端口密度、光学标准的扩展以及光纤网络带宽的更新是成本能够满足带宽需求的主要制约因素,转换为58G收发器是非常重要的一步,在相同的条件下它能够实现400G以上的数据传输速率