作者: 张国斌

经常听到有媒体问ASIC是否取代FPGA这类问题,看看ASIC设计流程,其中的数字前端中的仿真和验证是离不开FPGA的,所以FPGA和ASIC是共生关系,有了更大的FPGA ,才能在数字IC仿真原型设计效率上大大提升,才可以支持和设计更复杂更大的ASIC,近10年来,赛灵思一直保持着最大业内FPGA的记录,今天,赛灵思再次刷新最大FPGA的新记录。

图1 赛灵思一直保持最大FPGA领导地位

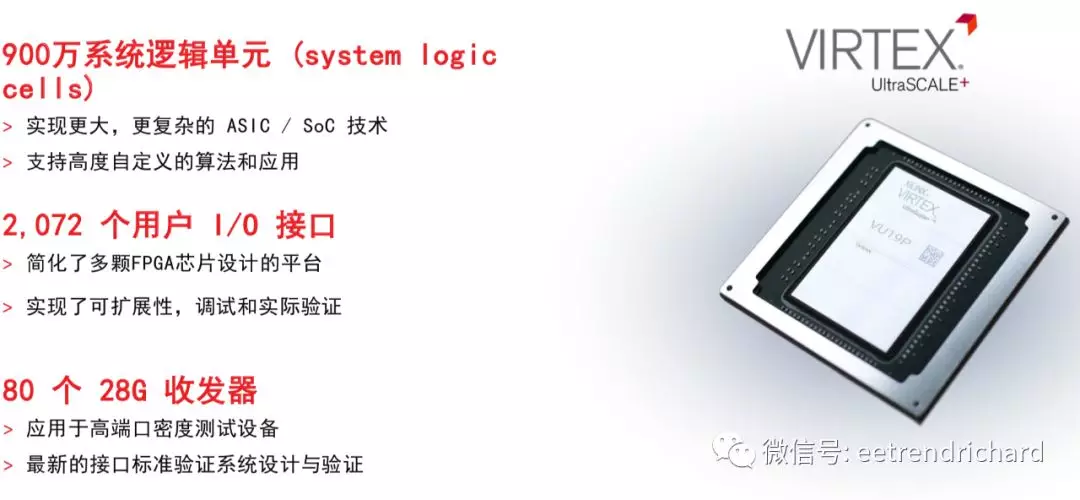

赛灵思公司刚刚宣布推出全球最大容量的 FPGA – Virtex UltraScale+ VU19P,从而进一步扩展了旗下 16 纳米 (nm) Virtex® UltraScale+™ 产品系列。VU19P拥有 350 亿个晶体管,是有史以来单颗芯片最高逻辑密度和最大I/O 数量的FPGA,它除了可以支持未来最先进 ASIC 和 SoC 技术的仿真与原型设计外,也将广泛支持测试测量、计算、网络、航空航天和国防等相关应用。

图2 赛灵思发言人展示最大FPGA

赛灵思公司测试,测量和仿真人工智能事业部高级市场总监Hanneke Krekels (上图左)在芯片发布会上指出随着机器学习、5G、汽车应用、视觉应用不断走热,超大规模 ASIC 及 SoC 需求增加,而且在架构不断创新的趋势影响下,仿真和原型设计面临更多挑战,“目前,原型开发设计的增长速度超过了仿真速度,而且已经出现了支持基于机架 (rack-based)的原型开发设计。”她强调,“而且随着云计算的兴起,一些设计可以将临时“峰值” 仿真和原型开发从内部卸载到云端,这些需求都呼唤更大FPGA的诞生!”

图3 VU19P关键指标

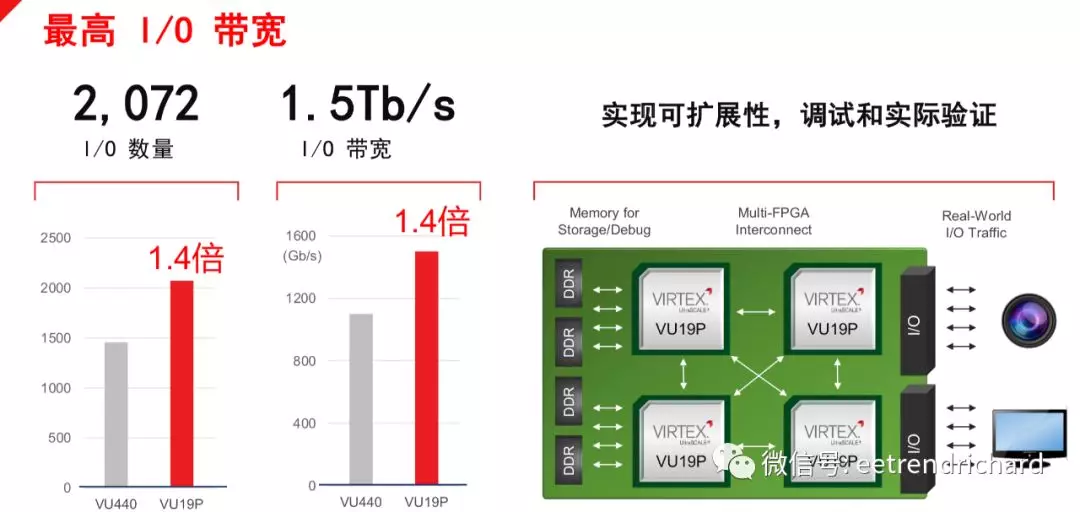

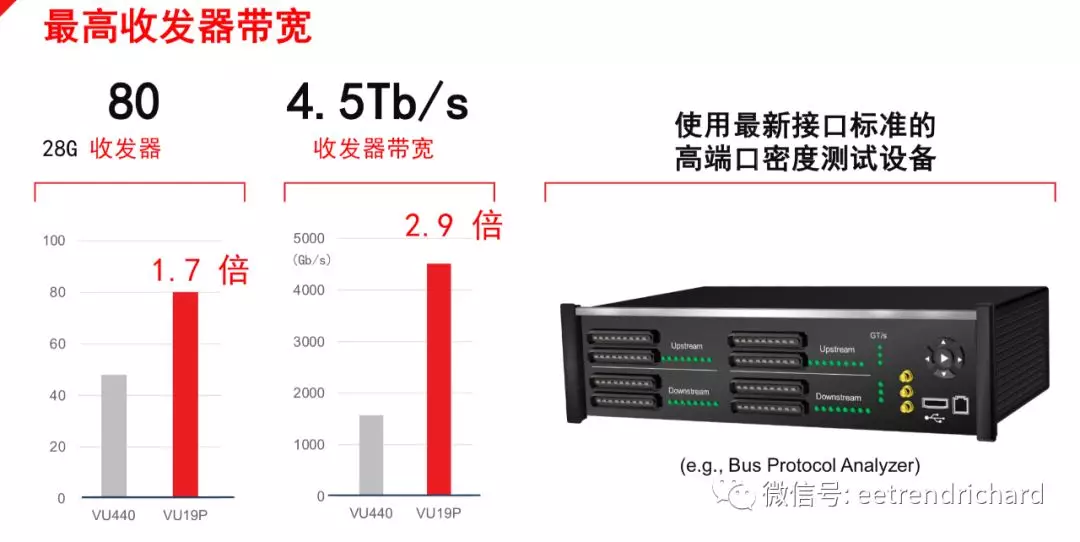

据赛灵思Virtex® UltraScale+TM 产品系列级产品线经理Mike Thompson介绍,VU19P 树立了 FPGA 行业的新标杆,它拥有 900 万个系统逻辑单元370亿个晶体管、每秒高达 1.5 Terabit 的DDR4存储器带宽、每秒高达 4.5 Terabit 的收发器带宽和超过 2,000 个用户 I/O。它为创建当今最复杂 SoC 的原型与模拟提供了可能,同时它也可以支持各种复杂的新兴算法,如用于人工智能 (AI)、机器学习 (ML)、视频处理和传感器融合等领域的算法。相比上一代业界最大容量的FPGA (20 nm 的 UltraScale 440 FPGA) ,VU19P 将容量扩大了 1.6 倍。

图4 VU19P关键技术指标

赛灵思产品线市场营销与管理高级总监 Sumit Shah 表示:“VU19P 不仅能帮助开发者加速硬件验证,还能助其在 ASIC 或 SoC 可用之前就能提前进行软件集成。VU 19P是赛灵思刷新世界记录的第三代 FPGA。VU19P所带来的不仅仅是尖端的芯片技术,同时我们还为之提供了可靠且业经验证的工具流和 IP支持。”

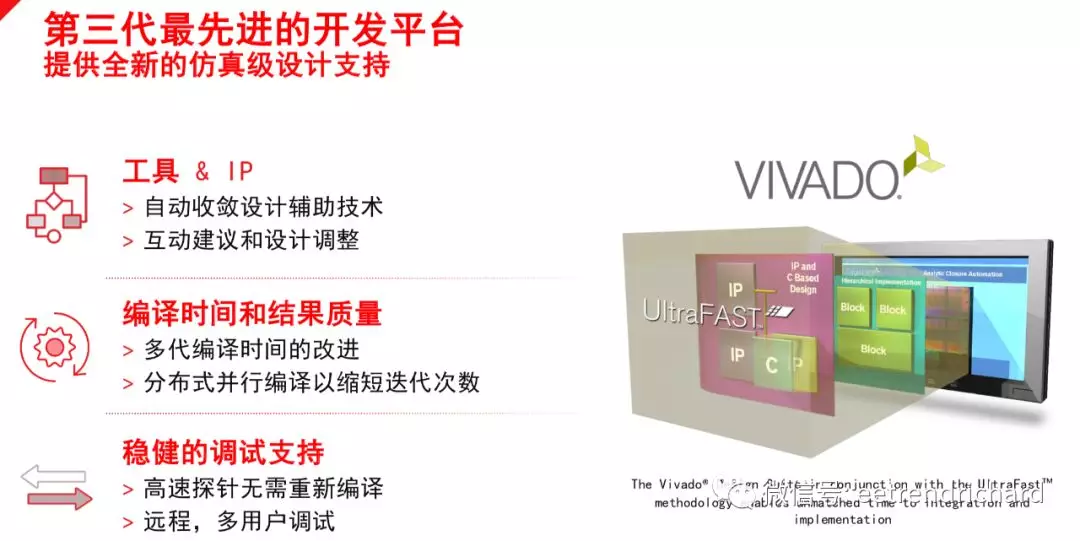

Thompson介绍说VU 19P提供了全新的仿真级设计,如支持自动收敛设计辅助技术 、互动建议和设计调整等,而且通过多代编译时间的改进以及分布式并行编译,不但缩短了迭代次数也优化了编译时间和结果质量,此外高速探针无需重新编译 ,支持远程,多用户调试都意味着这块最大的FPGA支持更稳健的调试。

他表示通过一系列调试工具、可视化工具和 IP 支持,VU19P 为客户快速设计和验证新一代应用与技术提供了一个全面的开发平台。软硬件协同验证支持开发者在取得实体器件之前就能提前着手启动软件与定制功能的实现。此外,通过使用赛灵思 Vivado® 设计套件,可以协同优化设计流程,从而降低成本、减轻流片风险、提高效率并加速产品上市进程。

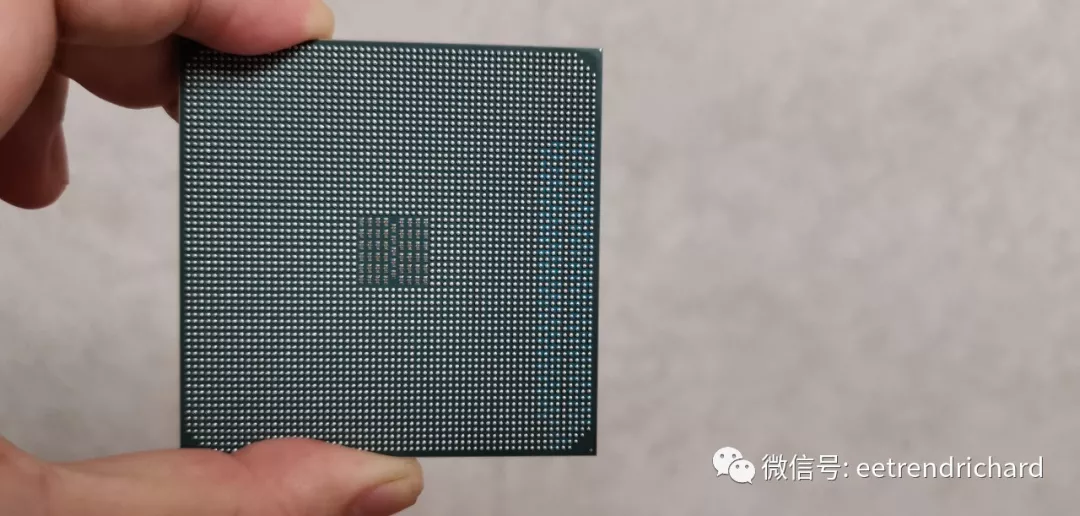

图5 VU19P的芯片上手

这款最大的FPGA采用了2.5D堆叠硅片互联 (SSIT) 技术实现了大容量,Thompson把未来赛灵思还会采用7nm工艺来实现更大容量FPGA。

图 6 赛灵思的2.5D堆叠硅片互联 (SSIT) 技术

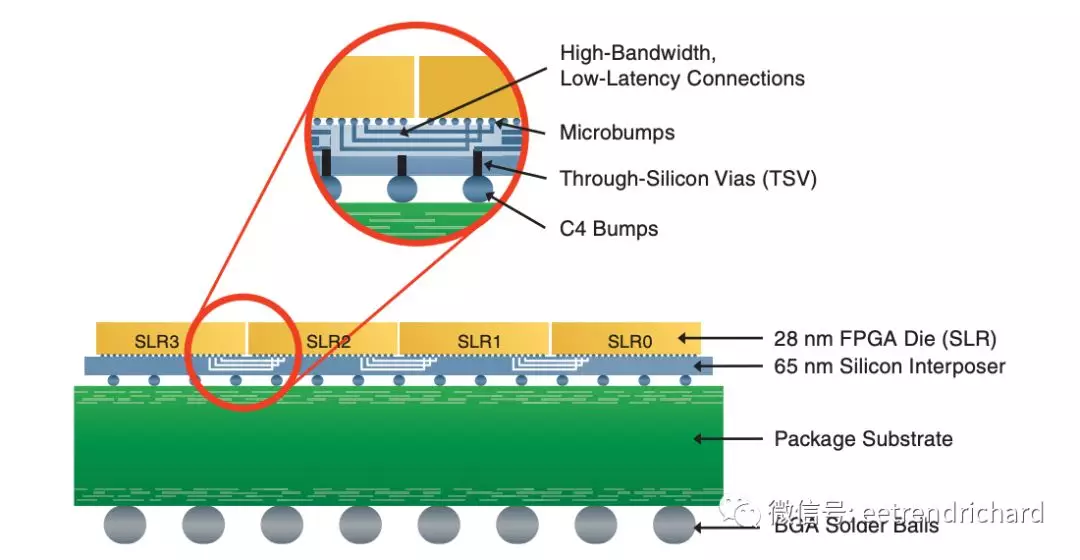

2.5D “堆叠硅片互联技术”(SST)是2011年在Virtex®-7 2000T上实现的技术,目前已经发展到第四代,Virtex-7 2000T利用这个技术实现了 68 亿个晶体管设计,可支持 200 万个系统逻辑单元。

图7 堆叠硅片互联技术示意图

Thompson表示很多大的IC设计公司已经EDA工具厂商都将是VU19P的潜在客户,他透露ARM已经在使用这个器件做开发,这也预示ARM在利用这款最大的FPGA开发最新的处理器。

ARM 设计服务总监 Tran Nguyen 表示:“ARM 依靠赛灵思器件作为验证我们新一代处理器 IP 和 SoC 技术的工艺。全新推出的 VU19P 将支持Arm及 我们生态系统中的众多其他合作伙伴,加速实现设计、开发和验证我们最宏伟的技术路线图。”

据悉,VU19P 将于 2020 年秋季上市。如需进一步了解有关 VU19P 以及赛灵思完整的 Virtex UltraScale+ FPGA 产品线的更多消息,请访问:china.xilinx.com/products/silicon-devices/fpga/virtex-ultrascale-plus-vu19p.html。

期待这款迄今最大FPGA让本土公司设计出更强大的C产品。