如何编写一个基本的 Verilog Module(模块)

judy 在 周三, 02/22/2023 - 09:51 提交

这篇文章主要介绍了 Verilog 在 FPGA 设计中的概念和使用方法

这篇文章主要介绍了 Verilog 在 FPGA 设计中的概念和使用方法

在FPGA开发调试阶段,经常遇到这样的情况,需要临时添加信号,观察信号变化

本文介绍一些计数器的常用方法和注意点

串并、并串转化也是FPGA设计中常见的基本问题,相对来说比较简单

在本文中,您将了解最常见问题的来源及其解决方案,以及如何将这些思想应用到您的设计中

对于FPGA设计,传统设计都是一个FPGA一个设计,产生一个Bit文件。这就是完整bit文件(full bit)

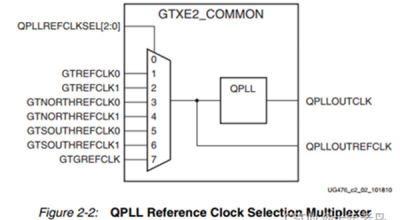

从IP核的时钟配置来学习transceiver的参考时钟架构细节

在FPGA的设计中,不可避免的会用到FIFO和RAM这2个基本单元

本文就跟大家分享如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法。

本文介绍使用coe初始化xilinx fpga ram和使用mif文件初始化intel fpga ram的方法。