ZYNQ+Vivado2015.2系列(十五)AXI Timer 用户定时器中断控制LED

judy 在 周一, 01/21/2019 - 09:47 提交

前面的中断学习中我们学了按键,GPIO,Timer,是时候把它们整合到一起了。今天我们混合使用PS/PL部分的资源,建立一个比较大的系统

前面的中断学习中我们学了按键,GPIO,Timer,是时候把它们整合到一起了。今天我们混合使用PS/PL部分的资源,建立一个比较大的系统

前面我们介绍了按键中断,其实我们稍作修改就可以用按键控制LED了。做个小实验,两个按键分别控制两个led亮灭。

板子:zc702。

硬件部分

添加zynq核:

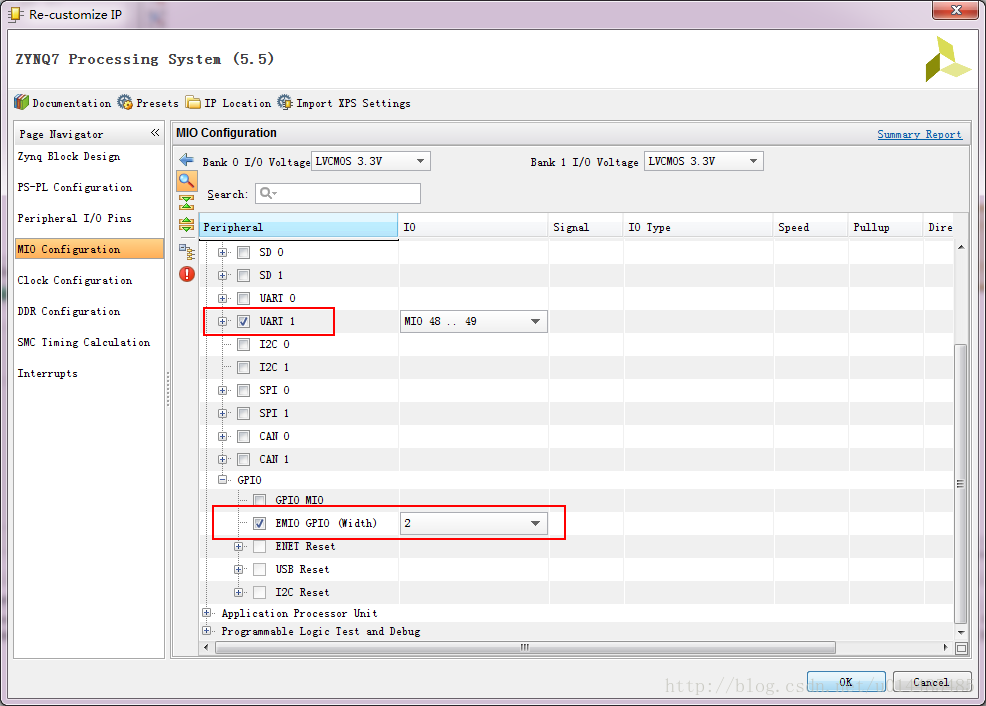

勾选串口用于打印信息,勾选EMIO,我们控制两个led,所以需要2bit

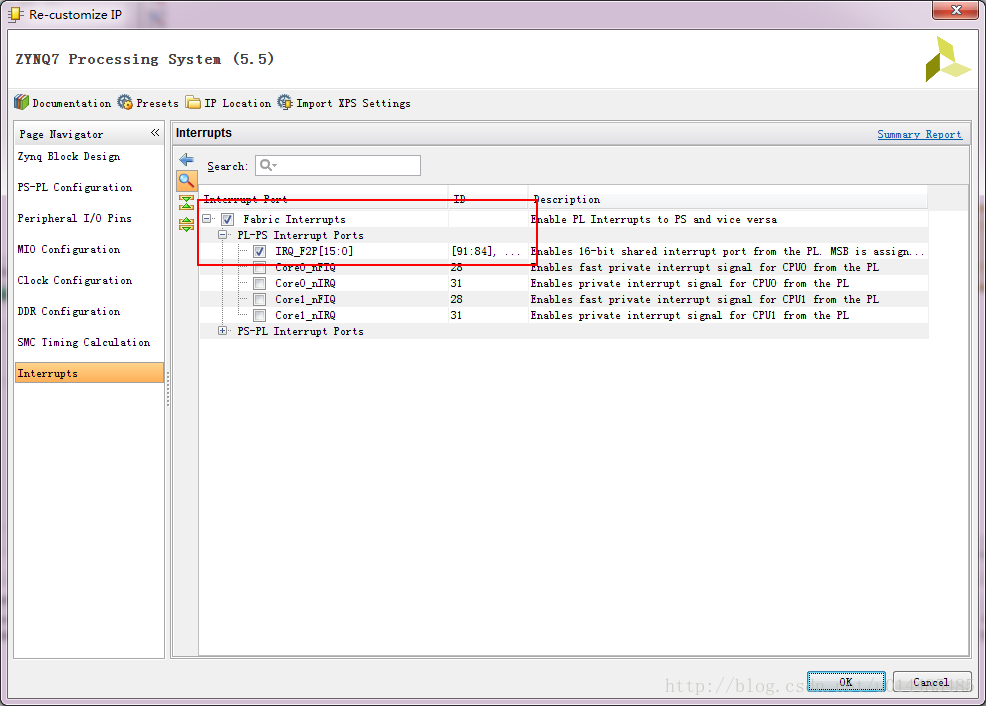

PL 到PS的中断勾选上:

PL时钟什么的都用不到,我们用的按键不需要时钟,EMIO属于PS。

再添加一个concat IP用于合并两路按键信号:

私有定时器属于PS部分,定时器可以帮我们计数、计时,有效的控制模块的时序。这一次实验我们认识定时器并使用定时器产生中断。

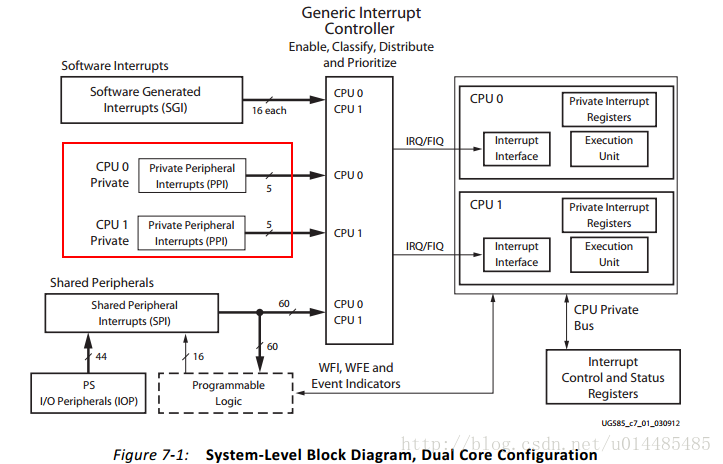

CPU的私有中断(PPI),5个:全局定时器, 私有看门狗定时器, 私有定时器以及来自 PL 的 FIQ/IRQ。

它们的触发类型都是固定不变的, 并且来自 PL 的快速中断信号 FIQ 和中断信号 IRQ 反向, 然后送到中断控制器因此尽管在ICDICFR1 寄存器内反映的他们是低电平触发,但是 PS-PL 接口中为高电平触发。

CPU的私有定时器:每个CPU都有自己的私有定时器:

私有定时器的工作频率是CPU的一半(频率仅供参考,主要看频率分配比率):

PS和PL之间的交互,怎么都逃不过中断,稍微大型的数字系统,PS和PL之间配合使用就需要中断作为桥梁。本文通过按键发起中断请求尝试学习PL请求中断的处理机制。

Block RAM是PL部分的存储器阵列,为了与DRAM(分布式RAM)区分开,所以叫块RAM。ZYNQ的每一个BRAM 36KB,7020的BRAM有140个(4.9M),7030有265个(9.3M),7045有545个(19.2M)。每一个BRAM都有两个共享数据的独立端口,当然是可以配置的,可用于片内数据缓存、FIFO缓冲

前面我们介绍过EMIO,但是不详细。MIO是PS的IO接口,这个M代表的是Multiuse,也就是多用途,在下图中我们可以看到54个MIO连接这么多东西,必须得复用,所以当我们开发的时候需要的功能配置上,不需要的去掉,防止IO口被占用

上一节我们体验了一把PS和PL是怎样联合开发的,这种ARM和FPGA联合设计是ZYNQ的精华所在。这一节我们实现一个稍微复杂一点的功能——测量未知信号的频率,PS和PL通过AXI总线交互数据,实现我们希望的功能。

如何测量数字信号的频率

最简单的办法——在一段时间内计数

在我们设定的时间(Tpr) 内对被测信号的脉冲进行计数, 得Nx, Fx=Nx/Tpr。

Tpr 越大,测频精度越高。这种方法适合于高频信号,因为这里可能会有一个被测信号周期的误差,测量高频信号时误差小。

另一个变种——在一个周期内计数

在 被测信号一个周期内对基准时钟信号计数,得Nx, 基准时钟周期为T, 则Tx=T*Nx, Fx=1/Tx。

被测信号频率越低, 基准时钟频率越高,测量精度越高。因此这种方法适用于低频信号。

二者结合——多个周期同步计数

上一节我们观察了AXI总线的信号,了解了基于AXI总线读写的时序,这一节我们继续探索基于AXI总线的设计,来看一看ZYNQ系列开发板的独特优势,PS可以控制PL产生定制化的行为,而不需要去动硬件代码。

前面一节我们学会了创建基于AXI总线的IP,但是对于AXI协议各信号的时序还不太了解。这个实验就是通过SDK和Vivado联合调试观察AXI总线的信号。由于我们创建的接口是基于AXI_Lite协议的,所以我们实际观察到是AXI_Lite协议的信号时序。

FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门开发基于总线的系统。

使用的板子是zc702。

AXI总线初识: