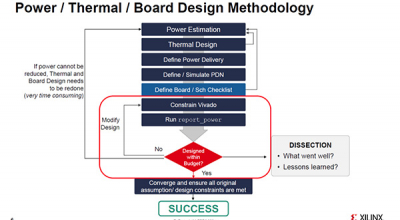

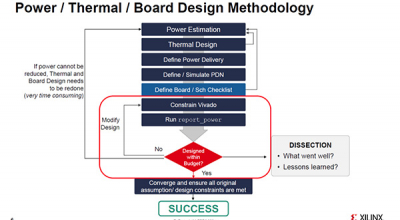

设计收敛技巧:正确使用功耗估算

judy 在 周三, 04/14/2021 - 09:32 提交

4月23日,Xilinx Adapt China:Vivado专场的第二天,赛灵思 Vivado专家团将带来连续三场的“设计收敛”技巧分享。从如何提高QoR(结果质量)的方法技巧、解决接受的时序问题工具,到功耗约束的最佳实践,诚意满满,技术干货一应俱全。

4月23日,Xilinx Adapt China:Vivado专场的第二天,赛灵思 Vivado专家团将带来连续三场的“设计收敛”技巧分享。从如何提高QoR(结果质量)的方法技巧、解决接受的时序问题工具,到功耗约束的最佳实践,诚意满满,技术干货一应俱全。

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建输入输出接口的约束,整理出了一套非常实用的InputDelay/Output Delay Constraints Language Templates。

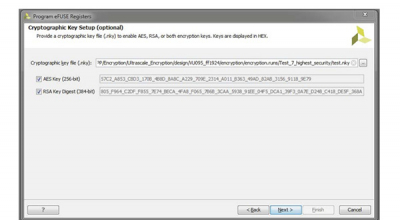

本文描述了使用 Vivado® 设计套件生成加密位流和加密密钥的分步过程。

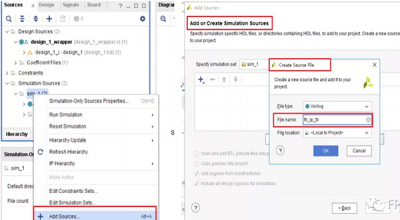

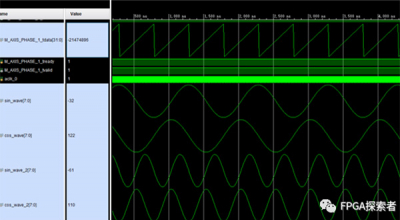

本讲使用两个 DDS 产生待滤波的信号和matlab产生带滤波信号,结合 FIR 滤波器搭建一个信号产生及滤波的系统,并编写 testbench 进行仿真分析,第五讲、第六讲开始编写 verilog 代码设计FIR滤波器,不再调用IP核。

本讲使用matlab产生待滤波信号,并编写testbench进行仿真分析,在Vivado中调用FIR滤波器的IP核进行滤波测试,下一讲使用两个DDS产生待滤波的信号,第五讲或第六讲开始编写verilog代码设计FIR滤波器,不再调用IP核。

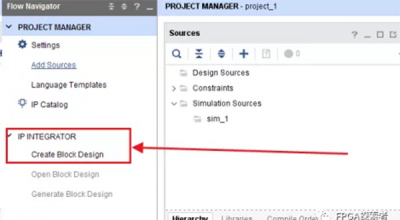

本讲在Vivado调用FIR滤波器的IP核,使用上一讲中的matlab滤波器参数设计FIR滤波器,下两讲使用两个DDS产生待滤波的信号和matlab产生带滤波信号,结合FIR滤波器搭建一个信号产生及滤波的系统,并编写testbench进行仿真分析

4月22日-23日,赛灵思举办 Adapt China:Vivado专场,特邀Vivado专家团队,与您分享 Vivado 在设计自动化集成、IP子系统复用和加速设计收敛等方面的方法和技巧。

因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

本视频着重介绍了 Vivado Design Suite 2020.2 版中的新增功能,包括操作系统和器件支持、高级别增强功能以及加速设计集成、实现与验证相关的各项改进措施。

本次使用Vivado调用DDS的IP进行仿真,并尝试多种配置方式的区别,设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。