Vivado IP中的Shared Logic到底是干嘛的?

judy 在 周五, 09/17/2021 - 15:29 提交

在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的设置中,都会有个Shared Logic的页面。可能很多同学并没有很关注这个页面,直接默认设置就完事了。但其实这个页面的内容也是非常有用的,我们可以看到页面中有两个选择:

在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的设置中,都会有个Shared Logic的页面。可能很多同学并没有很关注这个页面,直接默认设置就完事了。但其实这个页面的内容也是非常有用的,我们可以看到页面中有两个选择:

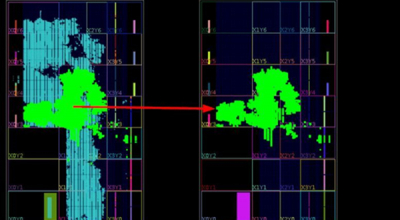

Vivado的Implementation主要有三大步:

opt_design,会生成opt_desgin.dcp

place_design,会生成place_design.dcp

route_design,会生成route_design.dcp

本文记录了Vivado®使用设计运行策略和单个实现命令进行放置和路由的实现功能。详细介绍了用于快速修改现有设计的增量编译流程,以及对信号路由路径进行精确控制的手动路由方法。

本篇博文中的分析是根据真实客户问题撰写的,该客户发现在现场出现罕见的比特翻转, 本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

随着设计复杂度和调用IP丰富度的增加,在调试时序约束的过程中,用户常常会对除了自己设定的约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,我的XDC里面并没有指定set_false_path,为什么有些路径在分析时忽略了?我怎么去定位这些约束是哪里设定的?本文结合一个具体案例,阐述了如何追溯同一时钟域内partial false path的来源,希望为开发者的设计调试提供一些技巧和窍门。

本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado。

在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分析时序问题的原因, 并根据时序失败的原因调整Vivado各个步骤的选项。有时我们也需要调整Vivado各个步骤的选项做不同方向的优化。

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整设计中提取目标模块、对其进行布局规划、约束,然后通过实现工具来运行这些模块,以判断是否能够独立达成时序收敛。

本视频将探讨Vivado IP集成器的特效与优势以及它如何帮助您解决复杂的设计问题。