Vivado之ILA详解

judy 在 周二, 01/05/2021 - 11:04 提交

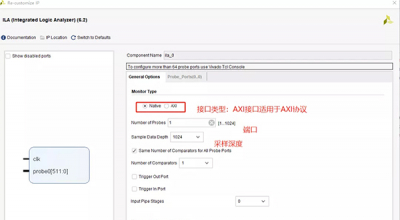

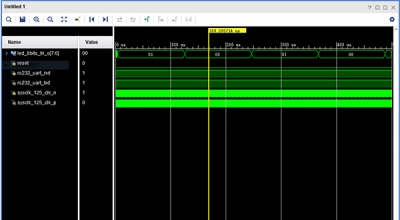

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

我在xdc文件中匹配目标的时候,在可行的情况下更倾向于使用正则表达式。本文就介绍一下我常使用的正则表达式和一些在Vivado中应用的特殊之处,同时也有个别自己尚未解决的问题。

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

本文介绍如何在教程(三)基础上, 关联ELF输出文件并使用vivado对系统进行行为仿真。

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

本文介绍如何导出硬件平台, 并启动SDK开发应用程序及板级支持包(BSP)。

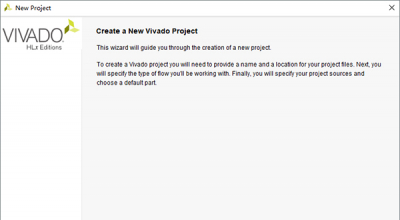

本文介绍如何在 vivado 开发教程(一) 创建新工程 的基础上, 使用IP集成器, 创建块设计。

本文主要介绍如何使用Vivado 开发套件创建硬件工程。

并不局限于Vivado一种EDA。头文件主要使用“文件包括”处理,所谓"文件包含"处理是一个源文件可以将另外一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。Verilog语言提供了`include命令用来实现"文件包含"的操作。

在vivado中 ,如何查看各个模块的资源占用情况呢?方法如下: