作者:falwat

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/falwat/article/details/85918300

本文介绍如何在 vivado 开发教程(一) 创建新工程 的基础上, 使用IP集成器, 创建块设计。

创建基本的MicroBlaze系统

点击Vivado 左侧流程导航器中的"IP INTERGRATOR" 下的 "Create Block Design".

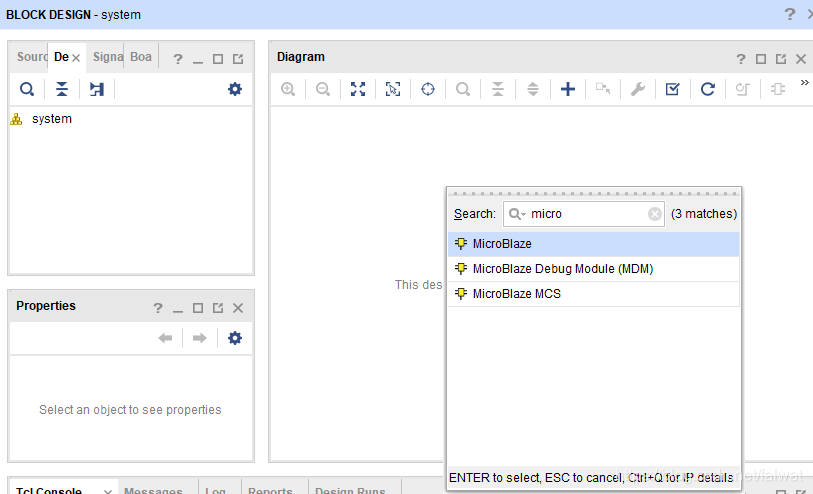

点击"Diagram"中心的"+", 或者使用快捷键"Ctrl+I", 或者右键选择菜单"Add IP", 选择"MicroBlaze" ,双击加入到块设计中.

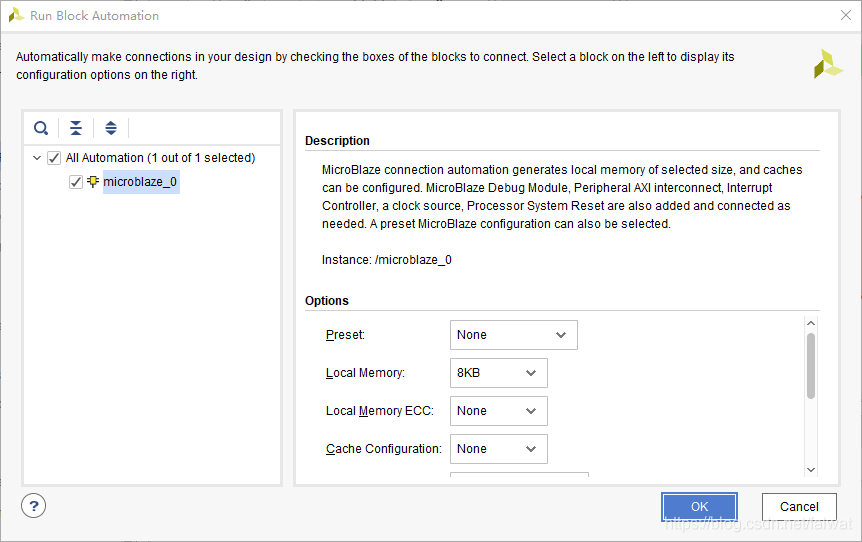

点击"Diagram"窗口中的"Run Block Automation", 运行块自动化. 在弹出的对话框中,根据需要修改选项, 这里先不做任何修改, 点击"OK"完成.

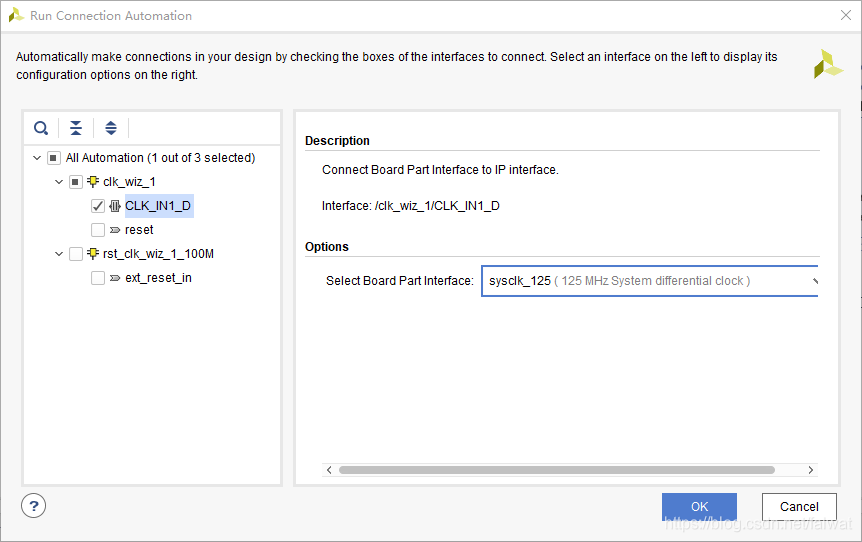

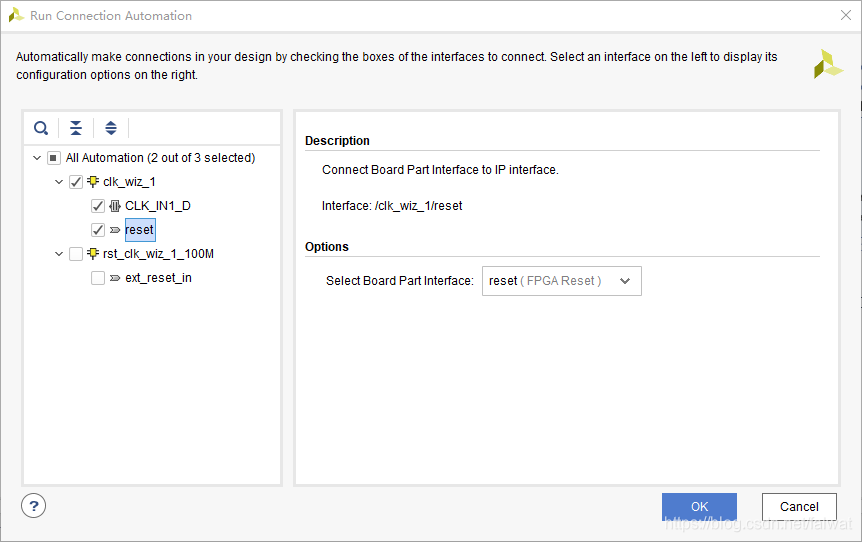

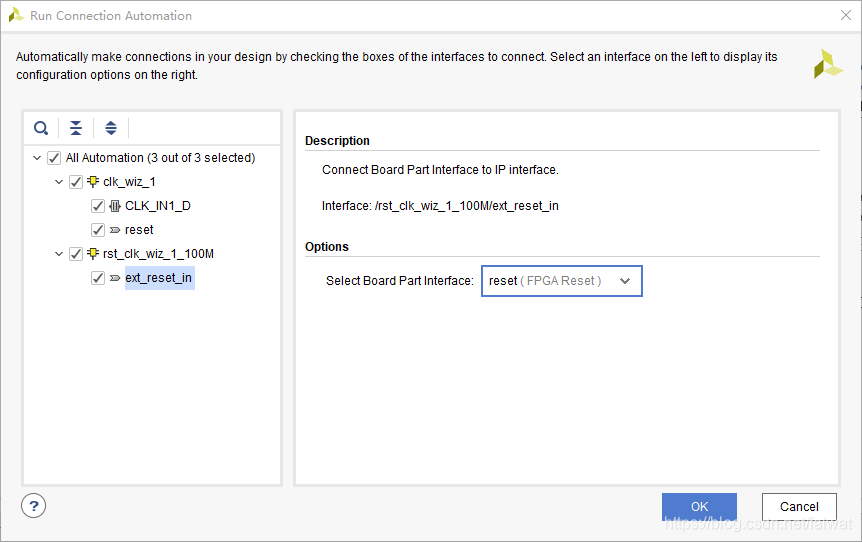

继续点击"Diagram"窗口中的"Run Block Automation", 运行块自动化, 设置时钟和复位信号.

在"Diagram"窗口中,右键选择菜单"Regenerate Laout", 重新生成布局, 如下图所示:

添加外设

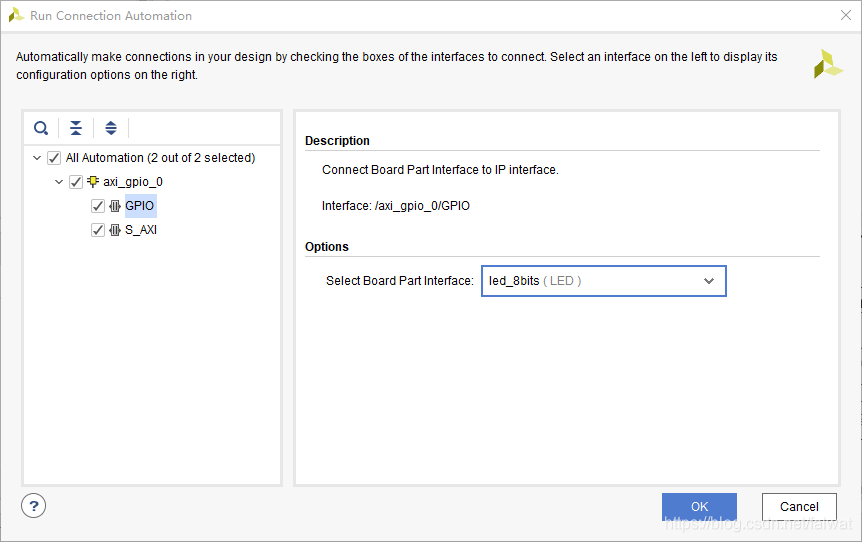

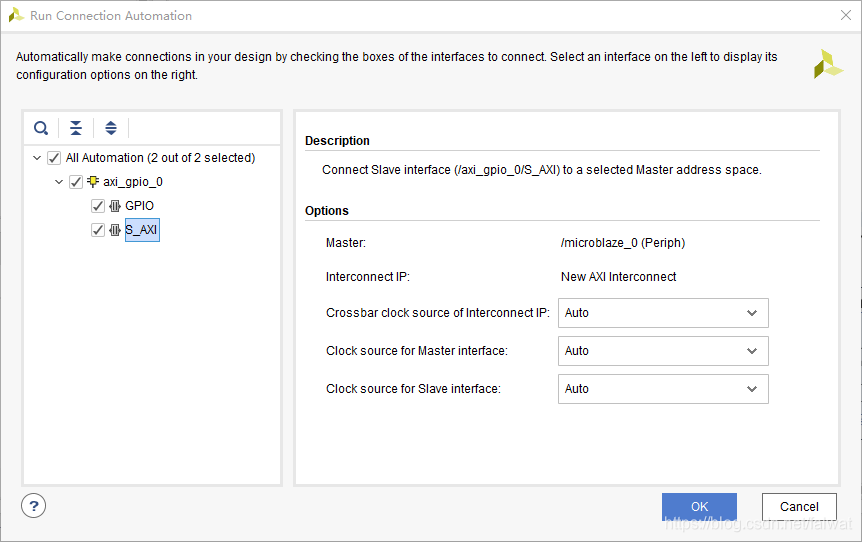

在"Diagram" 窗口中添加"AXI GPIO" IP核, 点击"Diagram"窗口顶部的"Run Connection Automation", 运行连接自动化. 按下图进行配置, 配置完成后, 点击"OK".

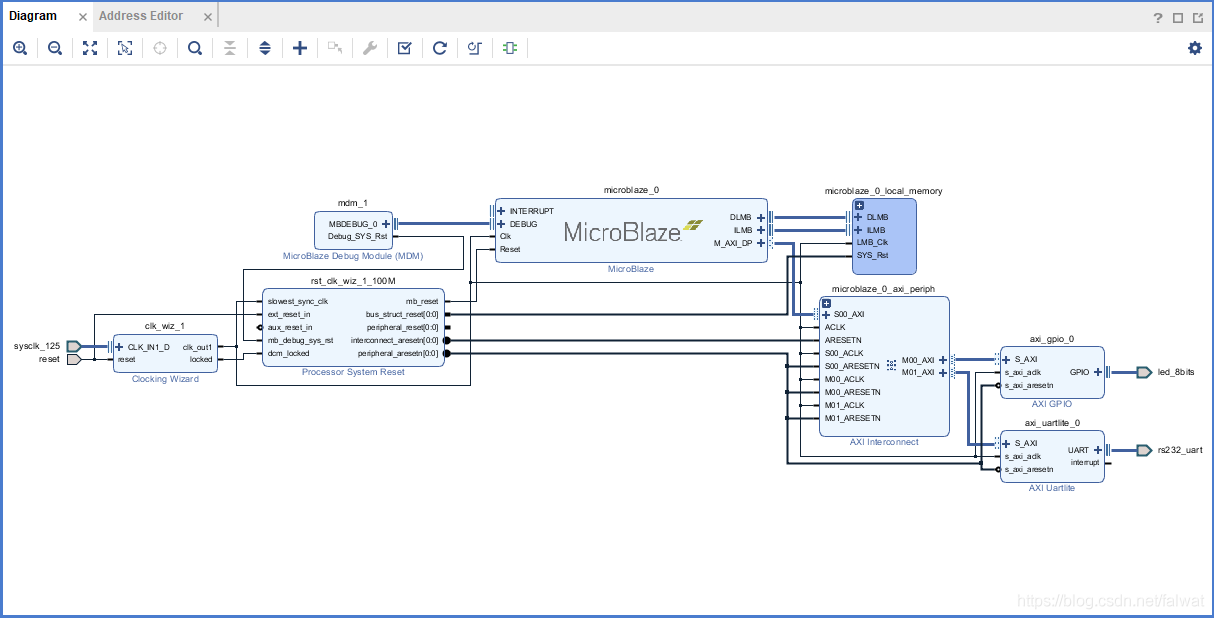

在"Diagram"窗口中,右键选择菜单"Regenerate Laout", 重新生成布局, 如下图所示:

按照上面的步骤,继续添加串口IP("AXI Uartlite").

在"Diagram"窗口中,右键选择菜单"Validate Design" 或使用快捷键"F6", 验证设计. 验证通过后, 关闭"Block Design" 窗口.

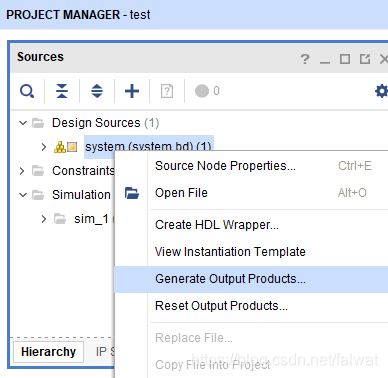

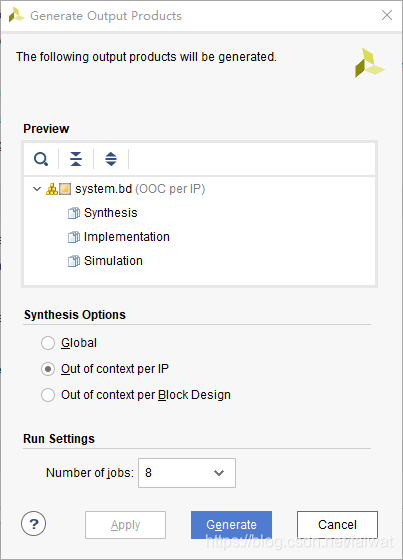

生成输出产品(Generate Output Products)

切回工程管理("PROJECT MANAGER" )视图, 在 "system(system.bd)"上右键选择菜单"Generate Output Products", 生成输出产品.

在弹出的对话框中,设置并行运行数量(Number of jobs), 点击"Generate" 按钮, 等待生成完成.生成过程中, 内存占用和CPU占用会急剧飙升.

创建HDL包装(HDL Wrapper)

在 "system(system.bd)"上右键选择菜单"Create HDL Wrapper". 在弹出的对话框中,点击"OK"即可, 生成的"system_wrapper"会自动被设置为顶层.