作者:Jackie Gao,AMD工程师;来源:AMD开发者社区

简介

在诸多的官方Versal开发板中,默认的工程均是以NoC集成的DDRMC这种硬核器连接DDR。本文介绍在VHK158开发板上,如何使用Versal Soft Memory Controller,替代默认的NoC方案。

制作步骤

根据ug1611-VHK158 Evaluation Board User Guide,我们可以看到VHK158开发板上的两个RDIMM插槽分别连接至如下两个triplet.

Two DDR4 interfaces (1x64-bit 16 GB RDIMM each)

XPIO triplet 1 (banks 700, 701, 702)

XPIO triplet 2 (banks 703, 704, 705)

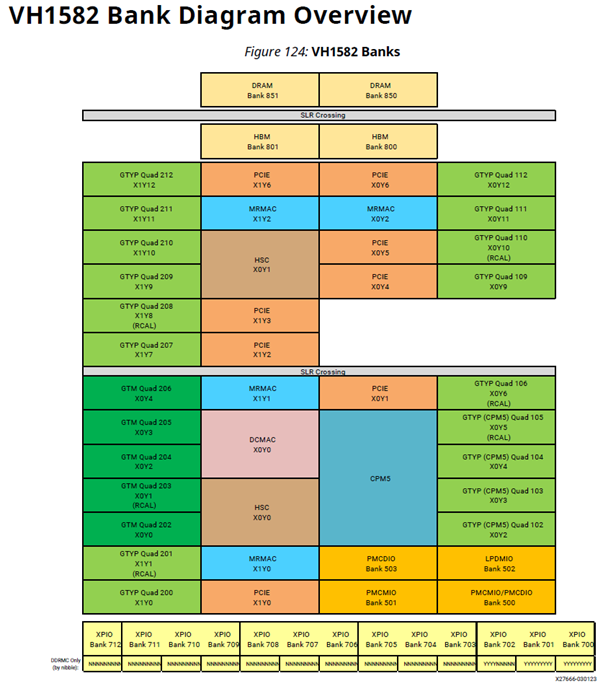

查询文档am013-versal-pkg-pinout,找到VH1582的Block Diagram如下,

可以看到BANK 700, 701, 702是DDRMC only,因此无法使用Versal Soft Memory Controller的方案。而BANK 703, 704, 705并无些限制。因此我们可以在这个RDIMM上使用PL DDR控制器。

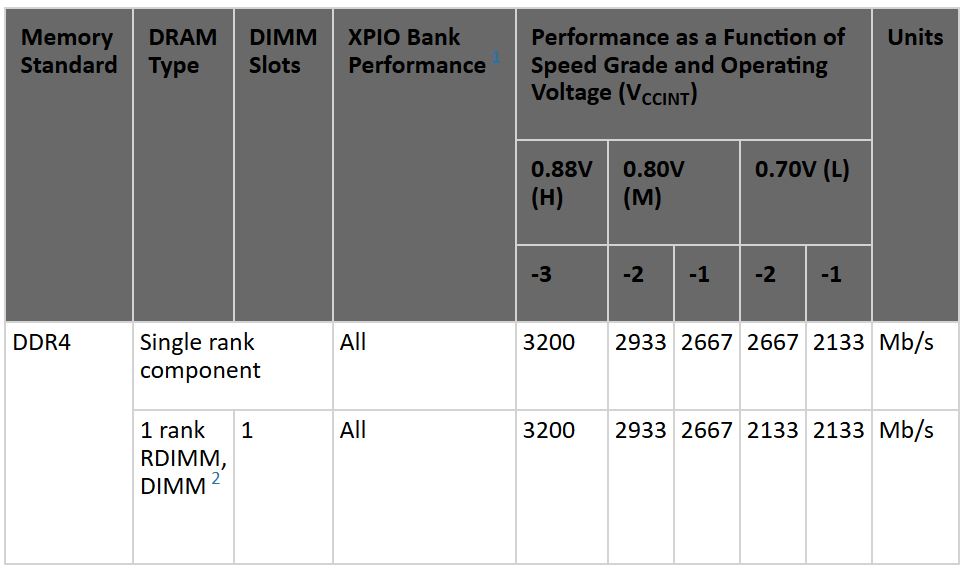

查询文档ds960- Versal HBM Series Data Sheet: DC and AC Switching Characteristics,可以看到-2器件在Vccint为0.8V的时候,最大支持single-rank的DDR4 RDIMM的speed bins是2933Mb/s。

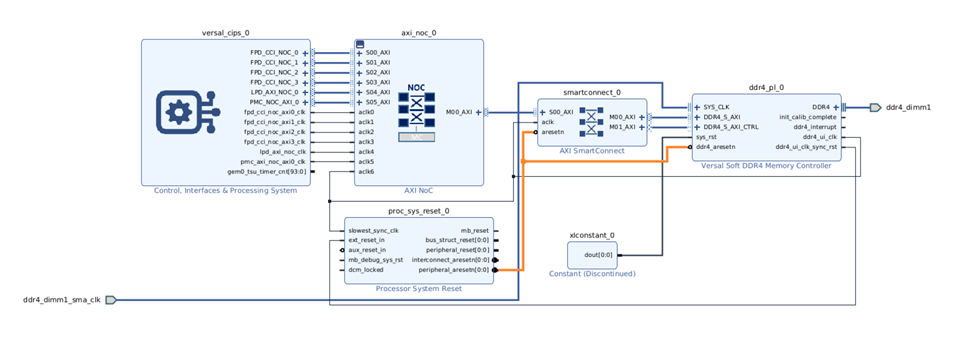

我们选取DDR4-2400模式,基于VHK158创建工程 ,BD如下:

其中,ddr4_pl_0的配置如下:

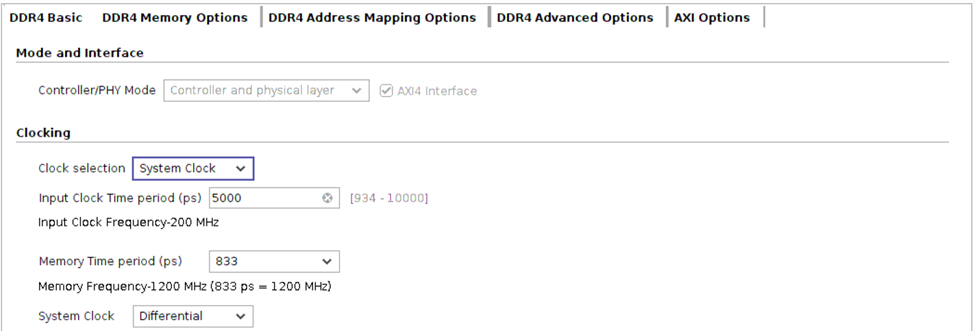

System Clock选择5000ps,对应板上200MHz的参考时钟。

Memory Time period为833ps,对应DDR的频率为1200MHz,速度为2400MHz。

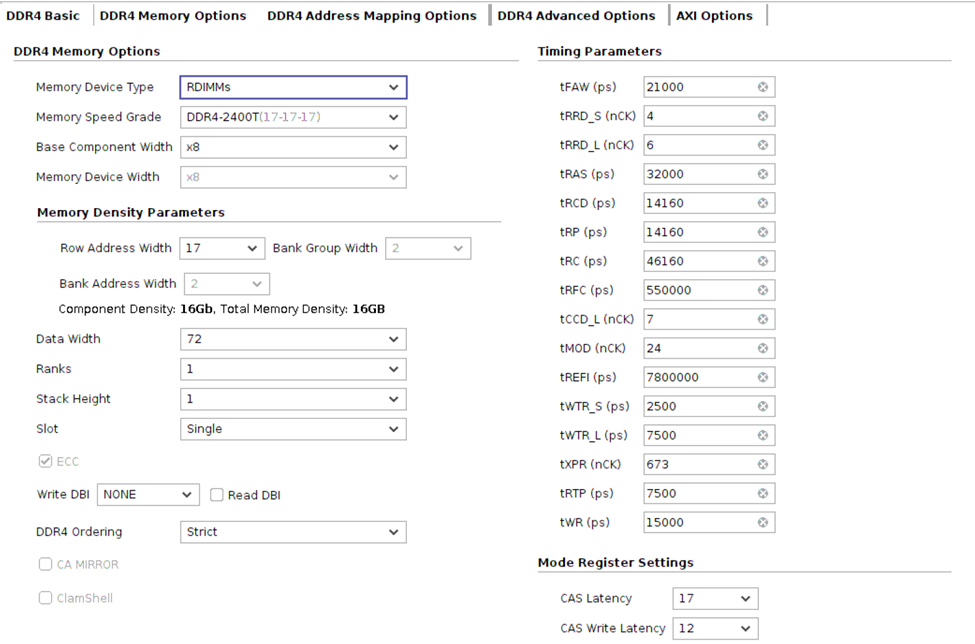

DDR4的详情页面选取RDIMMs和DDR4-2400T(17-17-17)

Write DBI选择为NONE

需要手动添加xdc引脚约束

完整的工程可以在附件中下载。

测试结果

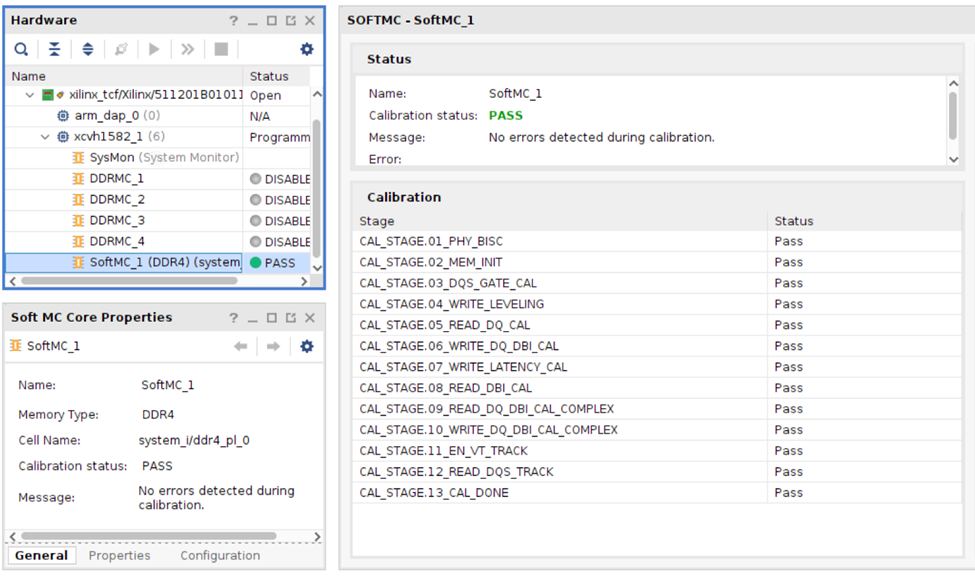

综合实现之后,我们上板测试。下载生成的pdi文件 ,在Vivado是可以 看到DDR校准通过 。

说明Versal Soft Memory Controller在VHK158上测试成功。