作者:Alan Zhang,来源:FPGA FAE技术分享选集

XDMA 是 Xilinx Direct Memory Access 的缩写,是AMD-Xilinx为其FPGA (Field-Programmable Gate Array)产品开发的一种高性能、高带宽的直接内存访问IP核,旨在加速 FPGA 与外部存储器或处理器之间的数据传输。XDMA IP通过减少 CPU 干预来提高数据传输效率,广泛应用于高速数据传输领域。

FPGA 型号:XC7K325T-2FFG900I

Vivado软件版本:2019.2

电脑操作系统:WINDOWS 10

XDMA IP驱动:

Xilinx_Answer_65444_Windows_Files_07022024

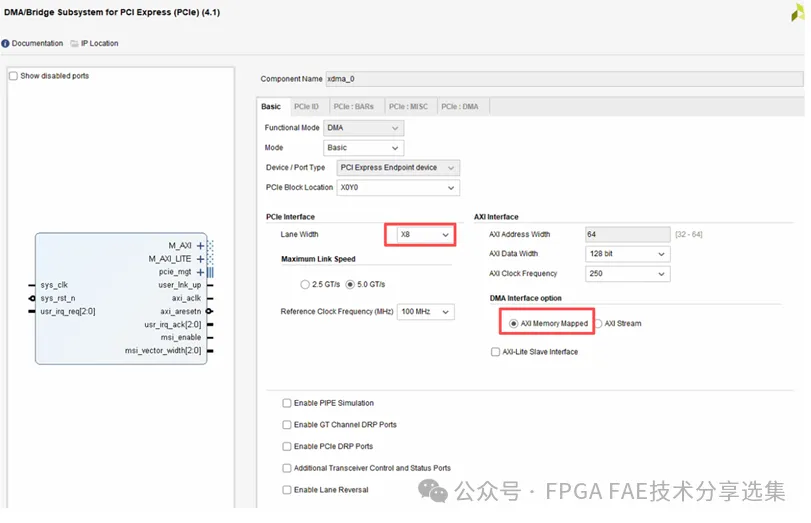

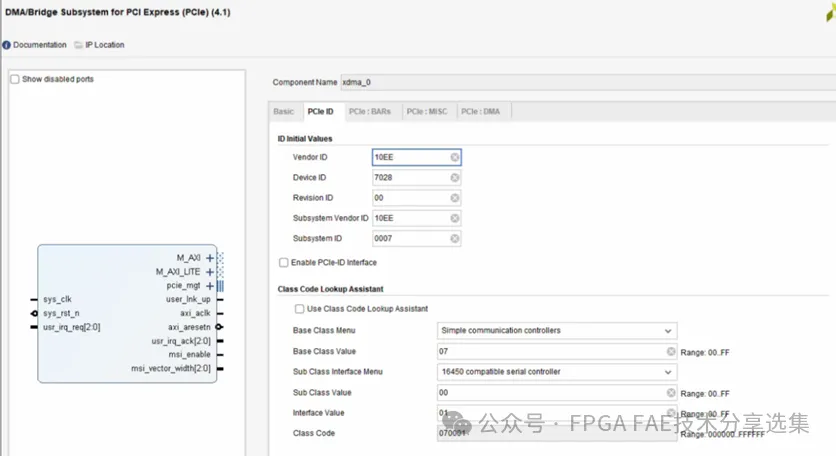

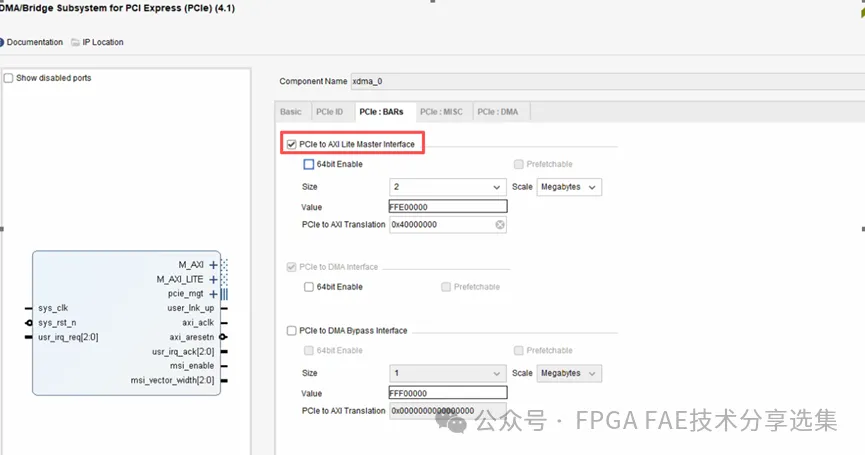

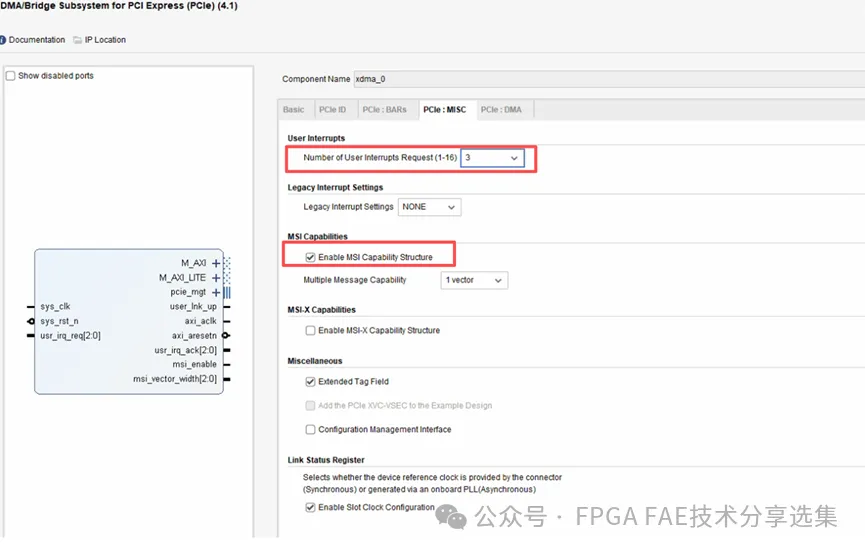

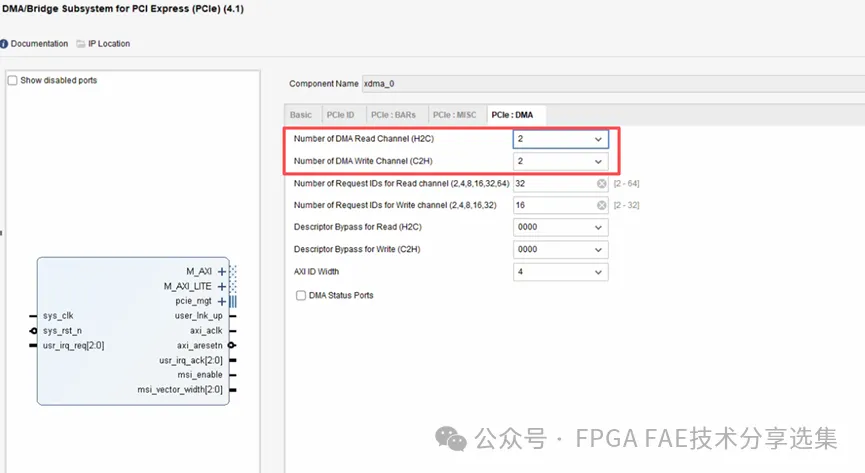

7K325T例化XDMA IP,使用PCIe G2*8,双通道传输,XDMA IP中的各项参数说明,请参考参考Xilinx的文档PG195。

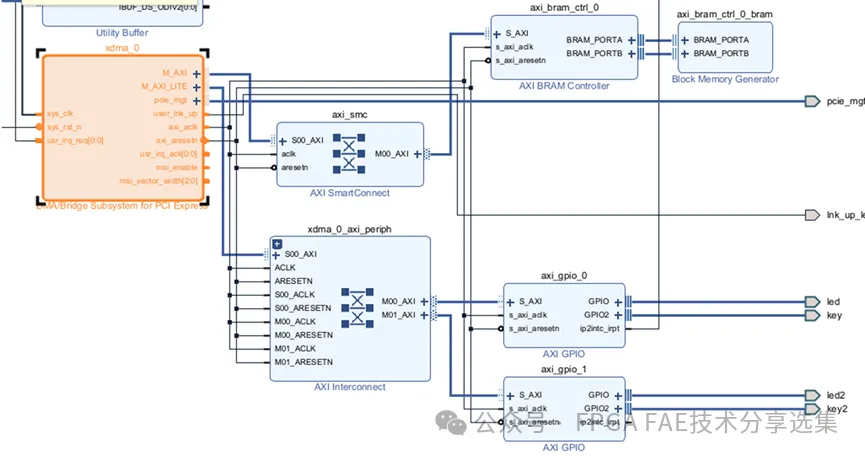

测试工程如下:

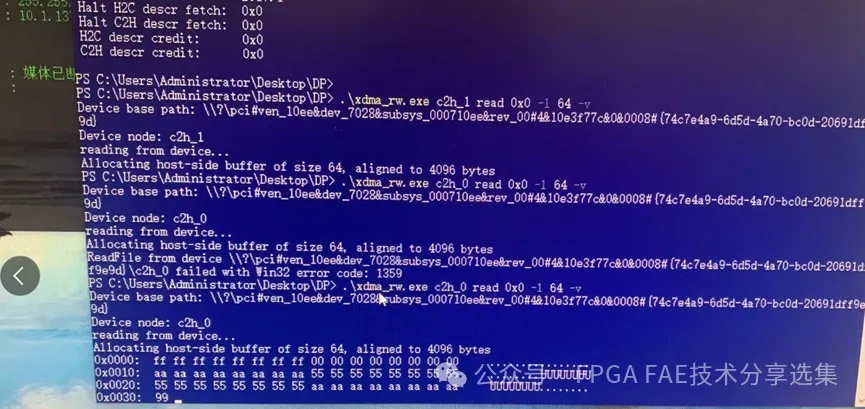

C2H0和C2H1通道读操作结果如下:

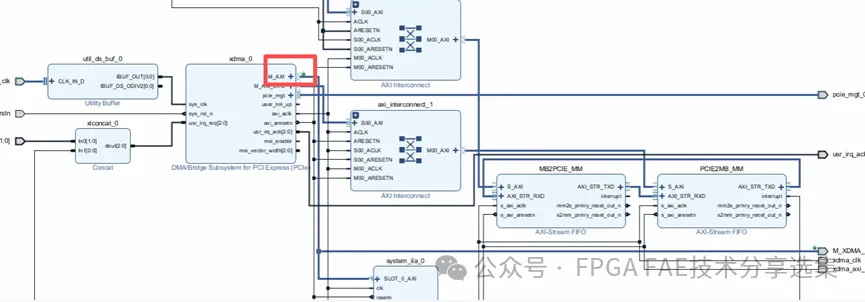

在出问题的Vivado工程中加ila核,抓取进行C2H1通道读操作时AXI总线的信息。

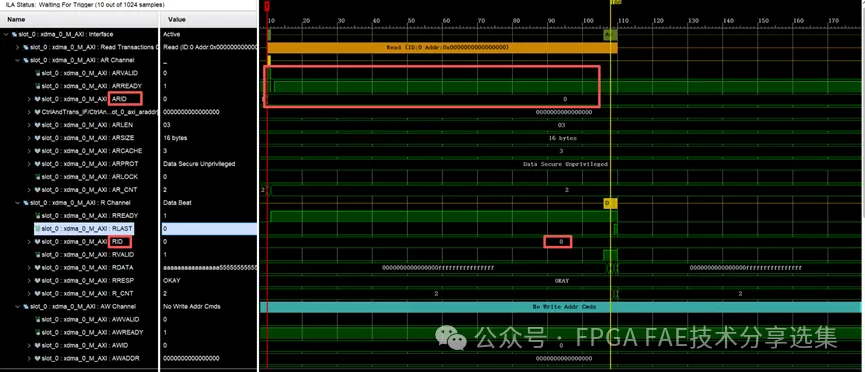

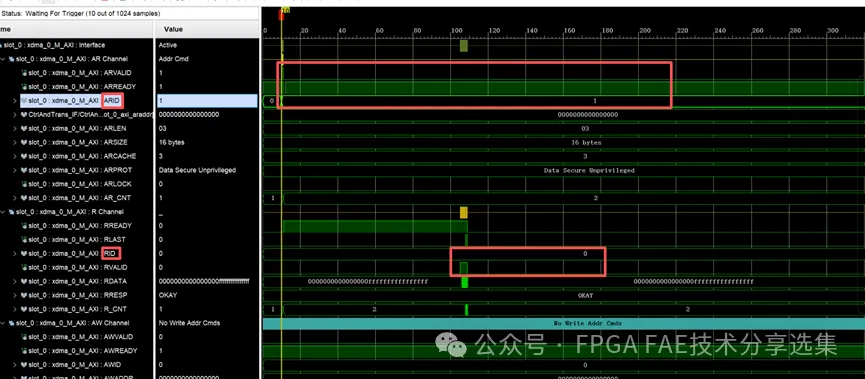

使用ila核抓取C2H0通道和C2H1通道的读时序图,分析C2H0通道的读时序图,在arvalid 为高时,ARID=0,在rvalid 为高时,RID=0,分析C2H1通道的读时序图,在arvalid 为高时,ARID=1,在rvalid 为高时,RID=0,推测ARID与RID的值不一致导致C2H1通道读操作失败。修改与XDMA IP连接的AXI interconnect IP的AXI Slave接口设置,C2H1通道读操作正常。

C2H0通道的读时序图:

C2H1通道的读时序图:

XDMA IP已经被大量客户在设计中使用,工作稳定可靠。在使用XDMA IP遇到问题时,从使用测试例程排查电脑端驱动和添加ila核抓取XDMA IP的信号入手,可以快速定位问题。

感谢AMD-Xilinx专家Huamin Gao、Antony Gu的指导。

如果您在XDMA IP使用方面有问题,欢迎联系: