Vivado除法IP注意事项

joycha 在 周五, 09/04/2020 - 11:36 提交

这篇博客主要记录Vivado中除法IP的注意事项,遇见一些新的知识点应该做相应的笔记。

这篇博客主要记录Vivado中除法IP的注意事项,遇见一些新的知识点应该做相应的笔记。

在本文中,我们将讲解如何在 Vivado® Design Suite 中完成平台准备工作,以便将其用作为 Vitis 中的加速平台。

对 Vivado 和它的前一代设计套件,ISE 做一个组件功能上的平行比较和总结是很有用的。其目的是让那些具有在 ISE 下工作经验 (但是不具有 Vivado 下经验)的人能够更快的适应新工具的各个特性。详细信息见下表。

EDF文件可以直接导入Vivado,而无需Verilog源文件。

好处:

(1) 避免沙雕队友修改源代码,则可以直接提交EDF网表文件。

(2) 避免用户剽窃劳动成果,保护自己的知识产权。

(3) 对于无需更改的设计复用,直接用EDF网表会贼方便。

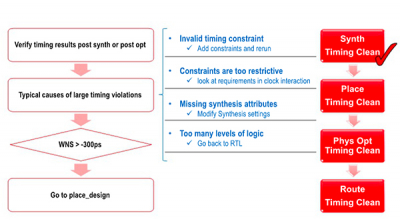

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对其进行了整理,分为了几篇文章。

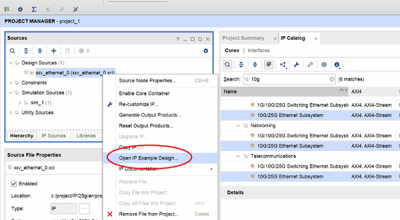

此调试过程亦适用于10G, 25G, 40G, 50G, 100G以太网IP核,每个IP可能会有些细节上的不同,但整个自协商和LinkTraining过程是类似的,可以作为参考。如果是40G/50G, 100G以太网,选的是多通道的IP,务必保证两端的通道0是正确对接上的,因为在做自协商的时候,以太网只使用通道0,其它通道需在自协商完成后再加入工作。

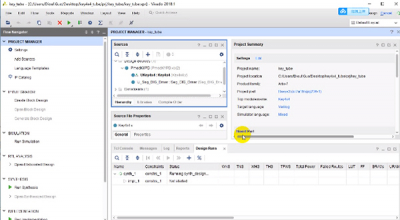

每次创建vivado工程时都会生成大量的文件,这样一方面导致占用的磁盘空间很大,另一方面也不利于vivado工程的copy和github上传等操作。这里教大家一个简单又实用的方法,将工程保存成xxx.tcl,只保留ip ,verilog/vhdl和xdc等必要文件即可。

发生IP核锁定,一般是Vivado版本不同导致的,下面介绍几种方法:

AXI(Advanced extensible Interface)协议主要描述了Master设备和Slave设备之间的数据传输方式,Master设备和Slave设备之间通过握手信号建立连接。当Slave设备的数据准备好时,会发出和维持VALID信号,表示数据有效;当Master设备准备好接收数据时,会发出READY信号。数据只有在这两个信号都有效时才开始传输。

本例程主要使用Vivado 调用ROM IP核,用含有正弦曲线的.coe文件初始化ROM,最终通过仿真实现波形的显示。