AXI的理解

AXI(Advanced extensible Interface)协议主要描述了Master设备和Slave设备之间的数据传输方式,Master设备和Slave设备之间通过握手信号建立连接。当Slave设备的数据准备好时,会发出和维持VALID信号,表示数据有效;当Master设备准备好接收数据时,会发出READY信号。数据只有在这两个信号都有效时才开始传输。

AXI协议(又称AXI4.0)的接口标准

包括3种接口标准:AXI4、AXI-Stream、AXI-lite。

AXI4:适用于要求数据高速传输的场合。

AXI-Stream:如FIFO,数据传输不需要地址,而是主从设备间直接进行数据的读写,主要用于高速数据传输的场合,如视频、高速AD等。

AXI-lite:AXI4-Lite接口是AXI4接口的子集,专用于和元件内的控制寄存器进行通信。AXI4用于单个数据传输,主要用于访问一些低速外设。

AXI接口的5个独立通道

WriteAddress通道、Write Data通道、Write Response通道、Read Address通道、Read Data通道。

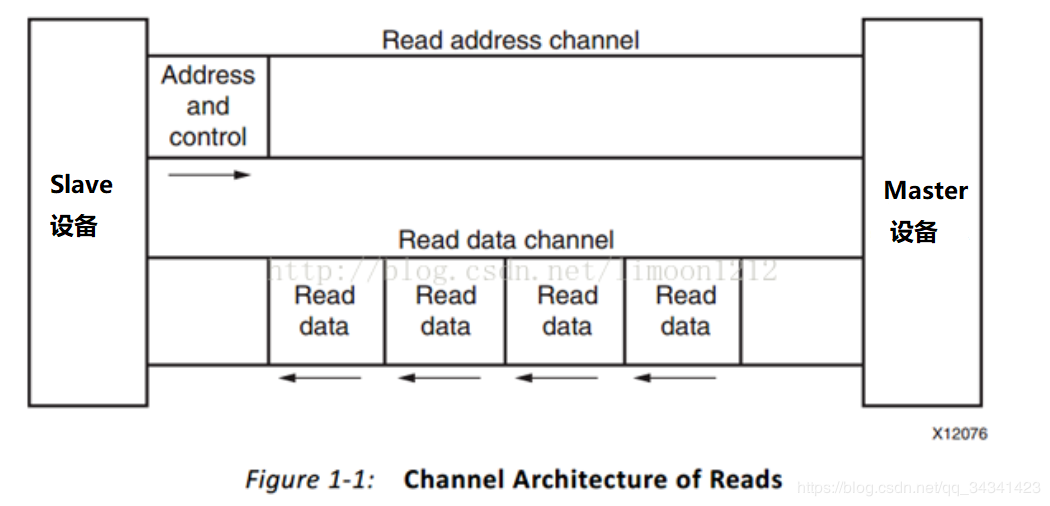

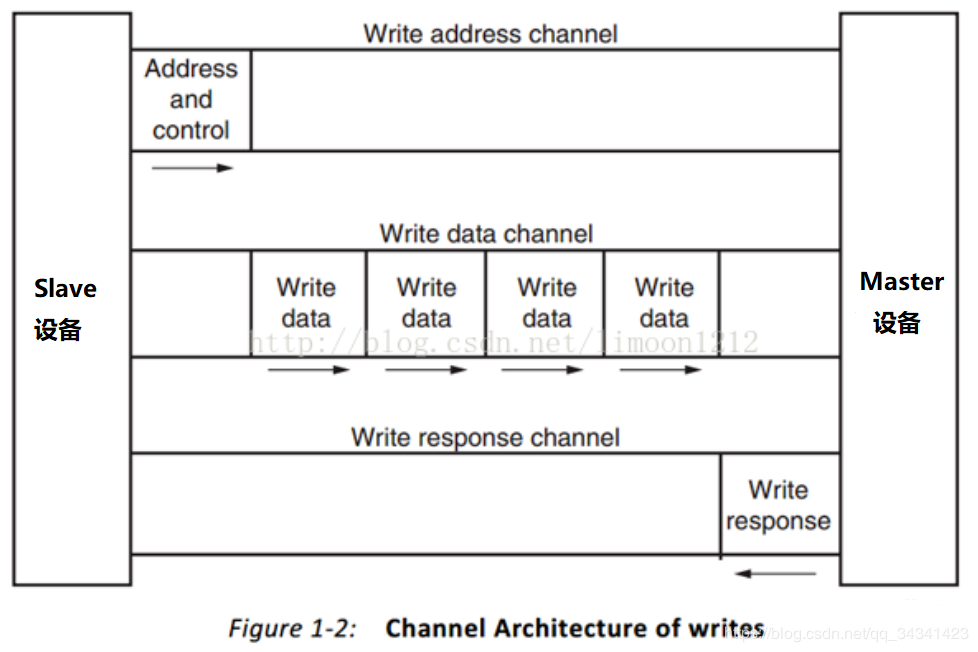

读/写的工作过程

读/写通道并行地进行数据交互,明显提高了数据吞吐量,对写数据,Master设备会返回确认信号,这样可以保证写数据通道的安全,读/写模型分别如图1-1、图1-2。

读模型:Slave设备发送读地址占用信号给从设备→Master设备将数据写入Slave设备,实现读操作。

写模型:Slave设备发送写地址占用信号给Master设备→Slave设备将数据写入Master设备→Master设备回复确认收到信号,实现写操作。

ZYNQ中的AXI接口共9个(包含3个类型),主要用于PS与PL的衔接。

(1) AXI_ACP接口(PS端是Master设备,PL端是Slave设备)

只有1个,又叫加速器一致性端口,适合做专用指令加速器模块接口。PL端(Slave设备)可直接从PS部分(Master设备)的Cache中拿到(读)CPU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至(写)Cache中,延时很小。

(2) AXI_HP接口(PS端是Master设备,PL端是Slave设备)

包括4个,主要用于PL访问(读/写)PS上的存储器。每个接口都有两个FIFO缓冲器,一个是读缓冲,一个是写缓冲。

【实例:设计视频处理时,高清的图像可由FPGA直接完成采集、预处理,然后通过AXI_HP接口将数据高速传输至DDR中,供APU(加速处理器)完成进一步的图像处理】

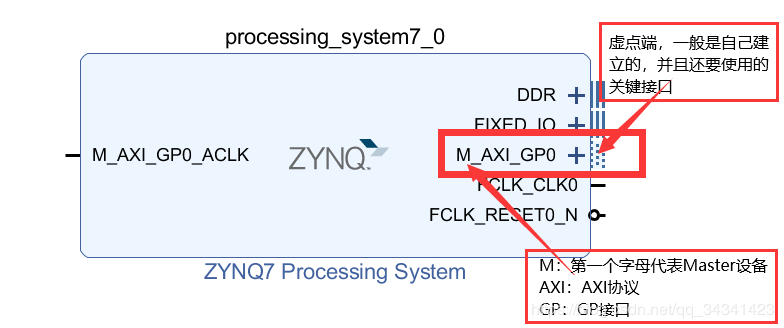

(3) AXI_GP接口

通用AXI接口,总共有4个(包括两个32位主设备接口和两个32位从设备接口)。

可用于控制电机运转(PS端是Slave设备,PL端是Master设备),获取传感器信号(PS端是Master设备,PL端是Slave设备)等逻辑模块的连接接口。

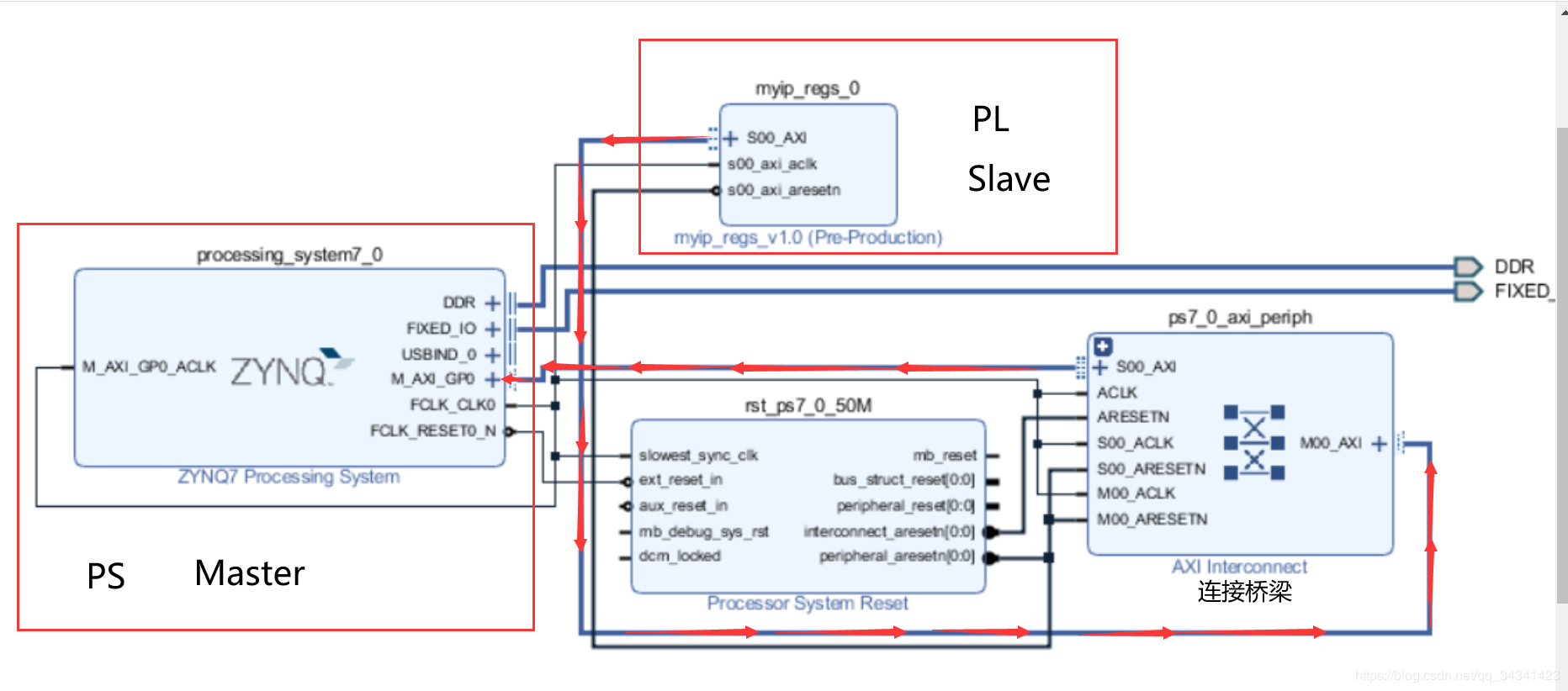

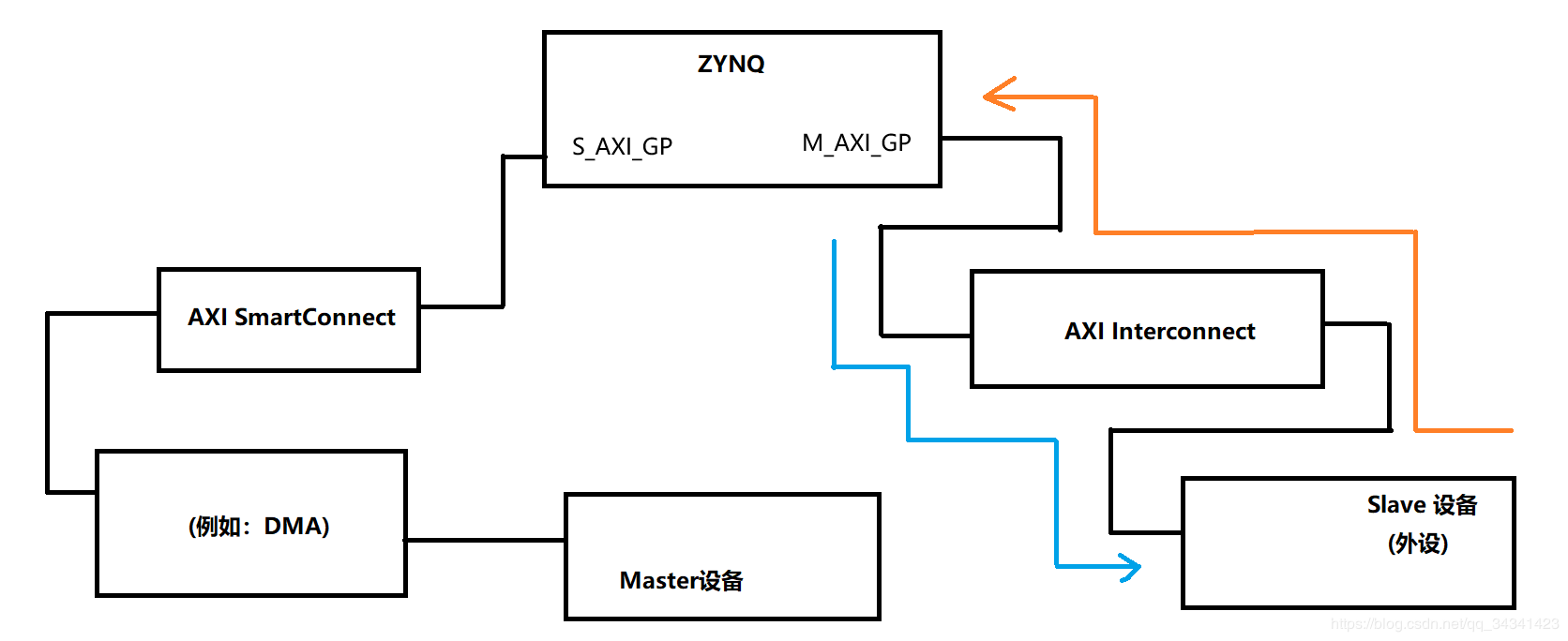

Master设备和Slave设备之间的桥梁

AXI协议严格来讲是一个点对点的主/从接口协议,当需要和多个外设需要互相交互数据时,我们需要加入一个AXI Interconnect模块,也就是AXI互联矩阵,AXI Interconnect的作用是将一个或多个AXI主设备连接到一个或多个AXI 从设备。

注意:AXI Interconnect IP核最多支持16个Master设备和16个Slave设备,如果需要更多的接口可以在设计中加入多个IP核。

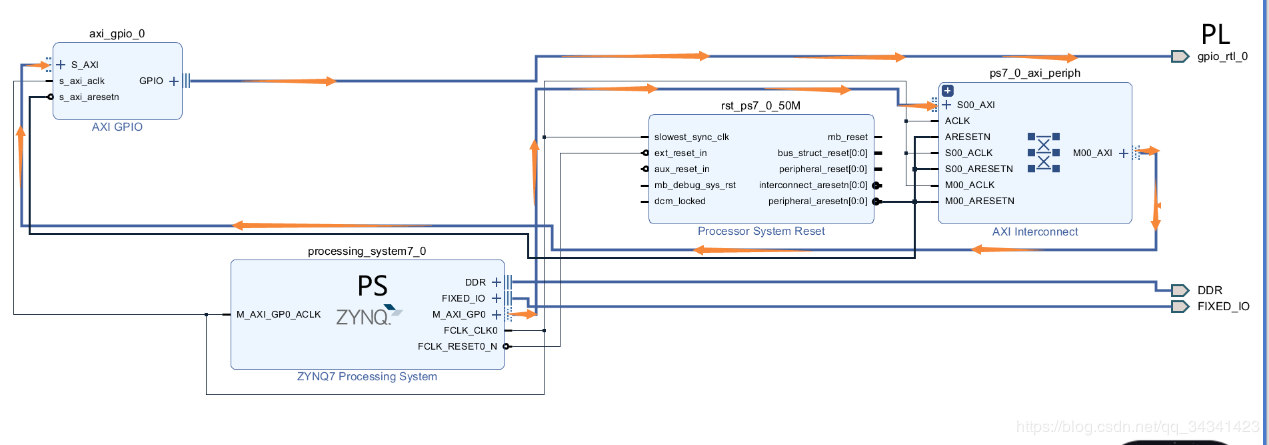

AXI GP接口设置

配置后效果:

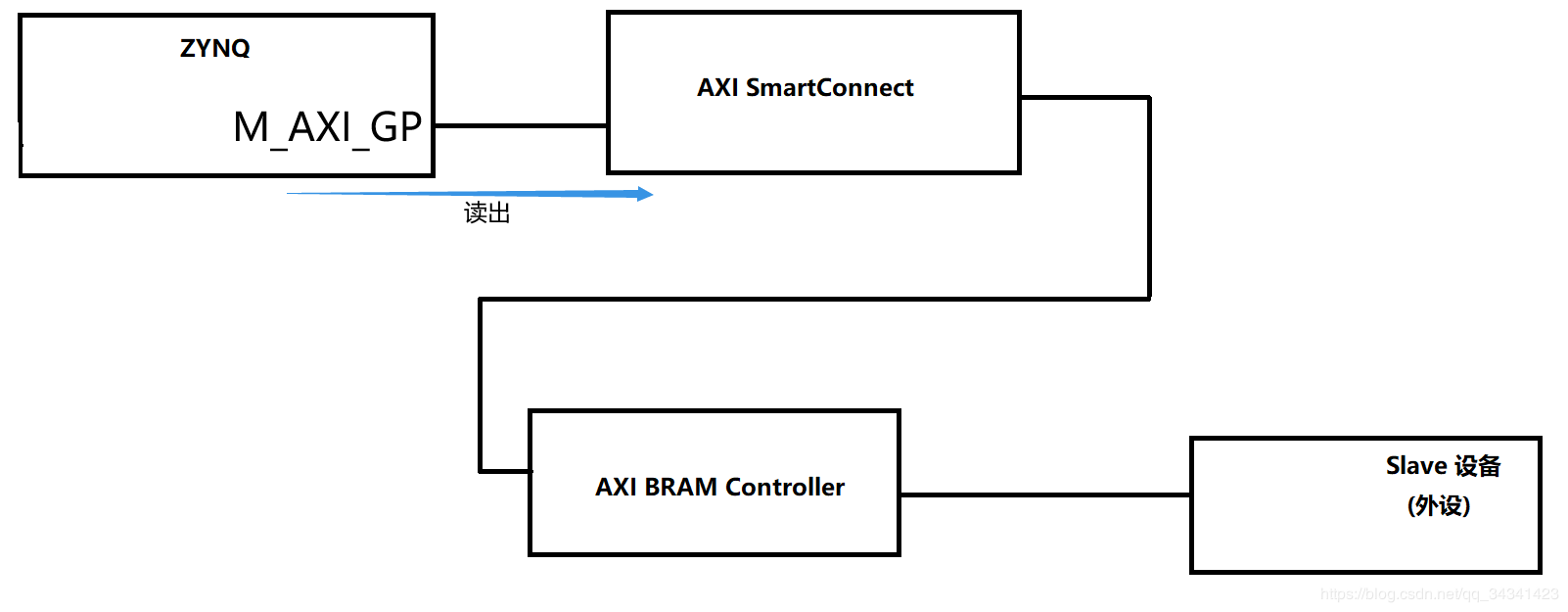

例子1:PS读PL资源(PS是Master设备,PL是Slave设备)

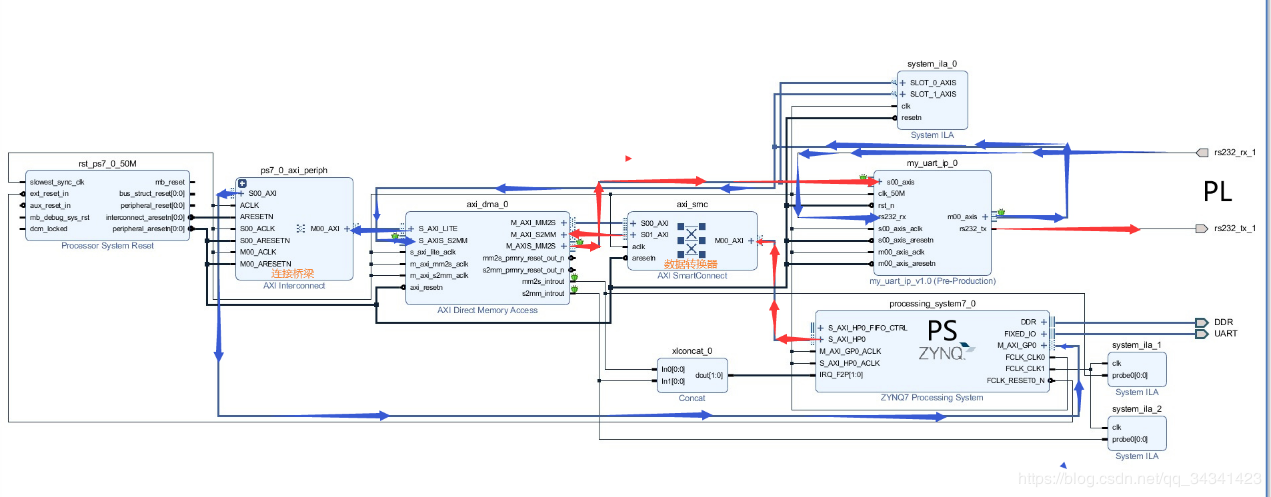

例子2:PL端实现UART功能

功能:在SDK(PS端)里发送数据通过DMA给PL端的UART发送出去。 外部将UART的收发回环,将发送出去的数据再收回来,通过DMA在给PS。

测试硬件框图如下:

例子3:流水灯(PS端作为Master设备)

综述大致流图(简单的连接原理,还有其他情况):

本文转载自: https://blog.csdn.net/qq_34341423/article/details/104792712