【 Vivado 】理解工程模式和非工程模式

demi 在 周四, 02/13/2020 - 12:22 提交

Vivado设计套件有两个主要使用模型:项目模式和非项目模式。 可以通过Vivado IDE或通过Tcl命令和批处理脚本开发和使用项目模式和非项目模式。

Vivado设计套件有两个主要使用模型:项目模式和非项目模式。 可以通过Vivado IDE或通过Tcl命令和批处理脚本开发和使用项目模式和非项目模式。

刚写了一段 Verilog代码,辛辛苦苦花了很长时间综合,在debug的过程中,却找不到需要debug的信号了,查看网表发现没有?这种情况是因为我们的某些中间信号被优化掉了。

FPGA的调试是个很蛋疼的事,即便Vivado已经比ISE好用了很多,但调试起来依旧蛋疼。即便是同一个程序,FPGA每次重新综合、实现后结果都多多少少会有所不同。而且加入到ila中的数据会占用RAM资源,影响布局布线的结果。

下面讲解在vivado中怎么抓一个bit下进去后开始运行的初始事件,即startup trigger。操作起来比较复杂,一般情况下都是让要抓的事件延迟发生或者循环发生,方便调试。

git有多好用我就不用多说了,可谓是程序员必备技能之一。对于一般的软件代码来说,只需把源文件进行git管理即可。但对于FPGA工程师来说,使用git多多少少有几个问题......

本教程介绍了如何使用Vivado®集成开发环境(IDE)构建基本的Zynq®-7000SoC处理器和MicroBlaze™处理器设计。在本教程中,您将使用Vivado IP集成器构建处理器设计,然后使用Vitis™统一软件平台和Vivado集成逻辑分析器调试设计。

xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。

准则1:合适的代码风格

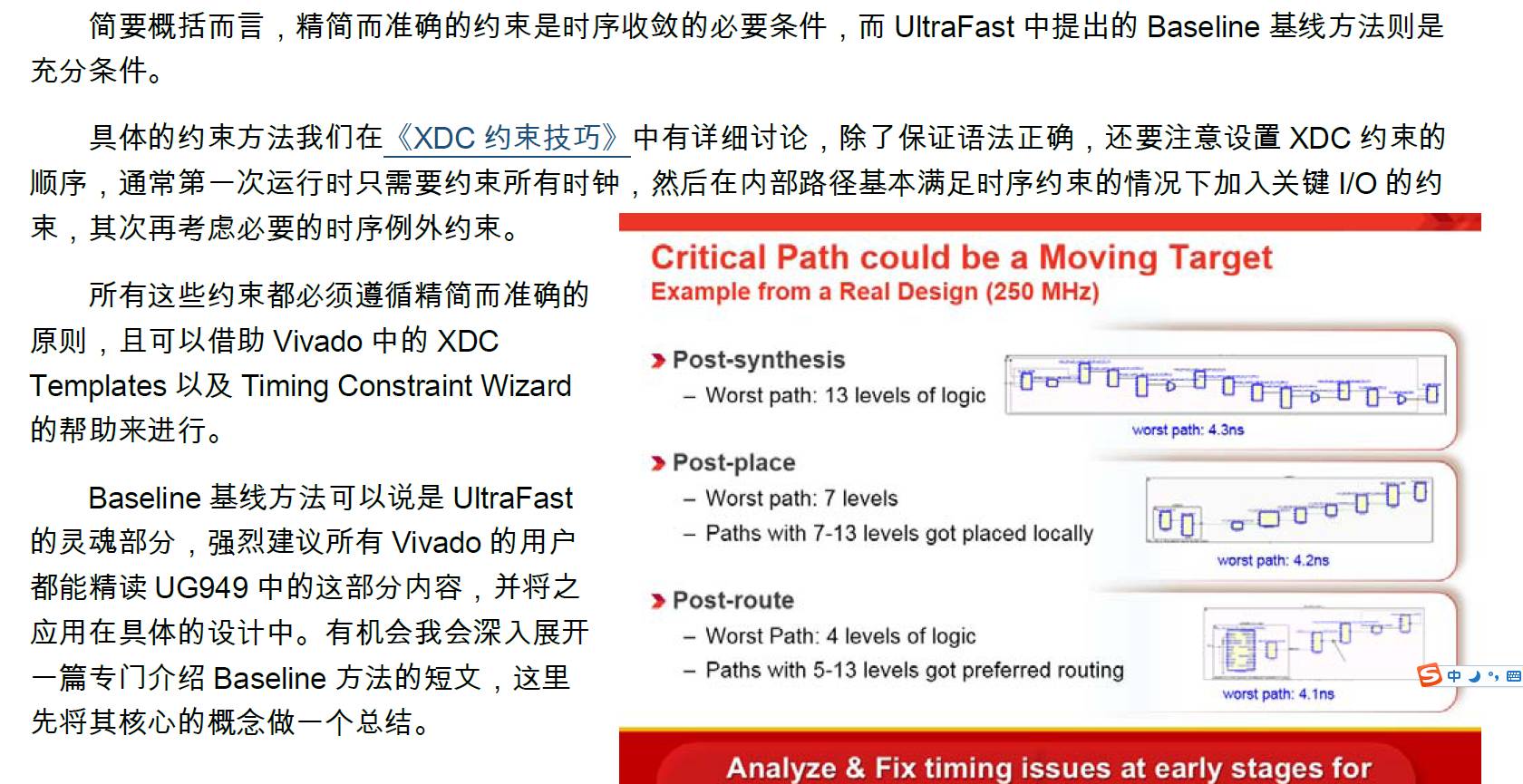

准则2:精准的时序约束

准则3:管理高扇出网络

准则4:层次化设计结构

在 Vivado/ISE 中遇到许可问题时,该怎么办呢?本文介绍了使用不同类型的许可证时可能遇到的不同问题。

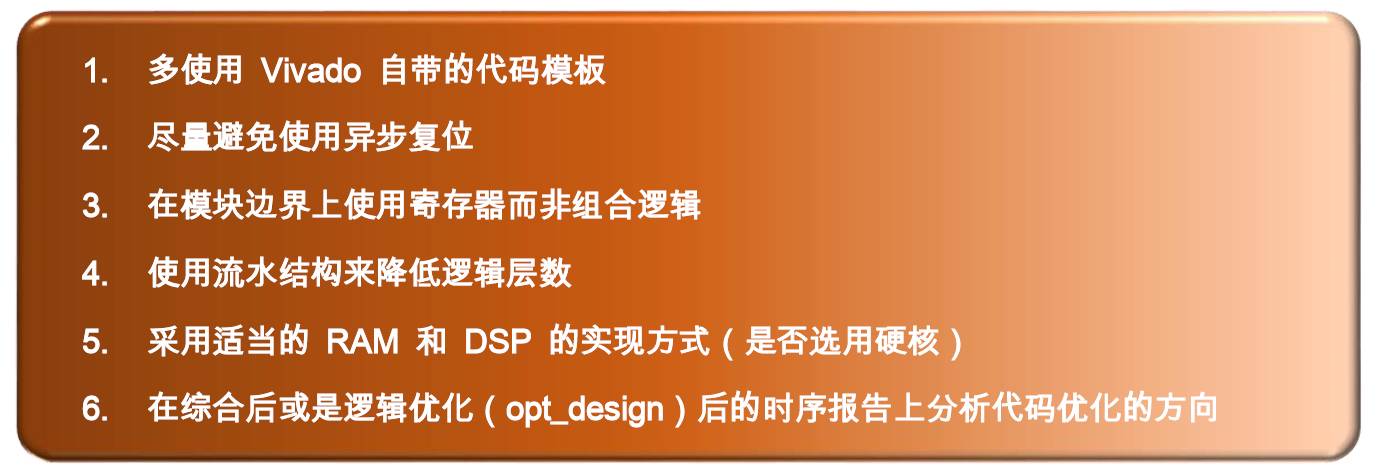

许多 FPGA 设计都难以达成所期望的性能目标。原因不尽相同,以下列出的只是其中部分可能的原因:未遵循 UltraFast 设计方法;时序约束不良;过高资源利用率;控制集过多;未采用最优化时钟设置;逻辑层次过多,难以达成目标性能;布局规划不良;布线拥塞;因约束导致工具优化受限。