作者:OpenSLee,FPGA开源工作室微信公众号

EDF文件可以直接导入Vivado,而无需Verilog源文件。

好处:

(1) 避免沙雕队友修改源代码,则可以直接提交EDF网表文件。

(2) 避免用户剽窃劳动成果,保护自己的知识产权。

(3) 对于无需更改的设计复用,直接用EDF网表会贼方便。

1 vivado write_edif

目的:将当前网络列表导出为EDIF文件。

语法:

write_edif [‑pblocks] [‑cell ] [‑force] [‑security_mode ] [‑logic_function_stripped] [‑quiet] [‑verbose] <file>

[-pblocks]导出这些pblocks的网络列表(对于-cell无效) [-cell]导出此单元格的网络列表(对于-pblocks无效) [-force]覆盖现有文件 [-security_mode]如果设置为“all”,并且某些设计需要加密,则 整个设计将被写入一个单独的加密文件 默认值:多文件 [-logic_function_stripped]将lut和ramb上的INIT字符串转换为固定值 [-quiet]忽略命令错误 [-verbose]在命令执行期间挂起消息限制输出文件(带有-pblocks或-cell的目录)

举例:

write_edif C:/Data/edifOut.edn

2 操作步骤

(1)将需要封装的模块设置为顶层模块

(2)综合或实现需要生成edif的verilog或vhdl源文件。

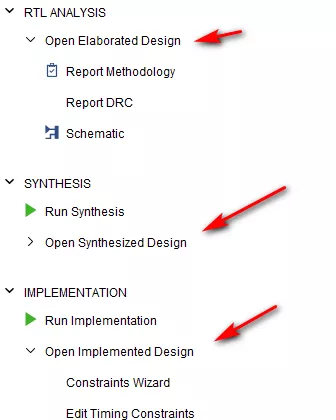

(3)open Elaborated Design or Open Synthesized Design or Open

Implemented Design

(4) tcl console:write_edif xx.edf

(5) tcl console:write_verilog -mode synth_stub xx_stub.v

(6) 调用 xx.edf和xx_stub.v