作者:碎碎思 OpenFPGA微信公众号

特性比较

对 Vivado 和它的前一代设计套件,ISE 做一个组件功能上的平行比较和总结是很有用的。其目的是让那些具有在 ISE 下工作经验 (但是不具有 Vivado 下经验)的人能够更快的适应新工具的各个特性。详细信息见下表。

ISE 和 Vivado 设计套件之间的比较

ISE 和 Vivado 设计套件之间的比较

部分软件工具的变化是很值得注意的,它会导致设计者的工作方法的改变。比如说,ISE 的 Xilinx Platform Studio(XPS) 和 Vivado 的 IP Integrator 都是用于设计嵌入式硬件系统的环境,但是它们的用户界面迥然不同。XPS 使用一系列的下拉列表和基于文本的配置选项,然而 IP Integrator 提供了更加图形化的接口。其他的变化则更加细微,比如说,Vivado 中的综合和布线的引擎相比 ISE 来说由很大的改进,但是这对于用户却是透明的。来获取关于原始的 ISE 设计套件以及 Xilinx 在 Vivado 中对这些开发工具做改进的理由的讨论。

值得重申的是,Vivado 支持 7 系列和 Zynq-7000 以及之后的设备,但是不支持更老的设备(Spartan, Virtex-6 以及之前的 FPGA) 。同样 ,ISE 也不再支持 7 系列之后的设备

ISE 和 Vivado 之间另一个重要的区别就是约束文件的类型。在 ISE 的流程中,使用的是 UCF(.ucf) 文件(User Constraints File, 用户约束文件的首字母缩写) ,然而在 Vivado 中,则使用 XDC(.xdc) 文件 (Xilinx Design Constraints,Xilinx设计约束 )。新的文件类型提供了与工业级集成电路设计约束的兼容性,并且增强了一些特定的 Xilinx 约束文件。XDC 文件使用的约束语法和 UCF 完全不同,因此ISE 的用户需要熟悉这种新的样式。在《Xilinx, Inc., “ISE to Vivado Design Suite Migration Guide”, UG911, v2014.1, April 2014.位于 : http://www.xilinx.com/support/documentation/sw_manuals/xilinx2014_1/ug91...》《Xilinx, Inc., “Vivado Design Suite Tutorial: Using Constraints”, UG945, v2014.1, April 2014.位于 : http://www.xilinx.com/support/documentation/sw_manuals/xilinx2014_1/ug94...》中明确的提供了从 UCF 文件到 XDC文件转换的方法。

System Generator 的用户也会注意到 MATLAB/Simulink 在版本 2012b 中所作的接口升级(这和 ISE 到 Vivado 的升级是相互独立的,不过也非常值得注意)。首先在美观上有了改进,但是其文件类型也有了变化:Simulink 的模型之前使用文件类型 .mdl,现在则默认使用 .slx。新的模型都会自动使用新的文件类型,System Generator 也会完全支持。旧的 .mdl 的模型文件依旧可以被打开,编辑,保存,如果需要的话,新的模型也可以被向后兼容保存成 .mdl 格式。

为了体现Vivado与ISE的开发流程以及性能差异,本文使用了相同的源码、器件,IP核分别用自己软件下的最新版本例化,时钟及管脚约束完全相同。

开发流程:

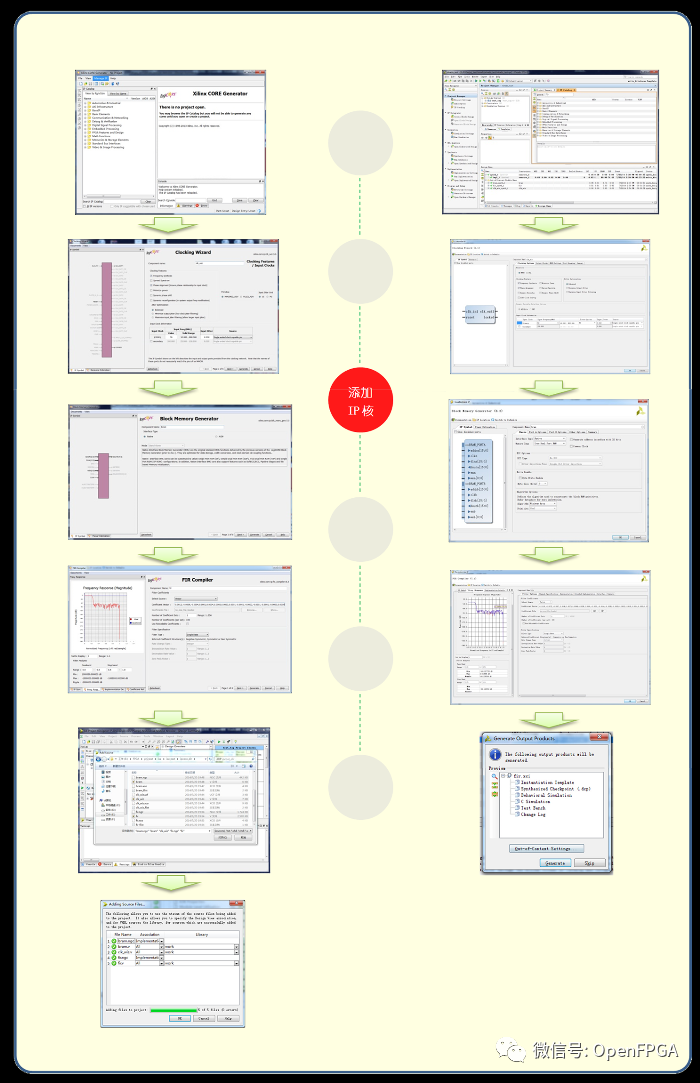

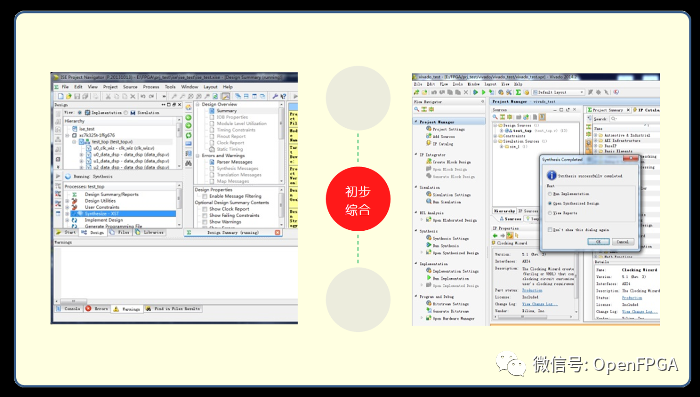

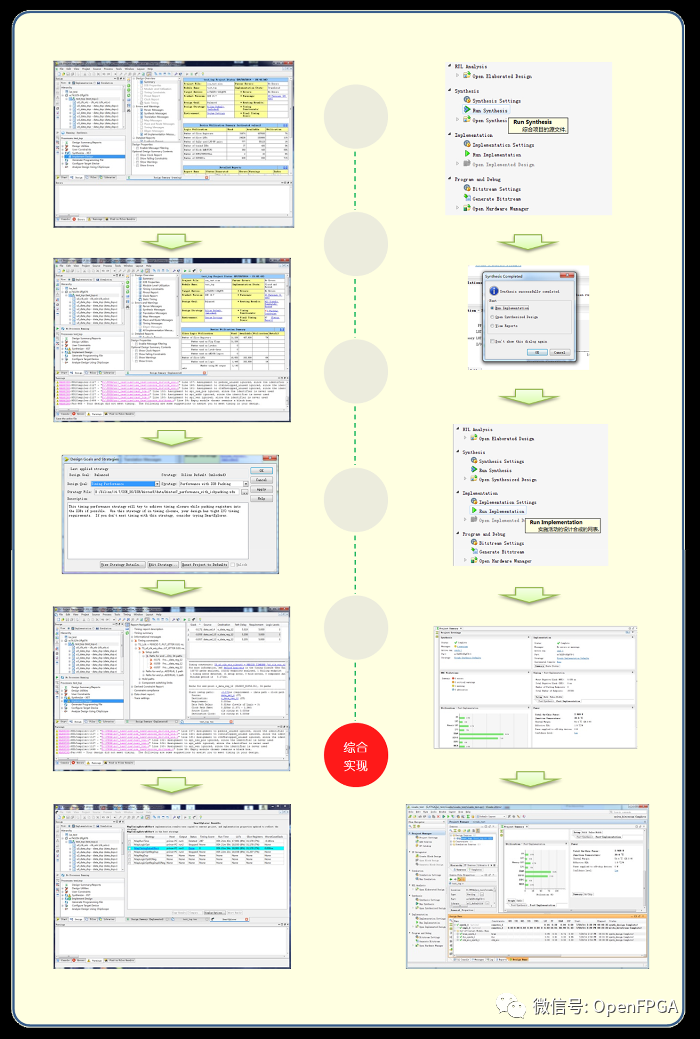

建立工程 -> 加入代码 -> 添加IP核 -> 初步综合 -> 添加约束 -> 综合实现

1、建立工程——点评:

Vivado界面清爽,流程清晰,完败Q2。再也不会因ISE的低集成度,再在各组件中调来调去了。

2、加入代码——点评:

Add Source无明显区别。

3、添加IP核——点评:

由于core gen没有被ISE集成,即便是从ISE中打开core gen,也需要重新建立core gen工程,甚至需要选择与工程一样的元器件,并且生成IP核之后还需要手动添加到ISE工程内。(为了公平测试综合性能,本例在ISE中直接添加IP核网表文件;Vivado的dcp文件中包括综合网表)

4、初步综合——点评:

在添加约束前,最好先综合,以便明确综合后网表中的clk的名字。Vivado实时检查代码是否存在语法错误,而ISE需要综合的时候才能发现。

5、添加约束——点评:

由于ISE添加MMCM时没有加入自动生成的约束,需要重新添加时钟约束。而Vivado自动将IP核添加到工程内,是包含时钟约束的。为了更好的ISE和Vivado的综合性能,管脚位置与电平约束完全一致。

PS:若时钟和管脚约束直接敲命令,两者除了语法,没有明显区别。

6、综合实现——点评:

Vivado默认策略情况下从综合到生成bit共计23分50秒。而ISE第一遍默认策略情况下,25分钟实现结束,时序约束未过。修改实现策略为Timing Performance,又过了二十五分钟,时序还没有过……最后不得已上大招,SmartXplorer同时跑四个!!!!瞬间CPU占用率,内存利用率爆表- -/// 22分钟后,终于有一个时序通过的结果出现。对比效率,Vivado:ISE =3:1。

图片不是特别清晰,这里放一个WORD文档,有需要的可以自行下载:

链接:https://pan.baidu.com/s/1Da1DOwOjIy4PUM7a7LUCTA

提取码:open