背景:zynqNet运用HLS来实现相应的IPcore。相关HLS过程的信息会打印到console之中。

目的:读懂HLS对IPcore代码的HLS过程,具体硬件如何实现。将报告信息存下来用于参考。

IPcore调试成功,HLS打印信息如下,实现了相应的优化指令。

一、 全IPcore的HLS console

Starting C synthesis ...

D:/xilinx/SDx/2016.4/Vivado_HLS/bin/vivado_hls.bat E:/FPGAdocuments/ZynqNetProj/zynqNetHLS/FPGAtop/solution1/csynth.tcl

INFO: [HLS 200-10] Running 'D:/xilinx/SDx/2016.4/Vivado_HLS/bin/unwrapped/win64.o/vivado_hls.exe'

INFO: [HLS 200-10] For user 'Administrator' on host 'cn-20171201uvsa' (Windows NT_amd64 version 6.1) on Wed Dec 12 10:33:39 +0800 2018

INFO: [HLS 200-10] In directory 'E:/FPGAdocuments/ZynqNetProj/zynqNetHLS'

INFO: [HLS 200-10] Opening project 'E:/FPGAdocuments/ZynqNetProj/zynqNetHLS/FPGAtop'.

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/weights_cache.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/weights_cache.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/unittests.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/unittests.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/processing_element.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/processing_element.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/output_cache.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/output_cache.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/network.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/network.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/netconfig.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/netconfig.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/memory_controller.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/memory_controller.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/image_cache.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/image_cache.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/vivado_include/hls_stream.h' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/gpool_cache.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/gpool_cache.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/fpga_top.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/fpga_top.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/cpu_top.hpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/cpu_top.cpp' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/vivado_include/ap_utils.h' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/vivado_include/ap_shift_reg.h' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/vivado_include/etc/ap_private.h' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/vivado_include/etc/ap_int_sim.h' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/vivado_include/ap_int.h' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/vivado_include/etc/ap_fixed_sim.h' to the project

INFO: [HLS 200-10] Adding design file '../_HLS_CODE/vivado_include/ap_fixed.h' to the project

INFO: [HLS 200-10] Adding test bench file '../_HLS_CODE/weights.bin' to the project

INFO: [HLS 200-10] Adding test bench file '../_HLS_CODE/indata.bin' to the project

INFO: [HLS 200-10] Adding test bench file '../_HLS_CODE/cpu_top.hpp' to the project

INFO: [HLS 200-10] Adding test bench file '../_HLS_CODE/cpu_top.cpp' to the project

INFO: [HLS 200-10] Opening solution 'E:/FPGAdocuments/ZynqNetProj/zynqNetHLS/FPGAtop/solution1'.

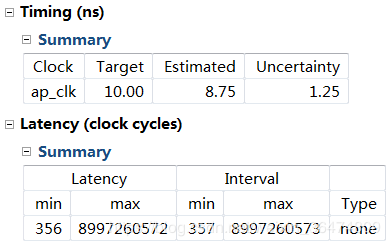

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [HLS 200-10] Setting target device to 'xc7z035ffg676-2'

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/cpu_top.cpp' ...

WARNING: [HLS 200-40] ../_HLS_CODE/cpu_top.cpp:254:46: warning: format specifies type 'unsigned long' but the argument has type 'unsigned int' [-Wformat]

printf("CPU: Loading Input from File %s, %lu kBytes.\n", filename,

~~^

%u

1 warning generated.

WARNING: [HLS 200-40]

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/fpga_top.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/gpool_cache.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/image_cache.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/memory_controller.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/netconfig.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/network.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/output_cache.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/processing_element.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/unittests.cpp' ...

INFO: [HLS 200-10] Analyzing design file '../_HLS_CODE/weights_cache.cpp' ...

INFO: [HLS 200-10] Validating synthesis directives ...

INFO: [HLS 200-111] Finished Checking Pragmas Time (s): cpu = 00:00:32 ; elapsed = 00:06:41 . Memory (MB): peak = 96.879 ; gain = 47.004

INFO: [HLS 200-111] Finished Linking Time (s): cpu = 00:00:32 ; elapsed = 00:08:44 . Memory (MB): peak = 96.879 ; gain = 47.004

INFO: [HLS 200-10] Starting code transformations ...

INFO: [XFORM 203-603] Inlining function 'MemoryController::setup' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:52).

INFO: [XFORM 203-603] Inlining function 'ImageCache::reset' into 'ImageCache::setLayerConfig' (../_HLS_CODE/image_cache.cpp:96).

INFO: [XFORM 203-603] Inlining function 'ImageCache::setLayerConfig' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:62).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::setLayerConfig' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:63).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::precalcInputOffset' into 'WeightsCache::loadFromDRAM' (../_HLS_CODE/weights_cache.cpp:81).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::precalcInputOffset' into 'ProcessingElement::preloadPixelsAndPrecalcCIoffset' (../_HLS_CODE/processing_element.cpp:100).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::precalcInputOffset' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:143).

INFO: [XFORM 203-603] Inlining function 'MemoryController::loadNextWeight' into 'WeightsCache::loadFromDRAM' (../_HLS_CODE/weights_cache.cpp:95).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::getAddrForSingleWeight' into 'WeightsCache::getOneWeight' (../_HLS_CODE/weights_cache.cpp:182).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::getAddrForSingleWeight' into 'WeightsCache::getNineWeights' (../_HLS_CODE/weights_cache.cpp:153).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::getAddrForSingleWeight' into 'WeightsCache::loadFromDRAM' (../_HLS_CODE/weights_cache.cpp:103).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::loadFromDRAM' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:70).

INFO: [XFORM 203-603] Inlining function 'MemoryController::loadNextChannel' into 'ImageCache::preloadPixelFromDRAM' (../_HLS_CODE/image_cache.cpp:69).

INFO: [XFORM 203-603] Inlining function 'ImageCache::preloadPixelFromDRAM' into 'ImageCache::preloadRowFromDRAM' (../_HLS_CODE/image_cache.cpp:80).

INFO: [XFORM 203-603] Inlining function 'ImageCache::preloadPixelFromDRAM' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:102).

INFO: [XFORM 203-603] Inlining function 'ImageCache::preloadPixelFromDRAM' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:76).

INFO: [XFORM 203-603] Inlining function 'ImageCache::preloadRowFromDRAM' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:74).

INFO: [XFORM 203-603] Inlining function 'ImageCache::precalcYOffset' into 'ProcessingElement::preloadPixels' (../_HLS_CODE/processing_element.cpp:81).

INFO: [XFORM 203-603] Inlining function 'ImageCache::getPixel' into 'ProcessingElement::preloadPixels' (../_HLS_CODE/processing_element.cpp:85).

INFO: [XFORM 203-603] Inlining function 'ProcessingElement::preloadPixels' into 'ProcessingElement::preloadPixelsAndPrecalcCIoffset' (../_HLS_CODE/processing_element.cpp:98).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::getNineWeights' into 'ProcessingElement::processAllCHout' (../_HLS_CODE/processing_element.cpp:61).

INFO: [XFORM 203-603] Inlining function 'ProcessingElement::macc2d' into 'ProcessingElement::processAllCHout' (../_HLS_CODE/processing_element.cpp:63).

INFO: [XFORM 203-603] Inlining function 'OutputCache::setChannel' into 'ProcessingElement::processAllCHout' (../_HLS_CODE/processing_element.cpp:66).

INFO: [XFORM 203-603] Inlining function 'OutputCache::setChannel' into 'OutputCache::accumulateChannel' (../_HLS_CODE/output_cache.cpp:37).

INFO: [XFORM 203-603] Inlining function 'OutputCache::getChannel' into 'ProcessingElement::postprocess' (../_HLS_CODE/processing_element.cpp:128).

INFO: [XFORM 203-603] Inlining function 'OutputCache::getChannel' into 'OutputCache::accumulateChannel' (../_HLS_CODE/output_cache.cpp:35).

INFO: [XFORM 203-603] Inlining function 'OutputCache::accumulateChannel' into 'ProcessingElement::processAllCHout' (../_HLS_CODE/processing_element.cpp:68).

INFO: [XFORM 203-603] Inlining function 'MemoryController::setupPixelWriteback' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:137).

INFO: [XFORM 203-603] Inlining function 'WeightsCache::getOneWeight' into 'ProcessingElement::postprocess' (../_HLS_CODE/processing_element.cpp:130).

INFO: [XFORM 203-603] Inlining function 'ProcessingElement::postprocess' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:152).

INFO: [XFORM 203-603] Inlining function 'MemoryController::writeBackOutputChannel' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:155).

INFO: [XFORM 203-603] Inlining function 'GPoolCache::setChannel' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:161).

INFO: [XFORM 203-603] Inlining function 'GPoolCache::accumulateChannel' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:163).

INFO: [XFORM 203-603] Inlining function 'GPoolCache::getChannel' into 'MemoryController::writeBackResult' (../_HLS_CODE/memory_controller.cpp:111).

INFO: [XFORM 203-603] Inlining function 'MemoryController::writeBackResult' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:178).

INFO: [HLS 200-111] Finished Standard Transforms Time (s): cpu = 00:01:53 ; elapsed = 00:11:07 . Memory (MB): peak = 2966.441 ; gain = 2916.566

INFO: [HLS 200-10] Checking synthesizability ...

INFO: [XFORM 203-602] Inlining function 'MemoryController::setLayerConfig' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:64) automatically.

INFO: [XFORM 203-602] Inlining function 'ProcessingElement::setLayerConfig' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:65) automatically.

INFO: [XFORM 203-602] Inlining function 'MemoryController::setPixelLoadRow' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:73) automatically.

INFO: [XFORM 203-602] Inlining function 'ImageCache::setNextChannel' into 'fpga_top' (../_HLS_CODE/image_cache.cpp:70->../_HLS_CODE/image_cache.cpp:80->../_HLS_CODE/fpga_top.cpp:74) automatically.

INFO: [HLS 200-111] Finished Checking Synthesizability Time (s): cpu = 00:02:09 ; elapsed = 00:11:25 . Memory (MB): peak = 3025.816 ; gain = 2975.941

INFO: [XFORM 203-502] Unrolling all sub-loops inside loop 'L_CH_OUT' (../_HLS_CODE/processing_element.cpp:54) in function 'ProcessingElement::processAllCHout' for pipelining.

INFO: [XFORM 203-502] Unrolling all loops for pipelining in function 'ProcessingElement::preloadPixelsAndPrecalcCIoffset' (../_HLS_CODE/processing_element.cpp:38:28).

INFO: [XFORM 203-501] Unrolling loop 'L_CH_OUT' (../_HLS_CODE/processing_element.cpp:54) in function 'ProcessingElement::processAllCHout' partially with a factor of 16.

INFO: [XFORM 203-501] Unrolling loop 'L_getNineWeights' (../_HLS_CODE/weights_cache.cpp:160) in function 'ProcessingElement::processAllCHout' completely.

INFO: [XFORM 203-501] Unrolling loop 'L_MACC_multiply' (../_HLS_CODE/processing_element.cpp:110) in function 'ProcessingElement::processAllCHout' completely.

INFO: [XFORM 203-501] Unrolling loop 'L_MACC_accumulate' (../_HLS_CODE/processing_element.cpp:115) in function 'ProcessingElement::processAllCHout' completely.

INFO: [XFORM 203-501] Unrolling loop 'L_PE_loadPixel_Y' (../_HLS_CODE/processing_element.cpp:79) in function 'ProcessingElement::preloadPixelsAndPrecalcCIoffset' completely.

INFO: [XFORM 203-501] Unrolling loop 'L_PE_loadPixel_X' (../_HLS_CODE/processing_element.cpp:83) in function 'ProcessingElement::preloadPixelsAndPrecalcCIoffset' completely.

INFO: [XFORM 203-101] Partitioning array 'GPoolCache::GBRAM' in dimension 1 with a cyclic factor 16.

INFO: [XFORM 203-101] Partitioning array 'pixel_buffer' (../_HLS_CODE/processing_element.cpp:40) in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'multresult' (../_HLS_CODE/processing_element.cpp:107) in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'weights_temp' (../_HLS_CODE/weights_cache.cpp:157) in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'weights_local' (../_HLS_CODE/processing_element.cpp:58) in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'OutputCache::OBRAM' in dimension 1 with a cyclic factor 16.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.0' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.1' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.2' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.3' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.4' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.5' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.6' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.7' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.8' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.9' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.10' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.11' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.12' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.13' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.14' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.15' in dimension 1 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.0.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.0.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.0.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.1.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.1.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.1.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.2.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.2.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.2.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.3.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.3.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.3.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.4.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.4.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.4.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.5.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.5.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.5.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.6.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.6.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.6.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.7.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.7.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.7.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.8.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.8.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.8.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.9.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.9.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.9.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.10.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.10.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.10.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.11.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.11.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.11.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.12.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.12.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.12.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.13.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.13.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.13.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.14.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.14.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.14.2' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.15.0' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.15.1' in dimension 2 completely.

INFO: [XFORM 203-101] Partitioning array 'WeightsCache::WBRAM.15.2' in dimension 2 completely.

INFO: [XFORM 203-602] Inlining function 'MemoryController::setLayerConfig' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:64) automatically.

INFO: [XFORM 203-602] Inlining function 'ProcessingElement::setLayerConfig' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:65) automatically.

INFO: [XFORM 203-602] Inlining function 'MemoryController::setPixelLoadRow' into 'fpga_top' (../_HLS_CODE/fpga_top.cpp:73) automatically.

INFO: [XFORM 203-602] Inlining function 'ImageCache::setNextChannel' into 'fpga_top' (../_HLS_CODE/image_cache.cpp:70->../_HLS_CODE/image_cache.cpp:80->../_HLS_CODE/fpga_top.cpp:74) automatically.

INFO: [XFORM 203-622] Instantiating function 'ProcessingElement::processInputChannel'(../_HLS_CODE/processing_element.cpp:35:1) to 'ProcessingElement::processInputChannel.0' at call site (../_HLS_CODE/fpga_top.cpp:122) by setting 'ci_in.V' to '.0'.

INFO: [XFORM 203-712] Applying dataflow to function 'ProcessingElement::processInputChannel.0' (../_HLS_CODE/processing_element.cpp:35:1), detected/extracted 2 process function(s):

'ProcessingElement::preloadPixelsAndPrecalcCIoffset108'

'ProcessingElement::processAllCHout'.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/weights_cache.cpp:91:56) to (../_HLS_CODE/weights_cache.cpp:105:7) in function 'fpga_top'... converting 4 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/fpga_top.cpp:147:52) to (../_HLS_CODE/fpga_top.cpp:159:9) in function 'fpga_top'... converting 4 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/fpga_top.cpp:135:67) to (../_HLS_CODE/fpga_top.cpp:147:12) in function 'fpga_top'... converting 3 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock from (../_HLS_CODE/processing_element.cpp:54:46) to (../_HLS_CODE/processing_element.cpp:65:9) in function 'ProcessingElement::processAllCHout'... converting 13 basic blocks.

INFO: [XFORM 203-401] Performing if-conversion on hyperblock in function 'ProcessingElement::preloadPixelsAndPrecalcCIoffset108'... converting 19 basic blocks.

INFO: [HLS 200-111] Finished Pre-synthesis Time (s): cpu = 00:03:19 ; elapsed = 00:14:15 . Memory (MB): peak = 4396.457 ; gain = 4346.582

WARNING: [XFORM 203-542] Cannot flatten a loop nest 'L_LOADWEIGHTS_CI' (../_HLS_CODE/weights_cache.cpp:78:49) in function 'fpga_top' :

WARNING: [XFORM 203-542] the outer loop is not a perfect loop.

WARNING: [XFORM 203-542] Cannot flatten a loop nest 'L_DRAM_PRELOADROW_X' (../_HLS_CODE/image_cache.cpp:78:68) in function 'fpga_top' :

WARNING: [XFORM 203-542] the outer loop is not a perfect loop because there is nontrivial logic before entering the inner loop.

WARNING: [XFORM 203-542] Cannot flatten a loop nest 'L_X' (../_HLS_CODE/fpga_top.cpp:92:40) in function 'fpga_top' :

WARNING: [XFORM 203-542] more than one sub loop.

INFO: [XFORM 203-541] Flattening a loop nest 'L_Y' (../_HLS_CODE/fpga_top.cpp:81:39) in function 'fpga_top'.

WARNING: [XFORM 203-631] Renaming function 'ProcessingElement::processInputChannel.0' (../_HLS_CODE/processing_element.cpp:37:1) into processInputChannel..

WARNING: [XFORM 203-631] Renaming function 'ProcessingElement::processAllCHout' (../_HLS_CODE/processing_element.cpp:51) into processAllCHout.

WARNING: [XFORM 203-631] Renaming function 'ProcessingElement::preloadPixelsAndPrecalcCIoffset108' (../_HLS_CODE/weights_cache.cpp:38:1) into preloadPixelsAndPrec.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.10'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.11'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.12'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.5'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.6'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.7'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.14'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.13'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.15'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.3'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.2'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.4'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.1'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.0'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.9'.

WARNING: [ANALYSIS 214-52] Found false inter dependency for variable 'GBRAM.8'.

INFO: [HLS 200-111] Finished Architecture Synthesis Time (s): cpu = 00:04:07 ; elapsed = 00:16:17 . Memory (MB): peak = 4958.328 ; gain = 4908.453

INFO: [HLS 200-10] Starting hardware synthesis ...

INFO: [HLS 200-10] Synthesizing 'fpga_top' ...

WARNING: [SYN 201-103] Legalizing function name 'reg

WARNING: [SYN 201-103] Legalizing function name 'processInputChannel.' to 'processInputChannel_s'.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Implementing module 'reg_float_s'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SCHED 204-11] Starting scheduling ...

INFO: [SCHED 204-61] Pipelining function 'reg

INFO: [SCHED 204-61] Pipelining result: Target II: 1, Final II: 1, Depth: 2.

INFO: [SCHED 204-11] Finished scheduling.

INFO: [HLS 200-111] Elapsed time: 1280.23 seconds; current allocated memory: 528.616 MB.

INFO: [BIND 205-100] Starting micro-architecture generation ...

INFO: [BIND 205-101] Performing variable lifetime analysis.

INFO: [BIND 205-101] Exploring resource sharing.

INFO: [BIND 205-101] Binding ...

INFO: [BIND 205-100] Finished micro-architecture generation.

INFO: [HLS 200-111] Elapsed time: 3.39 seconds; current allocated memory: 528.618 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Implementing module 'preloadPixelsAndPrec'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SCHED 204-11] Starting scheduling ...

INFO: [SCHED 204-61] Pipelining function 'preloadPixelsAndPrec'.

WARNING: [SCHED 204-69] Unable to schedule 'load' operation ('ImageCache_IBRAM_lo_7', ../_HLS_CODE/image_cache.cpp:117->../_HLS_CODE/processing_element.cpp:85->../_HLS_CODE/processing_element.cpp:98) on array 'ImageCache_IBRAM' due to limited memory ports.

INFO: [SCHED 204-61] Pipelining result: Target II: 7, Final II: 9, Depth: 14.

INFO: [SCHED 204-11] Finished scheduling.

INFO: [HLS 200-111] Elapsed time: 4.17 seconds; current allocated memory: 528.573 MB.

INFO: [BIND 205-100] Starting micro-architecture generation ...

INFO: [BIND 205-101] Performing variable lifetime analysis.

INFO: [BIND 205-101] Exploring resource sharing.

INFO: [BIND 205-101] Binding ...

INFO: [BIND 205-100] Finished micro-architecture generation.

INFO: [HLS 200-111] Elapsed time: 3.54 seconds; current allocated memory: 528.703 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Implementing module 'processAllCHout'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SCHED 204-11] Starting scheduling ...

INFO: [SCHED 204-61] Pipelining loop 'L_CH_OUT'.

INFO: [SCHED 204-61] Pipelining result: Target II: 1, Final II: 1, Depth: 51.

INFO: [SCHED 204-11] Finished scheduling.

INFO: [HLS 200-111] Elapsed time: 16.351 seconds; current allocated memory: 545.185 MB.

INFO: [BIND 205-100] Starting micro-architecture generation ...

INFO: [BIND 205-101] Performing variable lifetime analysis.

INFO: [BIND 205-101] Exploring resource sharing.

INFO: [BIND 205-101] Binding ...

INFO: [BIND 205-100] Finished micro-architecture generation.

INFO: [HLS 200-111] Elapsed time: 23.25 seconds; current allocated memory: 551.798 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Implementing module 'processInputChannel_s'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SCHED 204-11] Starting scheduling ...

INFO: [SCHED 204-11] Finished scheduling.

INFO: [HLS 200-111] Elapsed time: 24.21 seconds; current allocated memory: 551.389 MB.

INFO: [BIND 205-100] Starting micro-architecture generation ...

INFO: [BIND 205-101] Performing variable lifetime analysis.

INFO: [BIND 205-101] Exploring resource sharing.

INFO: [BIND 205-101] Binding ...

INFO: [BIND 205-100] Finished micro-architecture generation.

INFO: [HLS 200-111] Elapsed time: 6.13 seconds; current allocated memory: 551.382 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Implementing module 'fpga_top'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SCHED 204-11] Starting scheduling ...

INFO: [SCHED 204-61] Pipelining loop 'L_LOADWEIGHTS_CO'.

INFO: [SCHED 204-61] Pipelining result: Target II: 2, Final II: 2, Depth: 12.

INFO: [SCHED 204-61] Pipelining loop 'L_PRELOAD_PIXEL_FROM_DRAM'.

INFO: [SCHED 204-61] Pipelining result: Target II: 1, Final II: 1, Depth: 11.

INFO: [SCHED 204-61] Pipelining loop 'L_PRELOAD_PIXEL_FROM_DRAM'.

INFO: [SCHED 204-61] Pipelining result: Target II: 1, Final II: 1, Depth: 11.

INFO: [SCHED 204-61] Pipelining loop 'L_PRELOAD_PIXEL_FROM_DRAM'.

INFO: [SCHED 204-61] Pipelining result: Target II: 1, Final II: 1, Depth: 11.

INFO: [SCHED 204-61] Pipelining loop 'L_POSTPROCESS'.

INFO: [SCHED 204-61] Pipelining result: Target II: 1, Final II: 1, Depth: 17.

INFO: [SCHED 204-61] Pipelining loop 'L_writeBackResult'.

INFO: [SCHED 204-61] Pipelining result: Target II: 1, Final II: 1, Depth: 9.

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6660) 'load' (29) to operation (ID:6637) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6661) 'load' (29) to operation (ID:6635) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6662) 'load' (29) to operation (ID:6633) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6663) 'load' (29) to operation (ID:6631) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6664) 'load' (29) to operation (ID:6629) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6665) 'load' (29) to operation (ID:6627) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6666) 'load' (29) to operation (ID:6625) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6667) 'load' (29) to operation (ID:6623) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6668) 'load' (29) to operation (ID:6621) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6669) 'load' (29) to operation (ID:6619) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6670) 'load' (29) to operation (ID:6617) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6671) 'load' (29) to operation (ID:6615) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6672) 'load' (29) to operation (ID:6613) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6673) 'load' (29) to operation (ID:6611) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6674) 'load' (29) to operation (ID:6609) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6675) 'load' (29) to operation (ID:6639) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6704) 'store' (34) to operation (ID:6609) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6705) 'store' (34) to operation (ID:6611) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6706) 'store' (34) to operation (ID:6613) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6707) 'store' (34) to operation (ID:6615) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6708) 'store' (34) to operation (ID:6617) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6709) 'store' (34) to operation (ID:6619) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6710) 'store' (34) to operation (ID:6621) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6711) 'store' (34) to operation (ID:6623) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6712) 'store' (34) to operation (ID:6625) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6713) 'store' (34) to operation (ID:6627) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6714) 'store' (34) to operation (ID:6629) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6715) 'store' (34) to operation (ID:6631) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6716) 'store' (34) to operation (ID:6633) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6717) 'store' (34) to operation (ID:6635) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6718) 'store' (34) to operation (ID:6637) 'store' (27).

WARNING: [SCHED 204-81] Due to pragma (../_HLS_CODE/gpool_cache.cpp:33:1), dependence in pipeline region 'L_POSTPROCESS' need to be checked during RTL simulation, which is from operation (ID:6719) 'store' (34) to operation (ID:6639) 'store' (27).

INFO: [SCHED 204-11] Finished scheduling.

INFO: [HLS 200-111] Elapsed time: 41.92 seconds; current allocated memory: 582.749 MB.

INFO: [BIND 205-100] Starting micro-architecture generation ...

INFO: [BIND 205-101] Performing variable lifetime analysis.

INFO: [BIND 205-101] Exploring resource sharing.

INFO: [BIND 205-101] Binding ...

INFO: [BIND 205-100] Finished micro-architecture generation.

INFO: [HLS 200-111] Elapsed time: 37.121 seconds; current allocated memory: 594.992 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Generating RTL for module 'reg_float_s'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [RTGEN 206-100] Finished creating RTL model for 'reg_float_s'.

INFO: [HLS 200-111] Elapsed time: 36.68 seconds; current allocated memory: 595.097 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Generating RTL for module 'preloadPixelsAndPrec'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SYN 201-210] Renamed object name 'fpga_top_mul_16s_2ns_16_3' to 'fpga_top_mul_16s_bkb' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'fpga_top_mul_10ns_10ns_19_3' to 'fpga_top_mul_10nscud' due to the length limit 20

INFO: [RTGEN 206-100] Generating core module 'fpga_top_mul_10nscud': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'fpga_top_mul_16s_bkb': 3 instance(s).

INFO: [RTGEN 206-100] Finished creating RTL model for 'preloadPixelsAndPrec'.

INFO: [HLS 200-111] Elapsed time: 2.75 seconds; current allocated memory: 596.029 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Generating RTL for module 'processAllCHout'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SYN 201-210] Renamed object name 'fpga_top_fadd_32ns_32ns_32_4_full_dsp' to 'fpga_top_fadd_32ndEe' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'fpga_top_fmul_32ns_32ns_32_3_max_dsp' to 'fpga_top_fmul_32neOg' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'fpga_top_mux_32_32_1' to 'fpga_top_mux_32_3fYi' due to the length limit 20

INFO: [RTGEN 206-100] Generating core module 'fpga_top_fadd_32ndEe': 160 instance(s).

INFO: [RTGEN 206-100] Generating core module 'fpga_top_fmul_32neOg': 144 instance(s).

INFO: [RTGEN 206-100] Generating core module 'fpga_top_mux_32_3fYi': 144 instance(s).

INFO: [RTGEN 206-100] Finished creating RTL model for 'processAllCHout'.

INFO: [HLS 200-111] Elapsed time: 11.68 seconds; current allocated memory: 620.074 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Generating RTL for module 'processInputChannel_s'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [RTGEN 206-100] Finished creating RTL model for 'processInputChannel_s'.

INFO: [HLS 200-111] Elapsed time: 39.53 seconds; current allocated memory: 631.107 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Generating RTL for module 'fpga_top'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/memorybus' to 'm_axi'.

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_name' to 's_axilite & ap_memory'.

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_width_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_height_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_channels_in_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_channels_out_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_kernel_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_stride_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_pad' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_relu' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_is_first_split_layer' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_is_second_split_layer' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_global_pool' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_mem_addr_input_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_mem_addr_output_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/layer_mem_addr_weights_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/SHARED_DRAM' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/weights_offset' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/num_weights_V' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on port 'fpga_top/input_offset' to 's_axilite & ap_none' (register).

INFO: [RTGEN 206-500] Setting interface mode on function 'fpga_top' to 's_axilite & ap_ctrl_hs' (register).

WARNING: [RTGEN 206-101] Register 'MemoryController_dr' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_dr' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'MemoryController_dr_1' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_dr_1' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'ImageCache_width_in' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'ImageCache_width_in' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'ImageCache_height_i' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'ImageCache_height_i' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'ImageCache_ch_in_V' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'ImageCache_ch_in_V' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'ImageCache_line_wid' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'ImageCache_line_wid' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'ImageCache_loads_le' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'ImageCache_loads_le' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global scalar 'ImageCache_curr_img' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'ImageCache_curr_img_1' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'ImageCache_curr_img_1' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'WeightsCache_kernel' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'WeightsCache_kernel' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global scalar 'WeightsCache_ch_in_s' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'WeightsCache_ch_out' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'WeightsCache_ch_out' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global scalar 'WeightsCache_num_we' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global scalar 'WeightsCache_write_s' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'MemoryController_la' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_la' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_la_3' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'MemoryController_la_4' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_la_4' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global scalar 'pixels_per_row' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'MemoryController_ch' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_ch' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'MemoryController_wi' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_wi' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'MemoryController_is_1' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_is_1' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'MemoryController_is' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_is' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global scalar 'ProcessingElement_k' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'ProcessingElement_r' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'ProcessingElement_r' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Register 'MemoryController_la_5' is power-on initialization.

WARNING: [RTGEN 206-101] Global scalar 'MemoryController_la_5' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global array 'ImageCache_IBRAM' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_ImageCache_IBRAM' to 'fpga_top_ImageCacg8j' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'OBRAM_0' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_0' to 'fpga_top_WBRAM_0_hbi' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_0' to 'fpga_top_WBRAM_0_ibs' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_0' to 'fpga_top_WBRAM_0_jbC' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_1' to 'fpga_top_WBRAM_0_kbM' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_1' to 'fpga_top_WBRAM_0_lbW' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_1' to 'fpga_top_WBRAM_0_mb6' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_2' to 'fpga_top_WBRAM_0_ncg' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_2' to 'fpga_top_WBRAM_0_ocq' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_2' to 'fpga_top_WBRAM_0_pcA' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_3' to 'fpga_top_WBRAM_0_qcK' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_3' to 'fpga_top_WBRAM_0_rcU' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_3' to 'fpga_top_WBRAM_0_sc4' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_4' to 'fpga_top_WBRAM_0_tde' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_4' to 'fpga_top_WBRAM_0_udo' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_4' to 'fpga_top_WBRAM_0_vdy' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_5' to 'fpga_top_WBRAM_0_wdI' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_5' to 'fpga_top_WBRAM_0_xdS' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_5' to 'fpga_top_WBRAM_0_yd2' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_6' to 'fpga_top_WBRAM_0_zec' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_6' to 'fpga_top_WBRAM_0_Aem' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_6' to 'fpga_top_WBRAM_0_Bew' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_7' to 'fpga_top_WBRAM_0_CeG' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_7' to 'fpga_top_WBRAM_0_DeQ' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_7' to 'fpga_top_WBRAM_0_Ee0' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_0_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_0_8' to 'fpga_top_WBRAM_0_Ffa' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_1_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_1_8' to 'fpga_top_WBRAM_0_Gfk' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_0_2_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_0_2_8' to 'fpga_top_WBRAM_0_Hfu' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'OBRAM_1' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_0' to 'fpga_top_WBRAM_1_IfE' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_0' to 'fpga_top_WBRAM_1_JfO' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_0' to 'fpga_top_WBRAM_1_KfY' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_1' to 'fpga_top_WBRAM_1_Lf8' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_1' to 'fpga_top_WBRAM_1_Mgi' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_1' to 'fpga_top_WBRAM_1_Ngs' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_2' to 'fpga_top_WBRAM_1_OgC' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_2' to 'fpga_top_WBRAM_1_PgM' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_2' to 'fpga_top_WBRAM_1_QgW' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_3' to 'fpga_top_WBRAM_1_Rg6' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_3' to 'fpga_top_WBRAM_1_Shg' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_3' to 'fpga_top_WBRAM_1_Thq' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_4' to 'fpga_top_WBRAM_1_UhA' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_4' to 'fpga_top_WBRAM_1_VhK' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_4' to 'fpga_top_WBRAM_1_WhU' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_5' to 'fpga_top_WBRAM_1_Xh4' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_5' to 'fpga_top_WBRAM_1_Yie' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_5' to 'fpga_top_WBRAM_1_Zio' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_6' to 'fpga_top_WBRAM_1_0iy' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_6' to 'fpga_top_WBRAM_1_1iI' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_6' to 'fpga_top_WBRAM_1_2iS' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_7' to 'fpga_top_WBRAM_1_3i2' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_7' to 'fpga_top_WBRAM_1_4jc' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_7' to 'fpga_top_WBRAM_1_5jm' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_0_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_0_8' to 'fpga_top_WBRAM_1_6jw' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_1_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_1_8' to 'fpga_top_WBRAM_1_7jG' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_1_2_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_1_2_8' to 'fpga_top_WBRAM_1_8jQ' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'OBRAM_2' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_0' to 'fpga_top_WBRAM_2_9j0' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_0' to 'fpga_top_WBRAM_2_bak' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_0' to 'fpga_top_WBRAM_2_bbk' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_1' to 'fpga_top_WBRAM_2_bck' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_1' to 'fpga_top_WBRAM_2_bdk' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_1' to 'fpga_top_WBRAM_2_bek' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_2' to 'fpga_top_WBRAM_2_bfk' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_2' to 'fpga_top_WBRAM_2_bgk' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_2' to 'fpga_top_WBRAM_2_bhl' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_3' to 'fpga_top_WBRAM_2_bil' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_3' to 'fpga_top_WBRAM_2_bjl' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_3' to 'fpga_top_WBRAM_2_bkl' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_4' to 'fpga_top_WBRAM_2_bll' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_4' to 'fpga_top_WBRAM_2_bml' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_4' to 'fpga_top_WBRAM_2_bnm' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_5' to 'fpga_top_WBRAM_2_bom' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_5' to 'fpga_top_WBRAM_2_bpm' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_5' to 'fpga_top_WBRAM_2_bqm' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_6' to 'fpga_top_WBRAM_2_brm' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_6' to 'fpga_top_WBRAM_2_bsm' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_6' to 'fpga_top_WBRAM_2_btn' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_7' to 'fpga_top_WBRAM_2_bun' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_7' to 'fpga_top_WBRAM_2_bvn' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_7' to 'fpga_top_WBRAM_2_bwn' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_0_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_0_8' to 'fpga_top_WBRAM_2_bxn' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_1_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_1_8' to 'fpga_top_WBRAM_2_byn' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_2_2_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_2_2_8' to 'fpga_top_WBRAM_2_bzo' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'OBRAM_3' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_0' to 'fpga_top_WBRAM_3_bAo' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_0' to 'fpga_top_WBRAM_3_bBo' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_0' to 'fpga_top_WBRAM_3_bCo' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_1' to 'fpga_top_WBRAM_3_bDo' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_1' to 'fpga_top_WBRAM_3_bEo' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_1' to 'fpga_top_WBRAM_3_bFp' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_2' to 'fpga_top_WBRAM_3_bGp' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_2' to 'fpga_top_WBRAM_3_bHp' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_2' to 'fpga_top_WBRAM_3_bIp' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_3' to 'fpga_top_WBRAM_3_bJp' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_3' to 'fpga_top_WBRAM_3_bKp' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_3' to 'fpga_top_WBRAM_3_bLp' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_4' to 'fpga_top_WBRAM_3_bMq' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_4' to 'fpga_top_WBRAM_3_bNq' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_4' to 'fpga_top_WBRAM_3_bOq' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_5' to 'fpga_top_WBRAM_3_bPq' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_5' to 'fpga_top_WBRAM_3_bQq' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_5' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_5' to 'fpga_top_WBRAM_3_bRq' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_6' to 'fpga_top_WBRAM_3_bSr' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_6' to 'fpga_top_WBRAM_3_bTr' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_6' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_6' to 'fpga_top_WBRAM_3_bUr' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_7' to 'fpga_top_WBRAM_3_bVr' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_7' to 'fpga_top_WBRAM_3_bWr' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_7' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_7' to 'fpga_top_WBRAM_3_bXr' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_0_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_0_8' to 'fpga_top_WBRAM_3_bYs' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_1_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_1_8' to 'fpga_top_WBRAM_3_bZs' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_3_2_8' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_3_2_8' to 'fpga_top_WBRAM_3_b0s' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'OBRAM_4' will not be exposed as RTL port.

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_0_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_0_0' to 'fpga_top_WBRAM_4_b1s' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_1_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_1_0' to 'fpga_top_WBRAM_4_b2s' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_2_0' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_2_0' to 'fpga_top_WBRAM_4_b3s' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_0_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_0_1' to 'fpga_top_WBRAM_4_b4t' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_1_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_1_1' to 'fpga_top_WBRAM_4_b5t' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_2_1' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_2_1' to 'fpga_top_WBRAM_4_b6t' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_0_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_0_2' to 'fpga_top_WBRAM_4_b7t' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_1_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_1_2' to 'fpga_top_WBRAM_4_b8t' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_2_2' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_2_2' to 'fpga_top_WBRAM_4_b9t' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_0_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_0_3' to 'fpga_top_WBRAM_4_cau' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_1_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_1_3' to 'fpga_top_WBRAM_4_cbu' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_2_3' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_2_3' to 'fpga_top_WBRAM_4_ccu' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_0_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_0_4' to 'fpga_top_WBRAM_4_cdu' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_1_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_1_4' to 'fpga_top_WBRAM_4_ceu' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_2_4' will not be exposed as RTL port.

INFO: [SYN 201-210] Renamed object name 'fpga_top_WBRAM_4_2_4' to 'fpga_top_WBRAM_4_cfu' due to the length limit 20

WARNING: [RTGEN 206-101] Global array 'WBRAM_4_0_5' will not be exposed as RTL port.