作者: ShownSun,文章来源: 时沿科技微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

引言

雷达信号处理离不开高速ADC/DAC的使用,而高速ADC/DAC的信号处理对时序的要求非常苛刻。Xilinx SelectIO IP的出现满足了大多数芯片对于时序的处理需求,开发者可以高效的完成ADC/DAC驱动设计。

本文主要针对Xilinx SelectIO IP的GUI(图形用户界面),对每个参数进行详细解释,理解其中的内涵,快速完成驱动设计。下文详细讲述各个参数含义,内容上有些枯燥,后续进行FPGA设计实战,理论与实际相结合。

介绍

Xilinx SelectI IP是一个VHDL/Veilog封装文件,根据用户配置生成实例化的I/O逻辑,满足了输入SERDES、输出SERDES和延迟模块的应用要求。另外,它也可以例化生成所需的I/O时钟原语,将它连接到I/O引脚。

特色

产品说明书

SelectIO接口提供了源代码HDL,包括输入、输出或双向总线I/O电路,缓冲区,任何所需的延迟元件,ISERDES和OSERDES、寄存器和I/O时钟驱动的实现。电路设计包含两个主要组件:时钟缓冲和处理,以及数据路径。

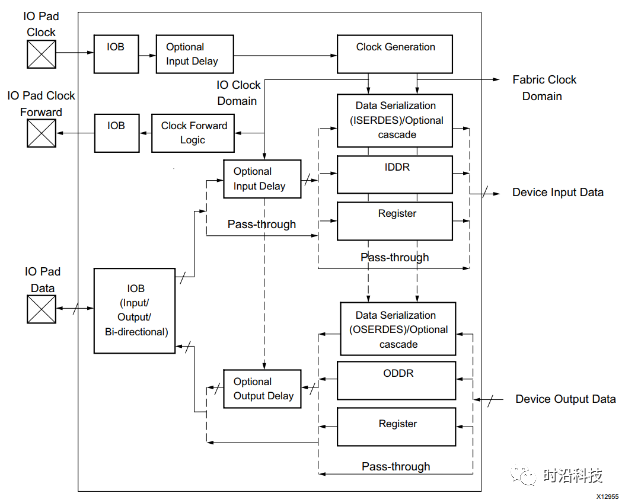

SelectIO内部框图

时钟缓冲和处理

SelectIO向导支持对时钟I/O逻辑使用BUFG或BUFIO2。一个带有BUFIO2原语的输入数据如下图所示。可以为输入时钟添加插入延迟。

I/O网络时钟连接

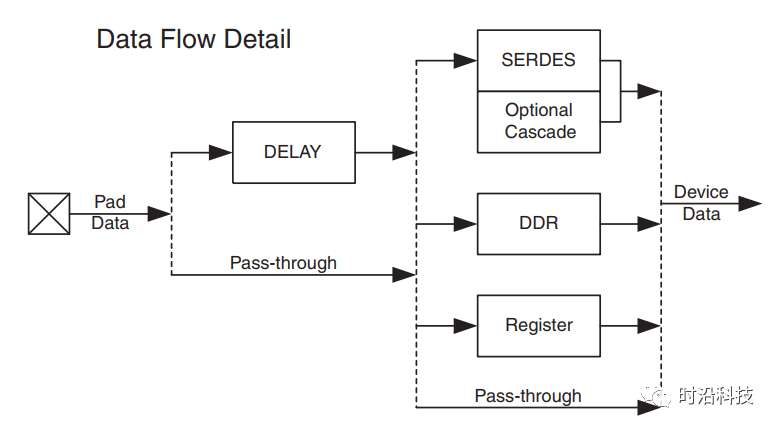

数据路径

SelectIO向导帮助在I/O中实例化和配置组件互连。你可以选择:

数据流细节

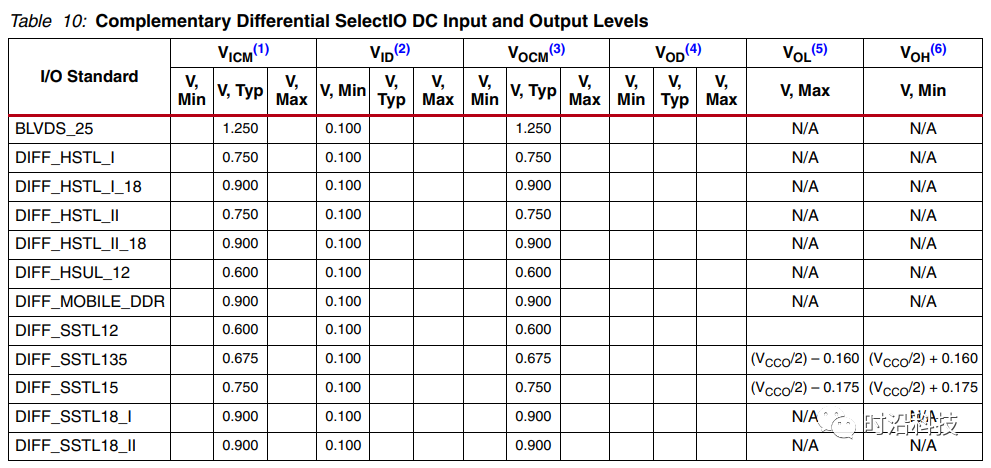

标准

该接口支持下列I/O标准。

单端信号: HSTL_I, HSTL_II, HSTL_III, HSTL_I_18, HSTL_II_18, HSTL_III_18, HSTL_I_12, LVCMOS33, LVCMOS25, LVCMOS18, LVCMOS15, LVCMOS12, SSTL15 SSTL18_I, SSTL18_II

差分信号: DIFF HSTL I, DIFF HSTL I 18, DIFF HSTL II, DIFF HSTL II 18, DIFF SSTL15, DIFF SSTL18 I, DIFF SSTL18 II, LVDS25, TMDS_33, MINI_LVDS_25, PPDS_25, BLVDS_25、LVDS RSDS_25

SelectIO单端输入输出电平

SelectIO差分输入输出电平

更多关于Select IO逻辑资源的详细介绍(比如LOGIC、DELAY、DELAYCTRL、SERDES等),请阅读ug471_7Series_SelectIO.pdf

设计流程

本章描述了定制和生成核、约束核和的仿真、合成和实现步骤。

Data Bus Setup界面

Interface Template

选择向导支持SGMII, DVI接收器,DVI发射器,Camera link接收器数据总线格式,摄像头连接发射器和芯片对芯片接口。SelectIO接口向导仅为上面提到的所有接口配置数据引脚。一般选择Custom或者Chip to Chip来完成高速ADC、DAC芯片或者AD/DA芯片的时序设计。

Data Bus Direction

总线的方向可以选择。选择向导支持输入,输出,双向和单独的I/O总线。单独的输入和输出选项创建独立的输入和输出引脚。开发者根据所用芯片的引脚实际方向进行选择。

Data Rate

如果数据在上升沿触发时,请选择SDR。如果上升沿与下降沿都触发,选择DDR。数据速率的选择影响序列化因子限制。

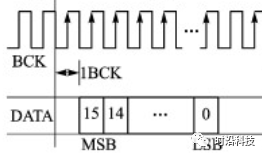

Serialization Factor

如果选择了序列化因子,将实例化ISERDESE2(串并转换器)和/或OSERDESE2(并串转换器)。所有数据由时间片,然后从右到左连接。例如,假设输出数据总线是8位宽的,序列化因子为4。如果数据在引脚上显示为:00,01、02、03时,呈现给设备的数据将为03020100。如果选择了10或14的序列化因子,那么每个I/O将实例化两个SERDES块因为每个SERDES的最大序列化能力是8:1。当数据速率为SDR时,序列化因子的可能值为2-8。当数据速率为DDR时,序列化因子可设置为4、6、8、10或14。Bitslip对于网络模式总是启用功能。如果不是,则将此引脚绑定到逻辑0。

如果所用ADC/DAC芯片为串行数据输入输出,选择序列化因子,可以方便的实现串并、并串数据之间的转换。

串行数据时序

如果选择了序列化因子,IP自动生成ISERDESE2或者OSERDESE2,IP引脚会多出Bitslip,其用来实现并行数据的边界对齐。比如串行输入的8bit的数据,经过ISERDESE2后,得到8bit的并行数据,但这并行数据可能存在前后8bit数据之间的错位,也即无法正确判断最高位、最低位, Bitslip就是用来找到并行数据的边界。

下图展示了Bitslip是如何确定并行数据的边界:对于SDR模式,Bitslip使能1次,则数据会左移1次,对于8bit并行数据,移动8次完成一个循环,可以这样无止境的循环。对于DDR模式,Bitslip工作方式不同,Bitslip使能1次,数据会右移1次或者左移3次,两者交替进行,同样移动8次完成一个循环。

不同模式Bitslip操作

External Data Width

芯片的并行输入、输出引脚的数目,比如:并行16位ADC芯片,数据宽度填写16。

I/O Signaling

所有的I/O信号标准都显示为所选择的I/O信号类型。根据实际外部芯片ADC/DAC引脚的实际信号类型进行设置。

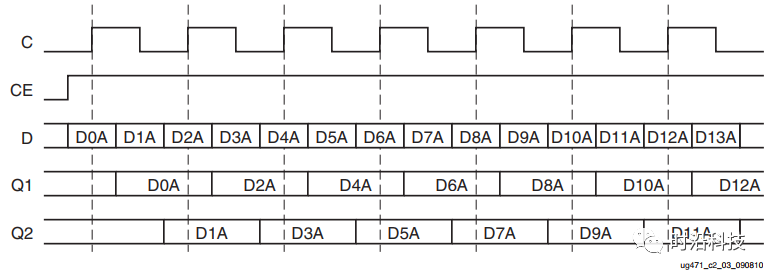

Input DDR Data Alignment

OPPOSITE_EDGE

上升沿触发的数据通过输出端Q1呈现,下降沿触发的数据通过输出端Q2呈现。

OPPOSITE_EDGE模式

SAME_EDGE

在时序图中,同一时刻输出对Q1和Q2不再是D0A和D1A,而是第一对呈现的是一对D0A和(不关心),然后下一个时钟输出一对D2A和D1A。

SAME_EDGE模式

SAME_EDGE_PIPELINED

输出对Q1和Q2在同一时刻输出。

SAME_EDGE_PIPELINED模式

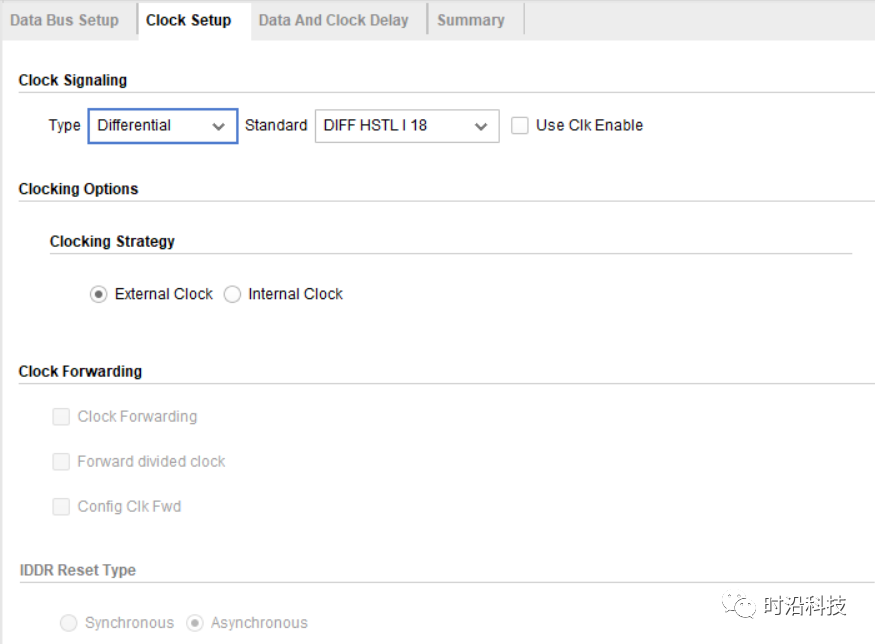

Clock Setup

Clock Setup界面

External Clock

如果在输出数据路径上设置了任何延迟,则将同样的延迟分配给时钟,使数据和时钟保持同步。

Internal Clock

如果你的时钟来自时钟输出模块,你会想要选择内部时钟,但是需要确保实例化一个MMCM来驱动时钟。

Clocking Signaling

您可以为输入时钟指定信令类型和标准。I / O信号标准将嵌入所提供的HDL源代码。

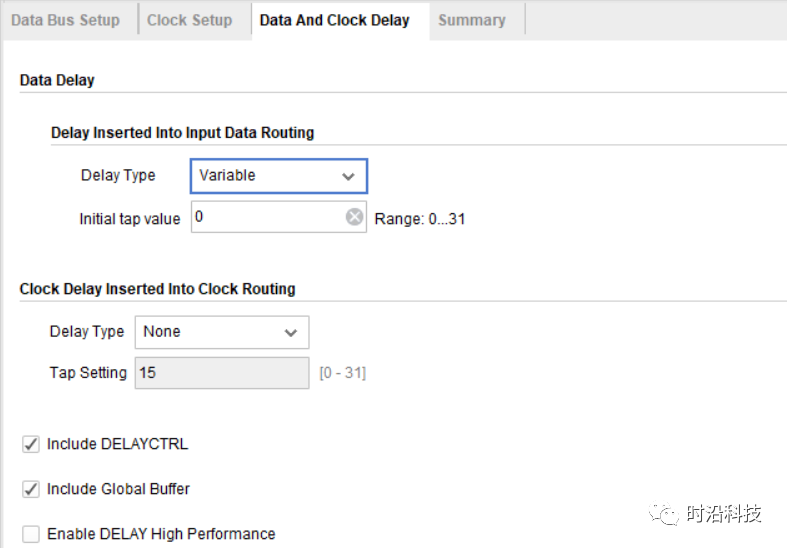

Data And Clock Delay

Data And Clock Delay界面

Delay Type

FIXED

在固定延迟模式下,延迟值由属性IDELAY_VALUE确定。一旦设置,该值不能为改变了。在此模式下使用时,必须实例化IDELAYCTRL原语。

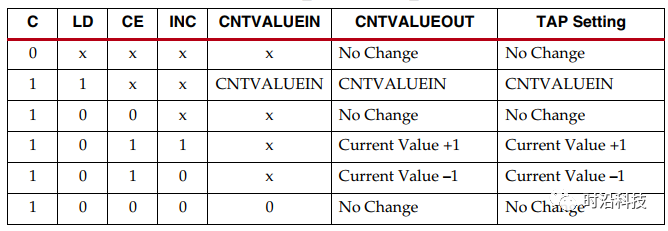

VARIABLE

在可变延迟模式下,延迟值可以通过控制信号CE和INC配置。在此模式下使用,IDELAYCTRL原语必须实例化。

VARIABLE模式延时控制

VAR_LOAD

IDELAY tap可以通过5输入位CNTVALUEIN[4:0]设置。当LD脉冲时,CNTVALUEIN[4:0]的值将是新值。作为这个功能的结果,IDELAY_VALUE属性是忽略了。在此模式下使用时,必须实例化IDELAYCTRL原语。

VAR_LOAD模式延时控制

Include DELAYCTRL

只适用于固定/可变的延迟。如果选中,则包含IODELAYCTRL在设计中实例化。

Include Global Buffer

如果选中,则在设计中实例化BUFG。当未选择包含DELAYCTRL时,没有启用BUFG以供选择。

Enable DELAY High Performance

如果启用,则设置IDELAY块的HIGH_PERFORMANCE_MODE属性为true,否则设置值为false。