本文转载自:FPGA技术实战

引言:接着上一篇继续介绍7系列FPGA收发器共享资源。本文主要介绍GTX/GTH收发器内部CPLL和QPLL锁相环时钟结构及使用,通过本文可以学习一下内容:

通道PLL(CPLL)的结构及使用

QPLL的结构及使用

1.通道PLL(CPLL)结构及使用

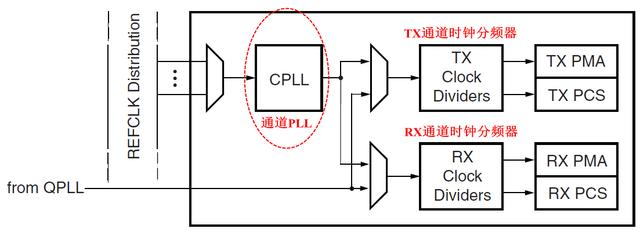

GTX/GTH收发器通道内部时钟架构如图1所示,可以看到收发器通道内部时钟主要分为CPLL、TX发送时钟分频器和RX接收时钟分频器三部分。TX时钟和RX时钟分频器允许收发器接收器和发送器操作在不同的线速率,使用不同的参考时钟输入。

图1、内部通道时钟架构

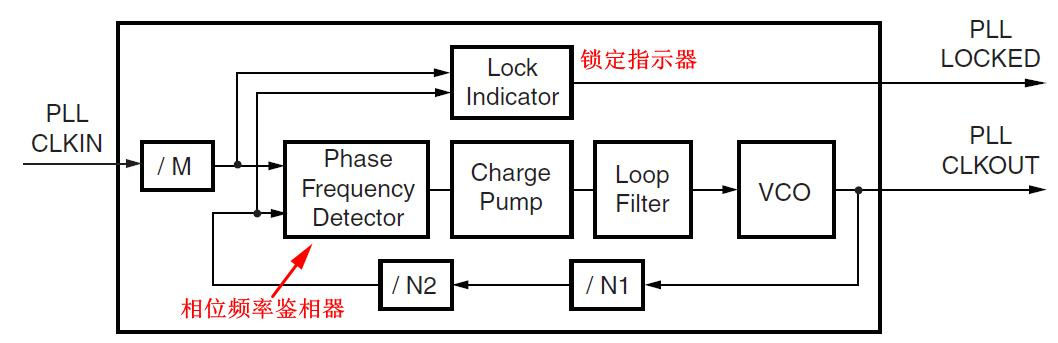

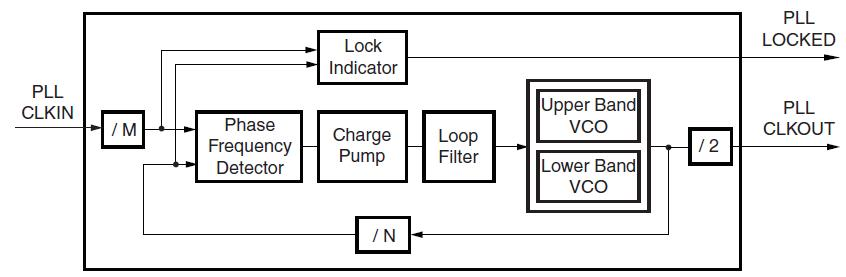

CPLL原理功能模块框图如图2所示。输入时钟在进入相位鉴相器前首先进行M倍分频。反馈分频器N1和N2决定了VCO倍频比例和CPLL输出频率。一个锁定指示器模块用于比较参考时钟和VCO反馈时钟频率以决定CPLL输出是否锁定。

图2、CPLL功能模块框图

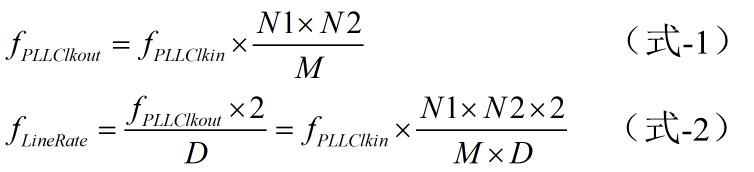

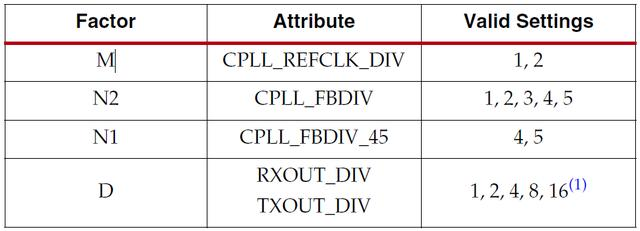

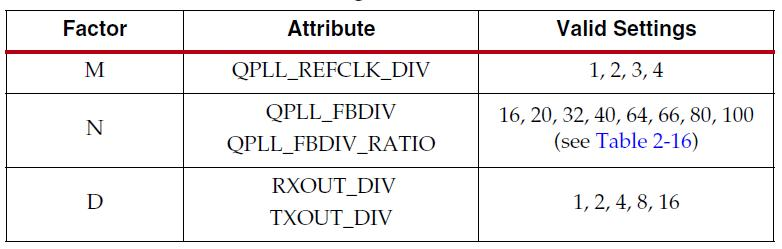

CPLL输出频率如图3中式-1所示,式-2为FPGA收发器线速率(line rate),式中D为TX和RX模块分频器因子。CPLL分频器因子如图4所示。

图3、CPLL输出频率及收发器线速率公式

图4、CPLL分频器因子

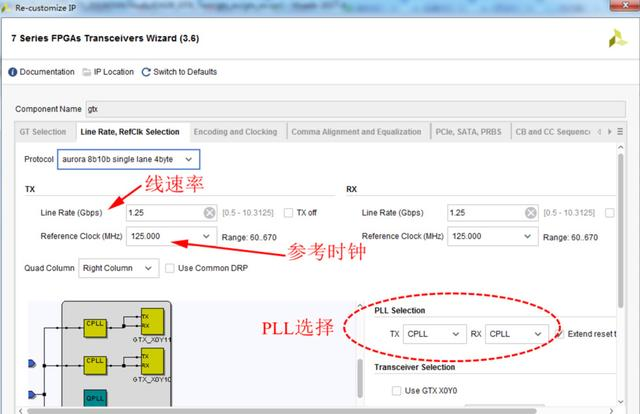

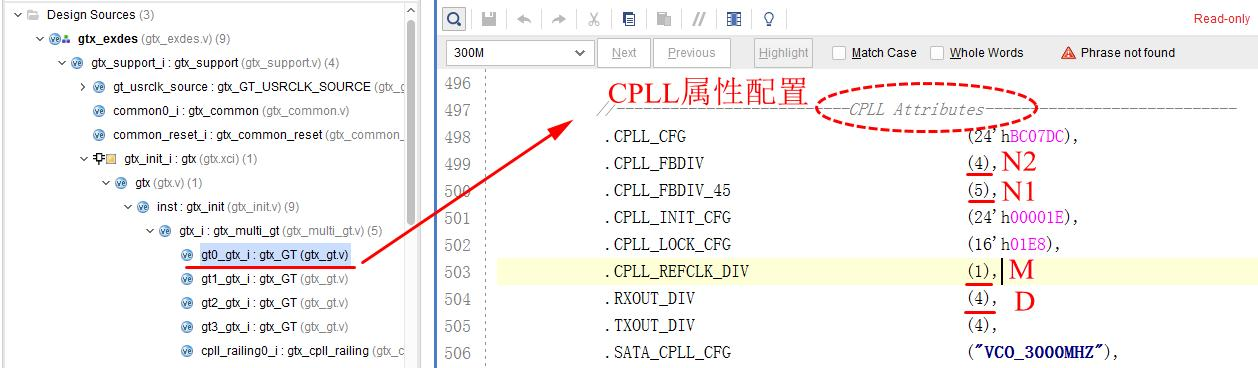

举例CPLL使用:图6显示了FPGA收发器线速率配置为1.25GHz,图7显示了与该线速率相匹配的收发器内部CPLL属性配置,根据图中公式,我们可以看到配置参数是正确的。

图6、FPGA收发器线速率配置

图7、收发器内部CPLL属性参数

2. QPLL结构及使用

QPLL为Quad内公共PLL,它可以支持的VCO最大频率比CPLL更大。当线速率大于6.6Gbps时,必须使用QPLL。QPLL的原理和CPLL操作方法很类似。图8显示了QPLL内部结构图。QPLL分频器因子如图10所示。

图8、QPLL内部结构框图

图9、QPLL输出频率及收发器线速率公式

图10、QPLL分频器因子

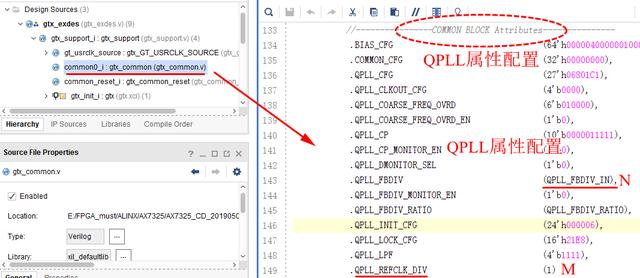

举例QPLL配置:图11显示了QPLL属性配置。由于图6没有使能QPLL,所以在图11中,未出现RXOUT_DIV和TXOUT_DIV属性配置,这点要注意。

图11、QPLL属性配置