本文来源:FpgaHome微信公众号

1. 前言

在上一篇文章里,我们介绍了如何使用DDR IP核的Native接口来读写DDR。本文我们将向大家介绍一种更简单快捷的读写DDR数据方法(至少作者自己是这样认为的)。

2. 读写DDR 的BD设计

(1) 首先建议大家新建一个工程,并进入vivado的BLOCK DESIGN (BD)设计模式。

(2) 新建一个DDR IP核,并将其设置为AXI接口,其它参数设置参考《MIG IP核的使用——DDR接口专栏(二)》。(BD模式下,DDR IP核默认都是AXI接口)

(3) 除了DDR IP核,我们还需要向工程里添加AXI InterConnect IP核、DataMover IP核,最后的连线如下图所示。

(4) 上面BD模式的连线需要注意时钟的接法。除了DataMover IP核有关cmd的管脚对应时钟域为cmd_clk时钟,其他所有信号都处在DDR IP核的ui_clk时钟域下。

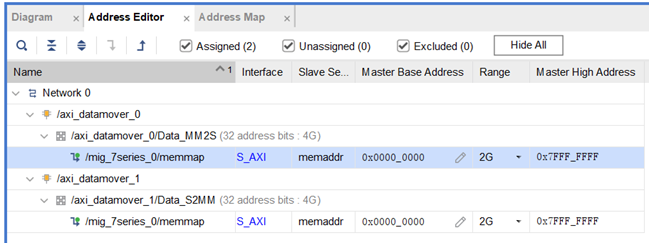

(5) 由于我们设置的DDR IP核内存大小为2GB,因此我们将两个DataMover能访问的地址范围也设为0x00000000~0x7fffffff(即2GB大小)。这样两个DataMover ip能访问整个DDR的数据空间。

至此我们已经完成了读写DDR的BD模块设计。

3.该BD设计如何工作

如果大家用过DataMover ip核的话,想必已经知道上面模块是如何工作的了。

Xilinx DataMover IP核是一种专门用于数据传输和处理的IP核,简单的说,它接收cmd总线上的读写指令,然后去与DDR相连的AXI4接口上搬移数据。下图展示了DataMover IP的读数据路径。关于DataMover的具体使用方法,可以参考Xilinx PG022手册。

上面的BD设计功能总结如下:

(1) AXI InterConnect IP使得两个DataMover都可以读写DDR的数据,扮演了缓存、仲裁的角色

(2) DataMover_0用于读取DDR的数据:rd_ddr_cmd总线接收读DDR的地址指令,指令执行后,读取到的数据通过rd_data接口输出。

(3) DataMover_1用于将数据写入DDR:wr_ddr_cmd总线接收写DDR的地址指令,wr_data接收待写入的数据,指令执行后,数据通过AXI InterConnect的S01_AXI接口写入DDR IP核。

4.总结

为何使用DataMover会使得读写DDR IP变得简单?主要原因是,用户操作DataMover的指令和数据接口均为AXI-Stream接口。因此用户不需要关心DDR IP核接口具体的读写时序,只用简单的根据AXI-Stream协议,往DataMover接口送地址指令和数据就能完成DDR数据的读写。

---------------------------------------------

参考文献:

[1] Xilinx, NavDoc, AXI DataMover. LogiCore IP Product Guide PG022.