本文转载自:十年老鸟的CSDN博客

前言

前面modelsim已经仿真成功了了DDR3的初始化,但其他端口都设置成了0,现在就需要对其读写端口进行操作了

APP端口

实际上我们也就是需要对APP端口进行读写操作,

.app_addr (app_addr),

.app_cmd (app_cmd),

.app_en (app_en),

.app_wdf_data (app_wdf_data),

.app_wdf_end (app_wdf_end),

.app_wdf_wren (app_wdf_wren),

.app_rd_data (app_rd_data),

.app_rd_data_end (app_rd_data_end),

.app_rd_data_valid (app_rd_data_valid),

.app_rdy (app_rdy),

.app_wdf_rdy (app_wdf_rdy),

.app_sr_req (1'b0),

.app_ref_req (1'b0),

.app_zq_req (1'b0),

.app_sr_active (),

.app_ref_ack (),

.app_zq_ack (),

.ui_clk (ui_clk),

.ui_clk_sync_rst (ui_clk_sync_rst),

.app_wdf_mask (0),

其中 ui_clk是给用户使用的时钟

ui_clk_sync_rst是给用户使用的复位信号

APP端口中有一部分信号是不需要管的

.app_sr_req (1'b0),

.app_ref_req (1'b0),

.app_zq_req (1'b0),

.app_sr_active (),

.app_ref_ack (),

.app_zq_ack (),

.app_wdf_mask (0),

写mask如果没有选择的需要也直接写成0。

剩下的实际上也就是对这些信号进行操作了

.app_addr (app_addr),

.app_cmd (app_cmd),

.app_en (app_en),

.app_wdf_data (app_wdf_data),

.app_wdf_end (app_wdf_end),

.app_wdf_wren (app_wdf_wren),

.app_rd_data (app_rd_data),

.app_rd_data_end (app_rd_data_end),

.app_rd_data_valid (app_rd_data_valid),

.app_rdy (app_rdy),

.app_wdf_rdy (app_wdf_rdy),

读写测试

因为已经很多优秀的博主已经写过MIG的文章,这里参考了 孤独的单刀博主的文章https://wuzhikai.blog.csdn.net/article/details/121646652?spm=1001.2101.3...

带的工程中有一个V文件,这里我直接套用在我这里进行测试

ddr3_rw.v

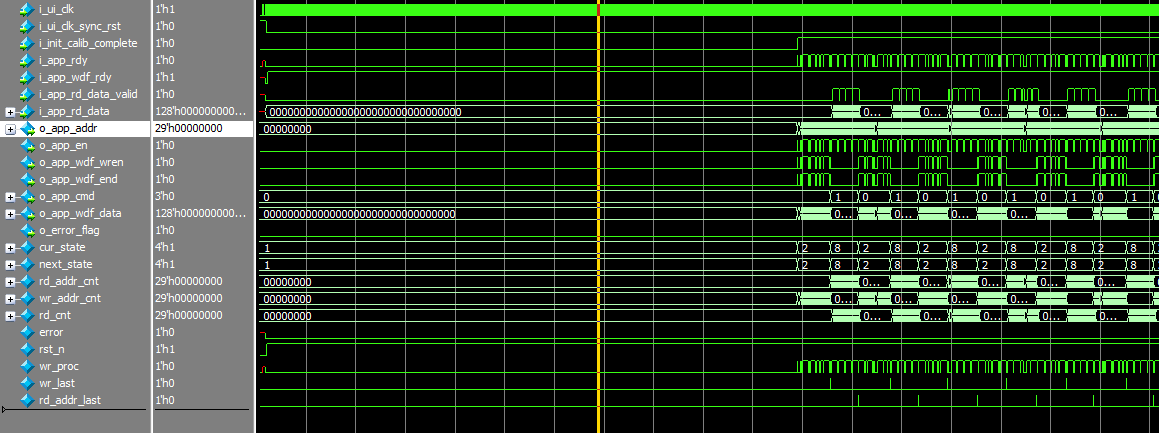

进行modelsim仿真后,读写测试正常,error指示一直为0

直接将该工程进行上板调试

抓取数据如下图,也是没有错误的