本文转载自:FPGA的现今未

在一个需要使用DDR的FPGA项目开始的时候,都会遇到DDR的管脚分配,对于搞FPGA的人来说,一般会遇到2个问题,第一个是如何分配管脚,第二个是验证你的管脚分配。

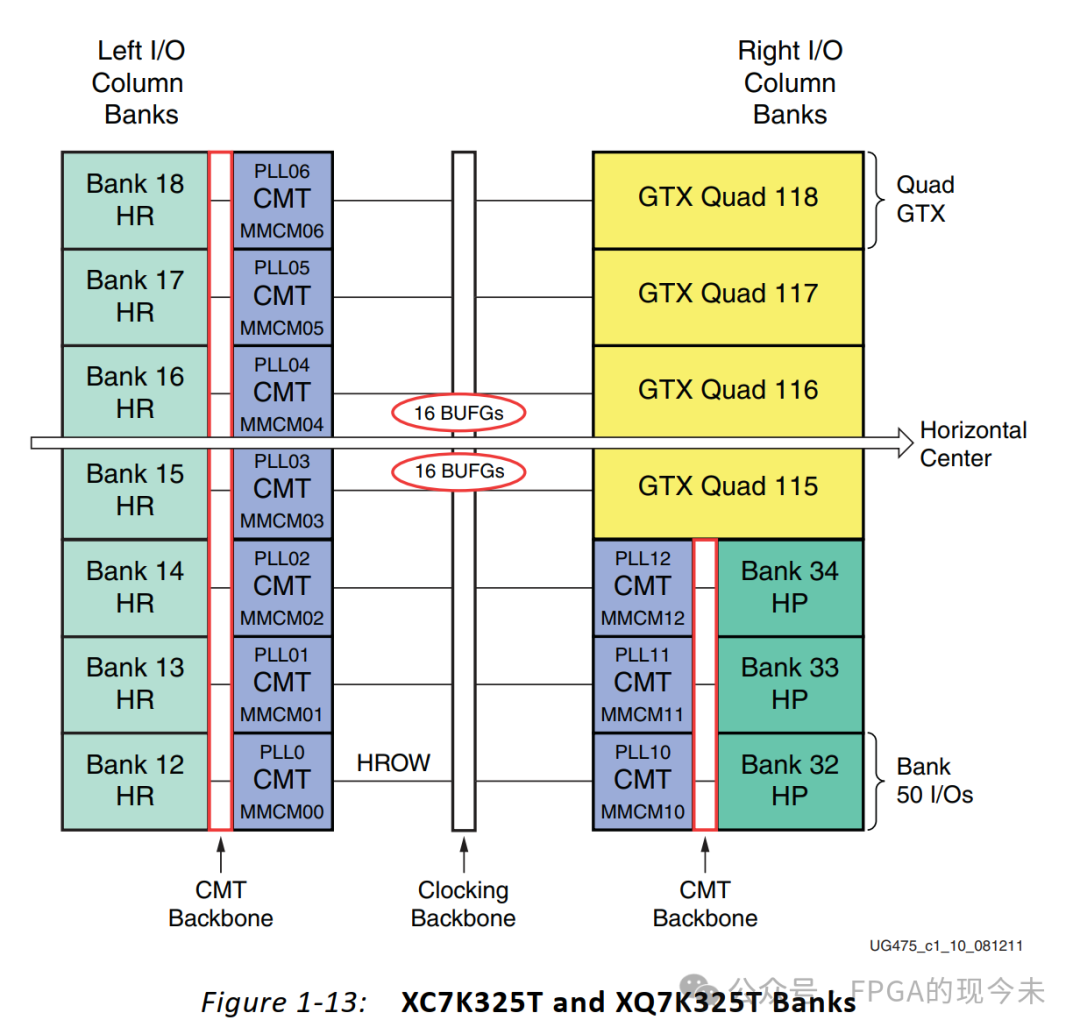

K7 325T封装

在分配DDR的管脚前,需要对FPGA芯片的封装有一些基本的了解,这里以K7 325T为例,在7 Series FPGAs Packaging UG475 (v1.19)中,可以找到所有封装的基本情况,如下图所示:

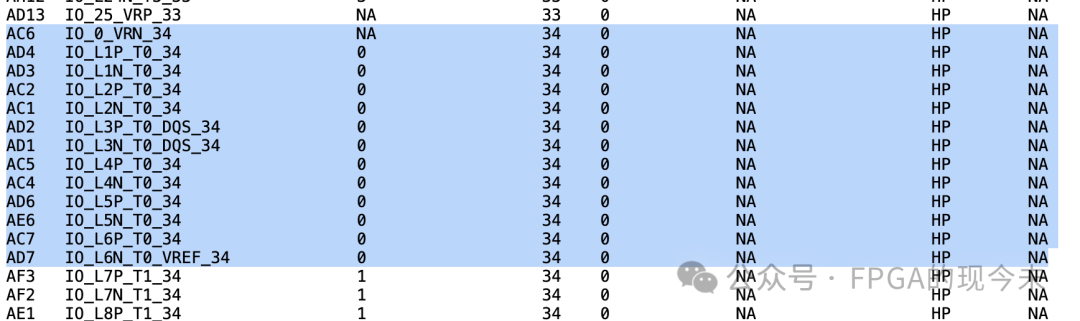

它的管脚主要分成了3类,一类是走serdes信号,如图中黄色Quad115/116/117/118这4个bank,第二种是3.3V-capable high-range (HR) banks,第三种是1.8V-capable high-performance (HP) banks。所有在DDR管脚的分配中优先考虑HP bank。

管脚的分配原则

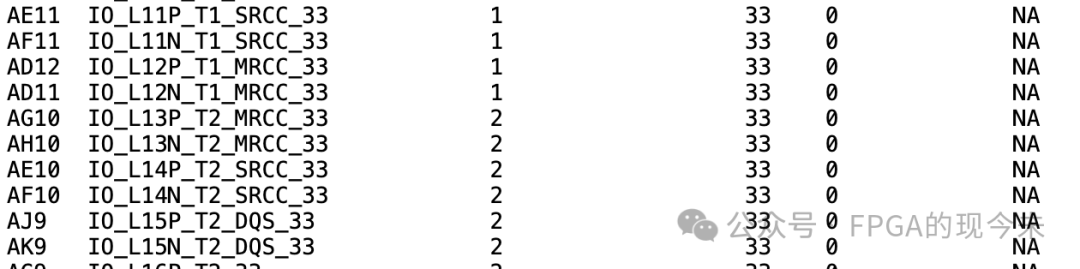

5、系统时钟和参考时钟,这里就有2种方案,用外部时钟或者是内部时钟,如果用外部时钟,无论系统时钟还是参考时钟都需要通过SR/MR CC管脚输入,如果是内部时钟,就直接通过MMCM产生。

当完成管脚分配后,验证分配的是否正确,这个时候就可以使用mig这个core来验证,即在生成mig core的时候,有一个步骤是可以输入你分配的管脚,然后点击Validate即可检测分配的结果是否正确。