本演示基于 Lattice ICE40 UltraPlus FPGA 开发板 开展。

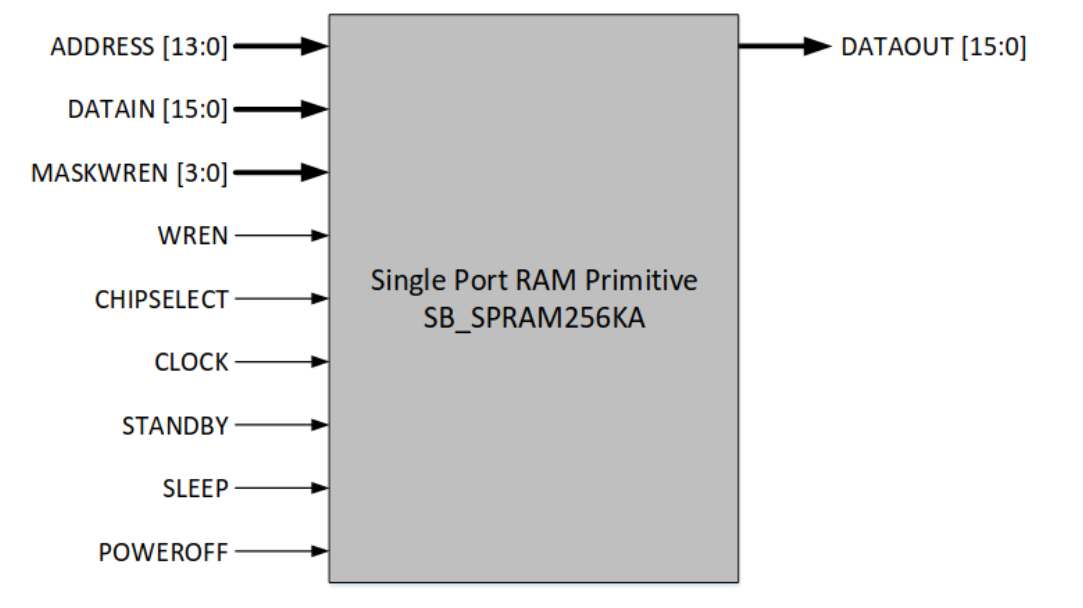

旨在通过有限状态机的设计与实现,演示如何借助下文所示的 FPGA 片内 SB_SPRAM256KA 模块,对片内 SPRAM 执行写入操作。

//Digikey Coffee Cup test of the SPRAM, using a state machine to write values in SPRAM, then

//reading them. The values written in memory is different combinations colors of a RGB led

module top(input clk, output LED_R, output LED_G, output LED_B);

reg [7:0] state;

reg [31:0] counter;

//access to spram

reg [15:0] ram_addr;

wire [15:0] ram_data_in;

wire [15:0] ram_data_out;

wire ram_wren;

parameter IDLE = 0, INIT0 = IDLE+1, INIT1=INIT0+1, INIT2=INIT1+1, INIT3=INIT2+1, INIT4=INIT3+1, INIT5=INIT4+1, INIT6=INIT5+1, INIT7=INIT6+1, RUN=INIT7+1;

reg [2:0] led;

//leds are active low

assign LED_R = ~led[0];

assign LED_G = ~led[1];

assign LED_B = ~led[2];

SB_SPRAM256KA spram

(

.ADDRESS(ram_addr),

.DATAIN(ram_data_in),

.MASKWREN({ram_wren, ram_wren, ram_wren, ram_wren}),

.WREN(ram_wren),

.CHIPSELECT(1'b1),

.CLOCK(clk),

.STANDBY(1'b0),

.SLEEP(1'b0),

.POWEROFF(1'b1),

.DATAOUT(ram_data_out)

);

initial begin

state <= INIT0;

led <= 3'b000;

counter <= 0;

end

always @(posedge clk)

begin

ram_wren <= 1'b0;

case(state)

IDLE:

begin

end

INIT0:

begin

ram_addr <= 16'b000;

ram_data_in <= 16'b001; //write red

ram_wren <= 1'b1;

state <= INIT1;

end

INIT1:

begin

ram_addr <= 16'b001;

ram_data_in <= 16'b010; //write green

ram_wren <= 1'b1;

state <= INIT2;

end

INIT2:

begin

ram_addr <= 16'b010;

ram_data_in <= 16'b011; //write yellow

ram_wren <= 1'b1;

state <= INIT3;

end

INIT3:

begin

ram_addr <= 16'b011;

ram_data_in <= 16'b100; //write blue

ram_wren <= 1'b1;

state <= INIT4;

end

INIT4:

begin

ram_addr <= 16'b100;

ram_data_in <= 16'b101; //write pink

ram_wren <= 1'b1;

state <= INIT5;

end

INIT5:

begin

ram_addr <= 16'b101;

ram_data_in <= 16'b110; //write light blue

ram_wren <= 1'b1;

state <= INIT6;

end

INIT6:

begin

ram_addr <= 16'b110;

ram_data_in <= 16'b111; //write light pink

ram_wren <= 1'b1;

state <= INIT7;

end

INIT7:

begin

ram_addr <= 16'b111;

ram_data_in <= 16'b011; //write yellow

ram_wren <= 1'b1;

state <= RUN;

end

RUN:

begin

counter <= counter + 1;

//increment address every ~1sec at 12Mhz

if(counter == 32'h1000000) begin

ram_addr[2:0] <= ram_addr[2:0] + 1;

end

if(counter == 32'h1000002) begin //wait two cycles to have data

led <= ram_data_out[2:0];

counter <= 0;

end

end

endcase

end

endmodule本演示通过有限状态机完成SPRAM 模块的数据写入与回读操作。写入内存的数据,对应开发板上 RGB LED 的不同颜色组合。写入 SPRAM 模块的颜色数据顺序为:红色、绿色、黄色、蓝色、粉色、浅蓝色、浅粉色、黄色。数据写入完成后,系统从 SPRAM 中读取这些颜色数据,并在开发板的 RGB LED 上循环显示。

相关 SPRAM 模块演示效果可参考视频。

Lattice ICE40 UltraPlus FPGA 开发板适用于多种应用场景,可在 DigiKey 平台采购。

文章来源: Lattice