文章来源:FPGA技术实战

多年来,FPGA和ASIC供应商之间一直存在着一场拉锯战解决方案。新的FPGA上引入了一些特性,随着人们对这些特性的了解,这些特性通常被强化到ASIC上,以实现更低的成本、更低的功耗和更大的容量。在新一代产品的早期,这种持续不断的反复工作通常有利于FPGA供应商,然后转向有利于ASIC供应商的长期稳定生产。

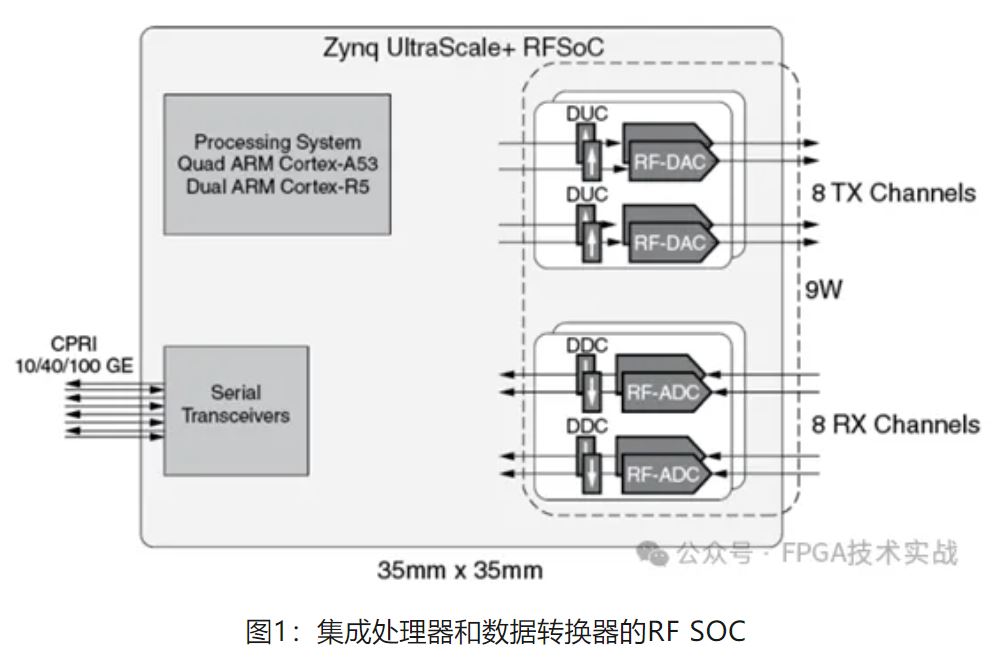

2019年,赛灵思的新产品开始改变这种状态。Xilinx为Zynq系列推出了一款具有“射频片上系统”(RFSoC)功能的升级版,它集成了ARM内核以实现某些处理器功能(降低成本和功耗),支持波束形成的可编程逻辑,并将ADC和DAC功能集成到RFSoC中。功率节省和体积缩小是非常引人注目的,特别是对于大规模MIMO(mMIMO)无线电。

2. 体系结构趋势:DFE与ADC/DAC的集成

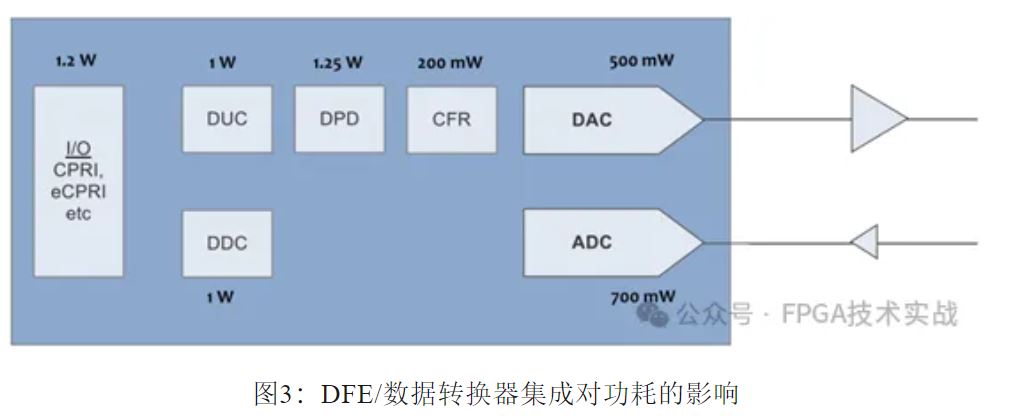

数据转换功能的集成为5G基站中的远程无线单元(RRU)提供了巨大的节能效果。对于每个JESD204通道,节省的成本大约为1W,或者对于来自天线阵列的每个数据流来说,节省的成本是不同的。在64T大容量MIMO的情况下,在250W的总散热预算中,可以节省超过60W的功耗。虽然ASIC设计可以为集成的功能提供更低的功耗,但总体解决方案的节省不太明显。

这就是数学开始变得模糊的地方。重要的指标是总散热量,而不一定是从一个优化的截面获得的效益。由于RRU中的恒压热管理,延迟了向传统ASIC的质量转换。即使是第1层网络设备供应商提供的整体解决方案,数字前端(DFE)和数据转换仍有不同的分区。目前还没有一种单一的实现方法。

注:1)图中显示了单个收发器链路100 MHz带宽的功耗估计。

在Xilinx应用示例中,需要解决的一个关键问题是JESD204接口的功耗,这是通过数据转换器与数字前端的集成来实现的,从而大大减少了JESD204B的处理。Xilinx将数字前端(DUC、DDC、DPD)与ADC和DAC集成,以消除功耗方面的开销。

处理器和数据转换器集成的另一个问题与流程节点开发的节奏有关。CMOS上的处理器逻辑稳定地向下移动到下一个工艺节点(新的ASIC将移动到7nm、5nm或更少),而数据转换器通常在领先的工艺节点上开发两到三代。(约18 nm)。

•频道带宽:带宽正在扩展。最初的5G系统通常使用100MHz,这与单个运营商能够访问的频率相对应。然而,趋势是提供支持200MHz或更高的硬件,以减少产品版本和简化制造(这对网络OEM和组件供应商都是一个好处)。通常,3.4-3.6GHz和3.6-3.8GHz产品可以满足大多数客户的要求。然而,即将在美国举行的C波段拍卖会将为5G使用分配高达280MHz的带宽,这将进一步提高RRU的性能要求。

4. FPGA、ASIC和RFSOC

在前面关于技术趋势的部分中,我们已经讨论了RFSoC集成的主要推动力包括:降低功耗、成本和板上尺寸。

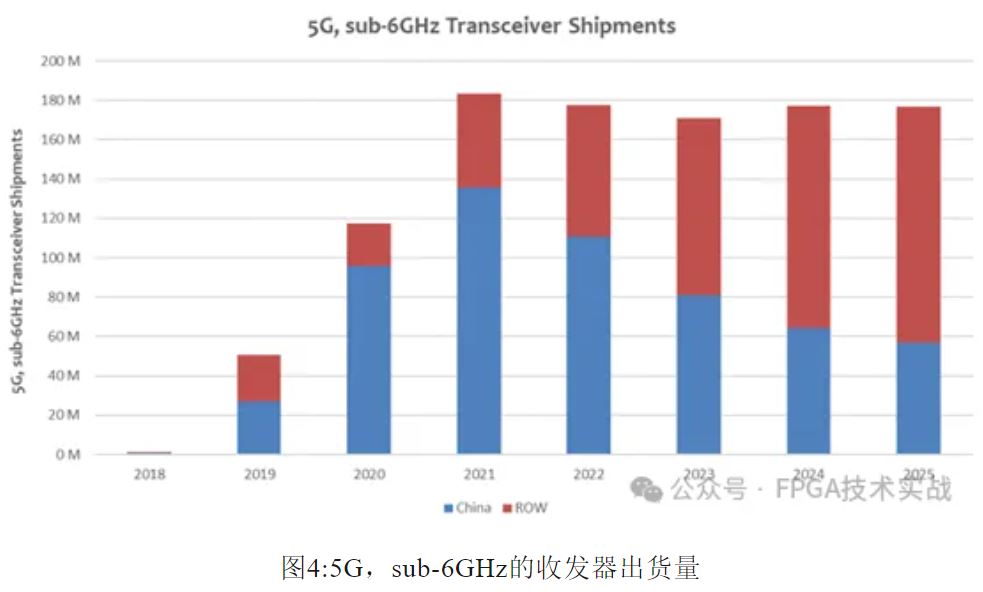

此外,基于5G引入的新使用案例,RAN需要更大的灵活性。从2019年开始,5G网络的首次推出主要集中在移动用户,即智能手机中。这被称为eMBB(增强型移动宽带)应用程序。在谈到整个5G网络时,与4G的一大区别是增加了两个新应用:IoT和URLLC(超可靠低延迟连接)。从长远来看,这些新的应用程序有望在B2B领域带来可观的收入…但这还没有发生。它将依赖于目前正在部署的5G基础设施,并可能在此基础上进行扩展。RRU必须满足需要部署在建筑物中或作为租用的专用网络,通过C-RAN架构连接到主网络。这些不同用例的数据需求还不完全清楚,但很有可能与当前eMBB系统的方法(和设计)有所不同。数据管理的灵活性将允许这些新应用程序的顺利支持和引入。

不难看出5G网络带来的额外复杂性。每一代电信都通过更好的语音质量或更多的数据来改善用户体验,5G已经在做这件事了。然而,我们今天看到的正在部署的5G网络实际上是将被添加和扩展的基础设施。这看起来像是宏基站、室内RRU、中继器和小型小区。它都是5G,但每个都有不同的要求。支持这种多样性所需的处理器必须基于每个需求灵活,并且能够灵活地适应仍在发展的用例,在系统部署之前,我们将无法真正理解这些用例。

注:以上内容翻译自《FPGA vs ASIC: 5G changes the equation》