Zynq UltraScale+ PS MIO可能在上电期间出现高位毛刺

judy 在 周六, 05/06/2023 - 17:13 提交

Zynq UltraScale+ PS MIO 可能在 VCCO_PSMIO 电源上电缓升期间输出高位毛刺

Zynq UltraScale+ PS MIO 可能在 VCCO_PSMIO 电源上电缓升期间输出高位毛刺

随着最新版GB-15084国家强制安全标准的发布和实施,智能汽车市场打开了电子后视镜的新机遇

全新 AU7P 和 ZU3T 器件基于 16nm FinFET 工艺,适用于低功耗、高每瓦性能的小型应用。

本文描述了UltraScale™ FPGA的BPI配置和闪存编程技术。

雪湖科技聚焦于智慧交通的的激光雷达 AI 感知,推出了嵌入式 AI 感知边缘计算机 LiDAREYE™。该平台内置赛灵思 Zynq® UltraScale+™ ZU7EV 和雪湖科技自研的 AI 硬件加速引擎与 AI 算法,专为激光雷达 3D 点云的 AI 感知计算而设计

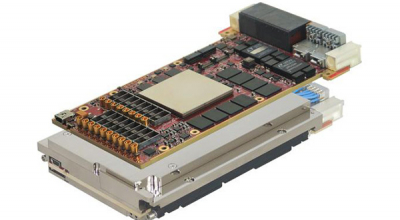

Abaco Systems 基于AMD-赛灵思抽象 Shell 设计流程推出硬件开发套件( HDK ),将 DFX 技术推向更高水平,使其可以向最终客户交付预编译且时序收敛的 Shell,从而助力其促进协作、提高编译效率、降低许可成本。

快手将赛灵思 Alveo 加速器卡应用于 ASR 服务,是 FPGA 在国内大规模直播及短视频自动语音识别场景落地的首个成功案例。

如果要在 UltraScale+ 器件中执行手动眼扫描,重新排列程序会导致 PCIe 重新训练,降至第一代产品的速度,并停留在那里。

FPGA 能够自适应生成定制计算架构,以前所未有的灵活性、更短的设计周期、更低的开发成本,助力各类机器人应用。机器人是一种复合系统,它由感知周边环境的传感器、根据感知采取行动的致动器和负责处理数据的计算构成,从而对其应用做出连贯一致的响应。在很大程度上,机器人技术是一种系统集成的艺术,在软件和硬件方面皆是如此。