Xilinx FPGA加密方案

judy 在 周一, 01/17/2022 - 16:11 提交

Xilinx 7系列采用的是AES-CBC块加密的模式,而UltraScale & UltraScale+采用的是AES-GCM流加密模式,效率更高且自带GMAC信息校验码,用以校验密文完整性。加密方式及操作上大同小异,本文仅介绍7系列和Zynq-7000裸机打包bin文件的加密方法。

Xilinx 7系列采用的是AES-CBC块加密的模式,而UltraScale & UltraScale+采用的是AES-GCM流加密模式,效率更高且自带GMAC信息校验码,用以校验密文完整性。加密方式及操作上大同小异,本文仅介绍7系列和Zynq-7000裸机打包bin文件的加密方法。

在Xilinx的DisplayPort 1.4 IP的文档中,提到支持的器件为Ultrascale/Ultrascale+/Versal系列,但很多的客户基于成本的考量希望能在7系列的器件中实现DP1.4。

本应用说明提供了一个系统,该系统旨在通过利用每个串行千兆位收发器内的功能来取代外部压控晶体振荡器(VCXO)电路。

本文描述了使用 Vivado工具为 7 系列 FPGA 生成和编程加密位流和加密密钥的过程。

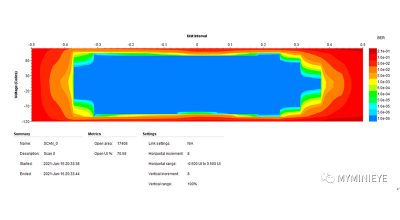

IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。

如果VCCO0连接至2.5V或3.3V,CFGBVS连接至VCCO0。如果VCCO0连接至1.5V或1.8V,CFGBVS连接至GND。建议bank0、bank14、bank15的VCCO电压一致,避免出现I/O Transition at the End of Startup

Xilinx-7系列FPGA主要包括:Spartan®-7、Artix®-7、Kintex®-7、Virtex®-7。其性能、密度、价格也随着系列的不同而提升。和前几代FPGA产品不同的是,7系列FPGA采用的是统一的28nm设计架构,客户在不同子系列的使用方式上是统一的,消除了不同子系列切换使用带来的不便。当然Kintex®-7、Virtex®-7两个系列后续还有20nm和16nm设计架构。

区别于传统的一根信号线一根地线的做法,差分传输在两根线上都传输信号,这两个信号的振幅相同,相位相反,在这两根线上的传输的信号就是差分信号。信号接收端通过比较这两个电压的差值来判断发送端发送的逻辑状态。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

AXI4 从站接口将 AXI4 事务映射到 UI,以向内存控制器提供行业标准总线协议接口。UI 块向用户提供 FPGA 逻辑块。它通过呈现平面地址空间和缓冲读写数据来提供对本机接口的简单替代。

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。