作者: Brian Liu,本文转载自: Ingdan FPGA微信公众号

1. 概述

Xilinx FPGA从7系列开始,设备有了片上高级加密标准(AES)解密逻辑,提供了高度的设计安全性。加密的Xilinx FPGA设计不能被复制或反向工程用于其他FPGA。

Xilinx FPGA负责加密的AES系统由基于软件的位流加密和片上位流解密组成,加密密钥由片上的专用内存存储。对于7系列或UltraScale& UltraScale+,Xilinx Vivado工具可用于生成加密密钥和加密的比特流;对于Zynq系列,XilinxSDK/Vitis的bootgen工具可用于生成加密密钥和加密的打包文件。密钥可由工具随机生成也可以由用户指定。

Xilinx FPGA将加密密钥存储在片上专用RAM中,可以选择存放在BBRAM或eFUSE。以7系列为例,加密密钥只能通过JTAG端口编程到设备上;7系列设备执行反向操作,在配置时对传入的比特流进行解密。7系列AES加密逻辑采用256位加密密钥。片上AES解密逻辑不能用于比特流解密之外的任何用途,AES解密逻辑对用户设计不可用,不能用于解密配置比特流以外的数据。

Xilinx 7系列采用的是AES-CBC块加密的模式,而UltraScale & UltraScale+采用的是AES-GCM流加密模式,效率更高且自带GMAC信息校验码,用以校验密文完整性。加密方式及操作上大同小异,本文仅介绍7系列和Zynq-7000裸机打包bin文件的加密方法。

2. 7系列AES加密

2.1 AES

7系列FPGA加密系统采用AES加密算法,AES是由美国国家标准与技术研究所(NIST)和美国商务部支持的官方标准。具体标准请参考:https://csrc.nist.gov/publications/fips/fips197/fips-197.pdf 。7系列FPGA AES加密系统使用一个256位的加密密钥一次加密或解密128位的数据块。根据NIST的说法,一个256位的密钥有1.1x10的77次方种可能的组合。对称加密算法(如AES)使用相同的密钥进行加密和解密,因此,数据的安全性依赖于密钥的保密性。

2.2 实现框图

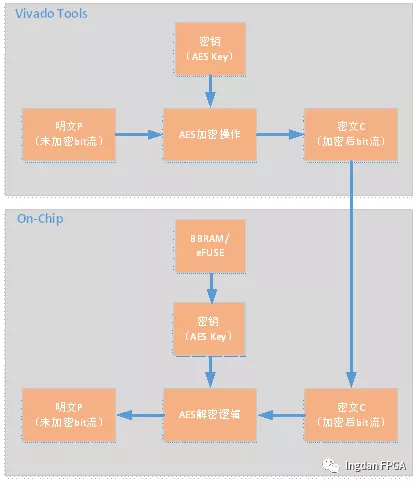

Xilinx 7系列加密解密框图由图2-1示。

图2-1 Xilinx 7系列AES加密解密实现框图

如图2-1所示,Vivado工具负责根据用户指定的密钥对bit流进行AES加密,同时将密钥写入FPGA片上的专用内存中;7系列在加载加密后的bit流时,会根据用户设置的密钥通过片上的AES解密逻辑进行AES解密,从而还原得到器件可以识别的未加密bit流。

2.3 AES实现步骤

2.3.1 生成KEY和加密后的bitstream

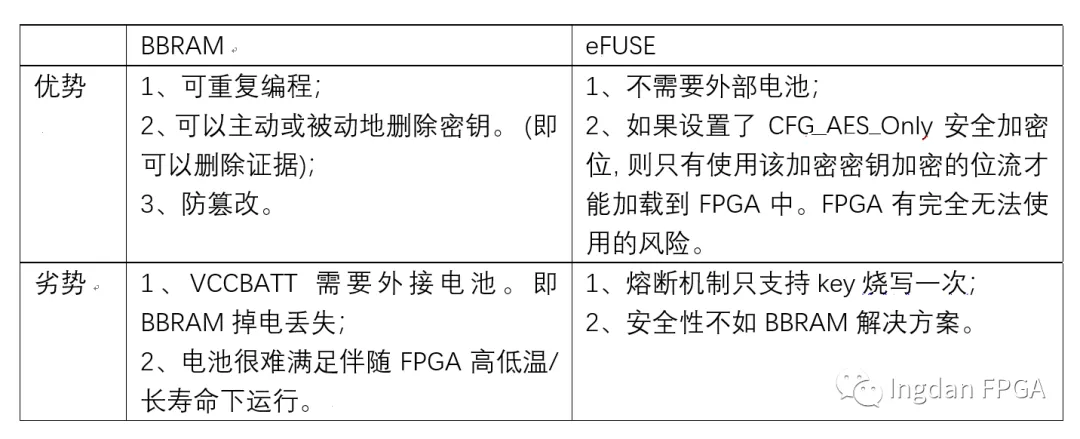

在此之前,我们先要清楚BBRAM和eFUSE之间的区别,以方便我们做相应的配置。BBRAM和eFUSE的比较如表2-1所示。

表2-1 BBRAM和eFUSE的的比较

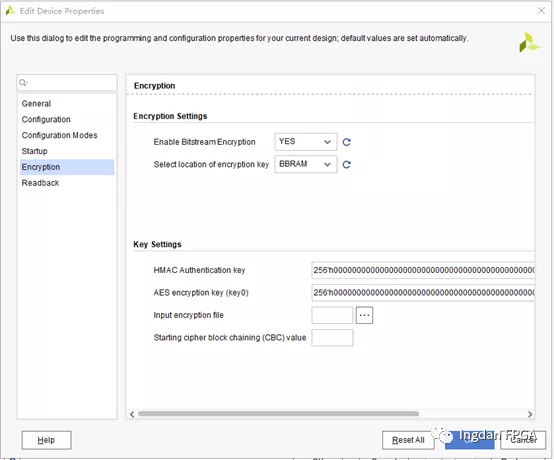

配置bitstream属性,选择Enable Bitstream Encryption;指定密钥key存放方式(BBRAM或eFUSE);提供HMAC key、AES key以及AES的初始向量。如图2-2所示:

图2-2 bitstream配置界面

除了通过以上GUI配置,还可以通过直接编写XDC约束文件达到同样目的。

图2-3 XDC约束文件

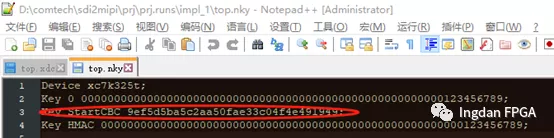

如果用户没有在GUI或XDC中指定,工具会在伴随bit流自动生成的.key文件中随机生成。

用户通常需要提供三个向量,分别为:

A. hkey(HMAC key):FPGA片上支持keyed-Hash Message Authentication Code (HMAC),提供AES单独解密额外的安全性。对于HMAC,具体标准请参考:https://csrc.nist.gov/publications/detail/fips/198/1/final

B. AES key:即256bit密钥(最重要)。

C. StartCBC:128bit AES初始向量。

图2-4 key文件中随机生成的StartCBC

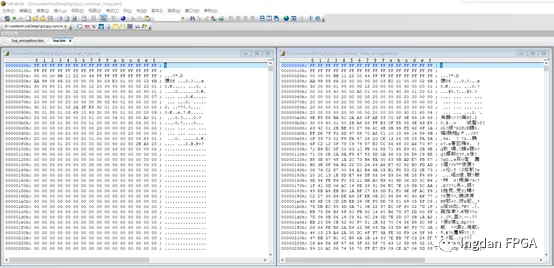

配置完成后,即可以生成加密后的bit流,并通过JTAG、SPIFLASH等方式加载到FPGA。当然,此时片上的AES解密逻辑不知道正确的密钥因此FPGA无法正常启动。加密和未加密的bit流对比如下:

图2-5 加密与未加密的bit流对比

2.3.2 通过JTAG将密钥写入片内

如前文提到的,根据bit流的配置,选择将key写入BBRAM或eFUSE中。

图2-6 烧写key

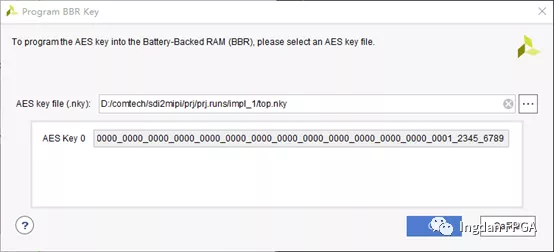

我们以BBRAM为例(如果客户最终选择Efuse也强烈建议用户先在BBRAM上验证好)。选择ProgramBBR Key,并指定工程bit流文件所在路径下的.key文件。密钥值为之前设置的256‘h123456789。如下图所示:

图2-7 烧写key到BBRAM

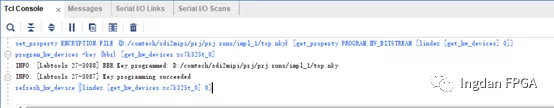

点击OK即可将密钥烧写至BBRAM,Tcl Console会有相应打印:

图2-8 key烧写成功的打印

2.3.3 验证

用户可以尝试单独改变vivadobit流配置端的AES密钥或片上BBRAM的密钥进行验证,程序将不能正常加载。

此时,无论是从spi flash重新加载加密后的程序还是JTAG烧写加密后的程序,程序都能通过AES解密逻辑解密并正常执行。

2.3.4 eFUSE

eFUSE是一种非易失的一次性可编程技术,是通过熔丝技术来实现不可逆。如果对寄存器的访问被禁用,则无法重新启用该寄存器。FPGA逻辑只能访问FUSE_USER寄存器值。所有其他的eFUSE位都不能从FPGA逻辑访问。

所以用户在配置和使用eFUSE的时候要小心谨慎,注意两点:

A. 确保密钥正确且不会再修改后再烧写到 eFUSE;

B. 除非清楚eFUSE相关寄存器的真正含义,否则不要轻易修改寄存器的值。尤其是eFUSE Control Register的CFG_AES_Only,如果该位置1,则片上会强制执行AES解密操作,一旦密钥忘记或弄丢,这片FPGA就无法再使用了。

3. ZYNQ-7000 AES加密

3.1 生成key和加密后的boot.bin

与7系列的方法类似,key文件的生成有两种方式:

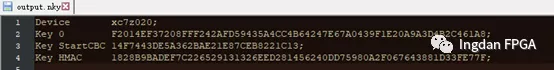

A. 手动编辑,根据以上.nky文件格式对里面的内容进行修改,主要修改key 0 即可;

B. 使用Vitis或SDK的bootgen工具生成:

图3-1 key文件的内容

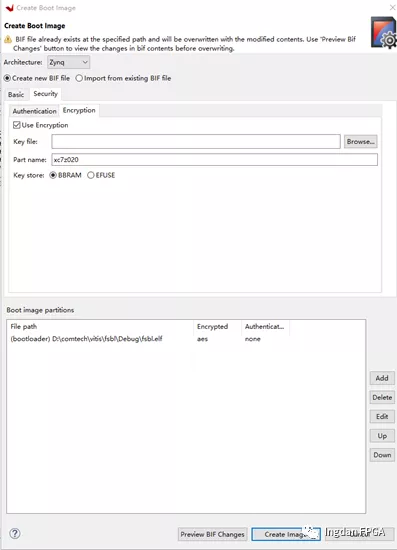

以Vitis的环境为例,打开一个Vitis工程,并选择工具栏中的Xilinx Tools->Creat BootImage如图3-2,选择加密选项、添加boot.bin打包所需要的文件。

图3-2 CreatBoot Image加密界面

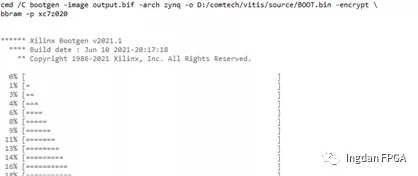

由于没有指定key file,同时又对fsbl.elf 文件打包加密,所以Vitis会自动生成一个.nky的加密文件在生成打包文件的目录内。生成加密文件过程中的打印信息可以看到bootgen的命令:

图3-3 Console打印

此时生成的boot.bin即为加密后可供烧写的打包文件。

3.2 通过JTAG将密钥写入片内

该步骤与7系列的操作方式一致,请参考2.3.2章节。

4. 利用DNA自定义加密

Xilinx 针对7系列或7系列以上的设备设计了具有片上高级加密标准(AES)解密逻辑的功能,提供了高度的设计安全性。但同时对于某些客户也有不方便的地方:

A. BBRAM方式需要外接电池才能保证掉电重启后能正常工作,同时电池往往难以匹配FPGA的工作寿命和工作环境;

B. eFUSE的熔断机制决定了key只能烧写一次,不可更改;

C. 对小客户的批量生产不友好;

D. Spartan-6等老型号芯片不支持;

基于这些原因,我们可以利用Device DNA(唯一ID)设计一种自定义的并且适合批量生产的加密方式。

4.1 自定义加密流程图

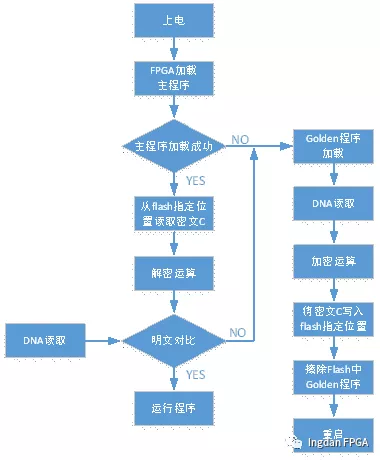

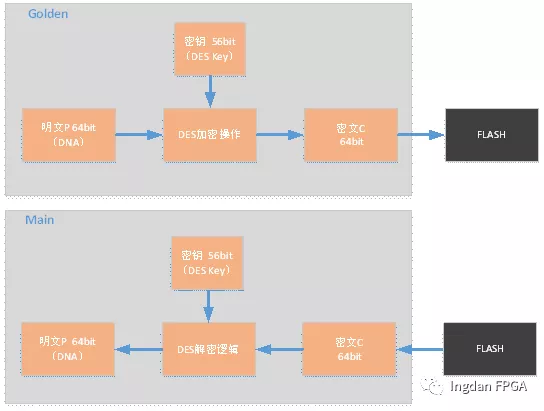

一种适合批量烧写的自定义加密流程如图4-1所示:

图4-1 加密流程图

如上图所示,这种加密方式需要应用到Xilinx FPGA的multi-boot特性,因此,flash中存在两份程序,一份为负责加密运算的Golden程序,而另一份则为包含了解密运算的主程序。除此之外,flash中还需要指定一片空间存储密文。

4.2 DNA读取

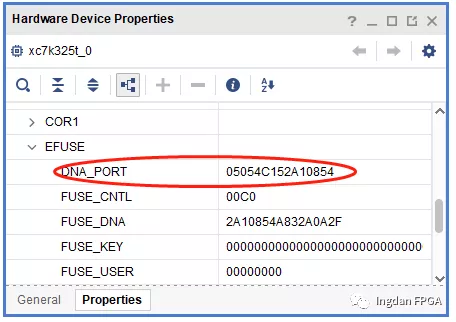

Xilinx每一个FPGA都有一个独特的ID,也就是DeviceDNA,在FPGA芯片生产的时候就已经写死在芯片的eFUSE寄存器中,因为使用的是熔断技术所以具有不可修改的属性。在7系列及之前的设备,DNA的ID位宽都是57bit;在Xilinx的Ultraslace架构下DNA的位宽为96bit。通过JTAG可以访问到DNA的值,如下图所示:

图4-2 JTAG读取DNA

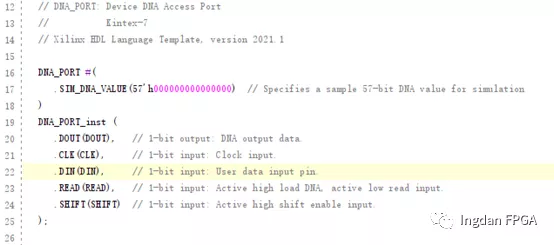

本设计中需要使用原语读取DNA,以7K325T为例,原语及端口说明如下图所示:

图4-3 DNA原语

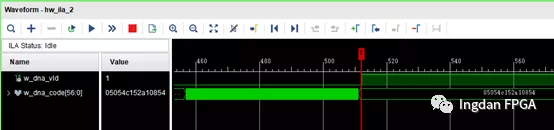

我们只需要设计一个串行接收的逻辑即可将读取到的DNA转换成57bit的并行数据,读取到的DNA与图4-2 JTAG读取到的DNA一致。

图4-4 原语读取DNA观测信号

4.2 加密/解密

加密/解密算法可以使用AES或DES等对称算法,对于7系列或7系列以下的型号,需要自行设计AES或DES的加密/解密逻辑;而对于UltraScale &UltraScale+的设备,Xilinx提供有AES的IP core,可以直接应用。本文仅介绍相对简单的DES加密/解密逻辑。

DES算法全称为Data Encryption Standard,即数据加密算法,它是IBM公司于1975年研究成功并公开发表的。DES算法的入口参数有三个:key、des_in、mode。其中Key为56位,是DES算法的工作密钥;des_in为64位,是要被加密或被解密的数据;mode为DES的工作方式,有两种:加密或解密。

图4-5 加密和解密框图

如图4-5所示,Multi-boot中的Golden程序负责提取DNA作为明文,并配合用户自定义的密钥进行DES的加密操作,再将加密后的密文写入flash中。

而Multi-boot中的主程序则完成对称的镜像操作,将flash中的密文读取,并配合用户自定义的密钥进行DES的解密操作,然后还原成明文。

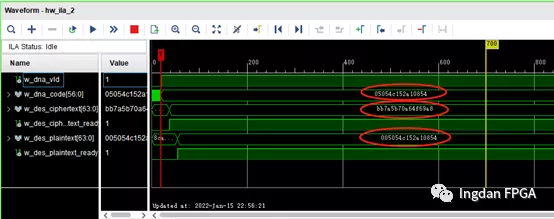

下图通过顶层调用DNA的读取、DES加密、DES解密来验证数据通路。

图4-6 顶层添加模块测试

ILA抓取的波形如下图:

图4-7 加密/解密数据波形

由ILA抓取的波形可以验证DES模块的对称性。

4.3 其他

除了DNA读取模块和加密/解密模块,还需要设计spi flash的控制器,可以通过verilog实现,也可以通过microblaze的软核实现。这里推荐用microblaze的方式来设计。具体不再阐述。

加密需要涉及的MultiBoot操作可以参考往期的《Xilinx FPGAde Multiboot功能介绍和实现》。

批量生产时,flash里面烧写统一的包含Golden和Main的MCS文件,然后再贴片至各个机器。每台机器一旦上电,Golden便会写入密文到flash并自擦除,实现flash与FPGA配合的唯一性,达到加密的目的。

如果您在FPGA加密方面有疑问,欢迎联系:

simonyang@comtech.com.cn

charlesxu@comtech.com.cn