描述

提供给7系列FPGA收发器中PLL的参考时钟的质量可以极大地影响发送抖动和接收抖动容限的性能。参考时钟的抖动或相位噪声在决定这种性能方面起着重要作用--相位噪声是首选的规范方法,因为它允许设计者纳入基于时间的抖动规范可能会忽略的各种频率成分。

本回答记录包含 Xilinx 根据所使用的 PLL 设置推荐的参考时钟相位噪声限制。

解决方案

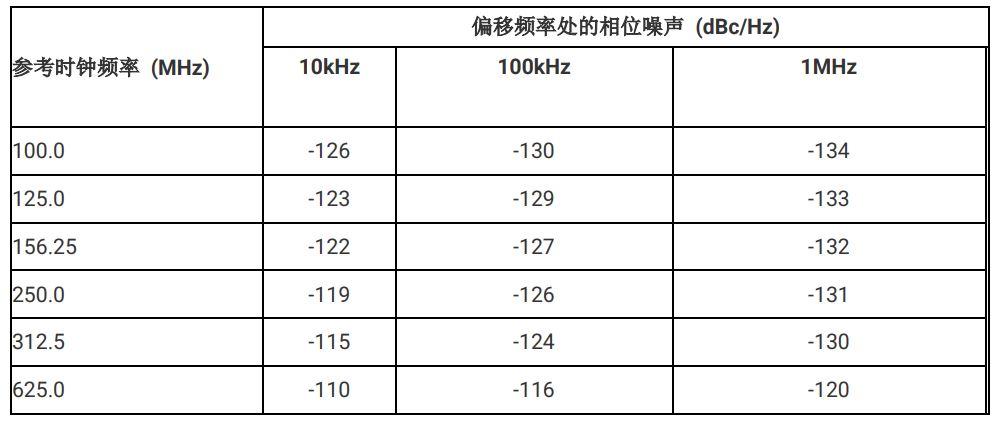

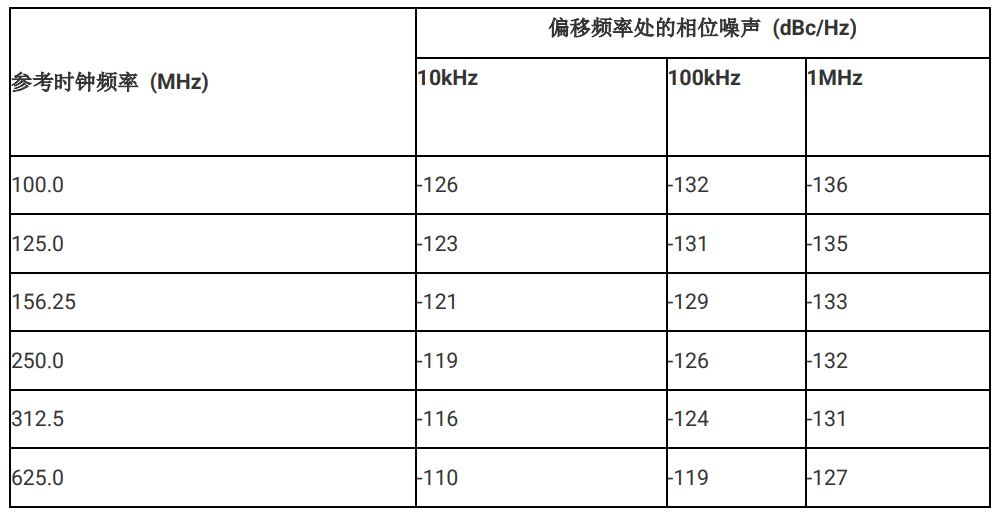

根据所使用的参考时钟,需要应用不同的掩码。下表描述了参考时钟相位噪声不应超过的模板点。如果参考时钟确实超过了这些掩码,则会导致 TX 数据出现额外的抖动。

对于 7 系列 GTX 和 GTH 收发器,下表提供了 QPLL 和 CPLL 的相位噪声掩码。对于 7 系列 GTP 收发器,CPLL 表提供相位噪声掩码。

QPLL:

CPLL:

注1:如果你想要的参考时钟频率没有在上表中列出,请使用最接近的参考时钟频率的相位噪声掩码。

注2:一些支持的协议可能有不同的要求。例如在PCIe的情况下,CDR已经被优化以支持同步模式和SSC。对于PCIe设计,用户应该检查REFCLK的质量是否符合PCIe参考时钟的规范。