SPI总线verilog hdl实现

demi 在 周五, 10/18/2019 - 15:51 提交

SPI总线传输只需要4根线就能完成——SCK(Serial Clock):SCK是串行时钟线,作用是Master向Slave传输时钟信号,控制数据交换的时机和速率;MOSI(Master Out Slave in):在SPI Master上也被称为Tx-channel,作用是SPI主机给SPI从机发送数据......

SPI总线传输只需要4根线就能完成——SCK(Serial Clock):SCK是串行时钟线,作用是Master向Slave传输时钟信号,控制数据交换的时机和速率;MOSI(Master Out Slave in):在SPI Master上也被称为Tx-channel,作用是SPI主机给SPI从机发送数据......

Verilog-2001中新增了语句generate,通过generate循环,可以产生一个对象(比如一个元件或者是一个模块)的多次例化,为可变尺度的设计提供了方便,generate语句一般在循环和条件语句中使用,为此,Verilog-2001增加了四个关键字generate,endgenerate, genvar, localparam。

Verilog中提供了四种循环语句,可用于控制语句的执行次数,分别为:for,while,repeat,forever。其中,for,while,repeat是可综合的,但循环的次数需要在编译之前就确定,动态改变循环次数的语句是不可综合的。forever语句是不可综合的,主要用于产生各种仿真激励。

一个程序块可以有多个initial和always过程块。每个initial和always说明语句在仿真的一开始同时立即开始执行;initial语句只执行一次,而always语句则不断重复的活动着,直到仿真结束。

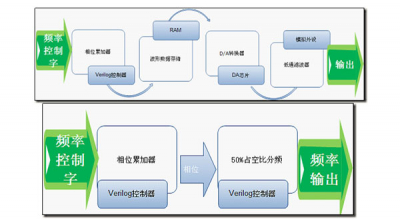

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。首先讲述DSS(直接频率合成法)的原理。DDS是重要的频率合成方法,在波形发生器中有极其重要的应用。DDS主要由几部分组成:a) 相位累加器;b) RAM数据读取;c) D/A转换器;d) 低通滤波器。

连续赋值语句是Verilog数据流建模的基本语句,用于对线网进行赋值,等价于门级描述,是从更高的抽象角度来对电路进行描述。连续赋值语句必须以关键词assign开始。

一次常规调试中发现上电后交换机多个口同时打流会导致卡死的现象,最后一步步分析问题出现的原因是位宽不够导致的溢出。

在设计仿真激励文件时,为了满足和外部芯片接口的时序要求,经常会用到延时赋值语句,由于不同的延时赋值语句在仿真过程中行为不同,会产生不同的激励输出,如果不认真区分不同表达式引起的差异,就可能产生错误的激励,无法保证仿真结果的正确,本文就是区分各种延时赋值语句的差异,并给出比较结果。

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

随着开源的MCU源代码越来越多,也逐渐的影响着嵌入式系统开发的思路,出现了两种以前不常见的设计思路。第一,原本需要购买一颗MCU芯片的设计,现在直接考虑购买一颗带有MCU硬核的FPGA(如ZYNQ系列FPGA)替代,既有MCU的功能,又有接口可编程的能力,更加的灵活......