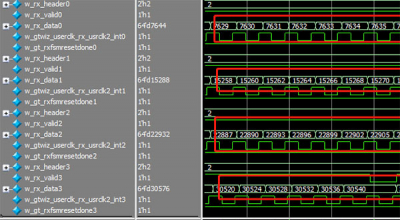

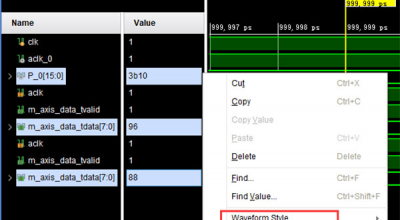

ZYNQ PS与PL通信之DMA

judy 在 周四, 08/11/2022 - 09:46 提交

本文先介绍集中PL与PS的通信方法,然后重点介绍通过DMA实现PS与PL通信。

本文先介绍集中PL与PS的通信方法,然后重点介绍通过DMA实现PS与PL通信。

针对各种Xilinx UltraScale+ FPGA和自适应片上系统(SoC)应用进行优化的定制解决方案

FIFO 通常用于跨时钟域,因此是双时钟设计。换句话说,该设计使用两个时钟

新版petalinux生成的u-boot是通过boot.scr来加载linux kernel的。如果我们用petalinux工程默认配置和下面命令生成boot image并从flash启动

在查看Xilinx KINTEX-7 FPGA 存储器资源时,你会发现它的FIFO生成器支持两种读选项模式——标准读取操作和FWFT读取操作。

10.1376G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对serdes例程,参考时钟为153.6MHz

在vivado 2021.2的VCK190 boardfile里DDR4-DIMM的DQ width被限制为64bit,不能使能ECC功能

在FPGA的设计里,RR(Round-Robin)调度是一个非常重要的话题。所谓RR调度就是从多个队列中公平地选一个队列进行处理。

本实验要完成利用vivado中的DDS IP核对两个正弦波进行混频,实现数字下变频或者上变频。

一个线速率为3.072G的,输入为20bit,输出为20bit的无协议无编码的4对serdes例程,参考时钟为153.6MHz