Vitis 2020.x - Ubuntu GDB内核调试

judy 在 周日, 04/24/2022 - 14:35 提交

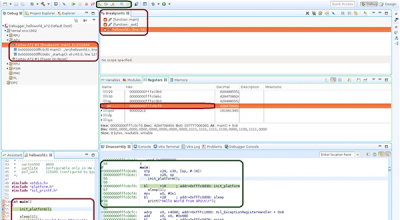

在Ubuntu系统中,当试图在内核代码中设置断点的加速应用程序上运行仿真调试时,工具不会在断点上停止,而只会在主机代码断点上停止。

在Ubuntu系统中,当试图在内核代码中设置断点的加速应用程序上运行仿真调试时,工具不会在断点上停止,而只会在主机代码断点上停止。

PetaLinux基于Yocto,编译Linux内核、文件系统等,非常庞大,需要的软件很多。如果从网络下载,可能消耗比较长的时间。本文基于Xilinx PetaLinux 2020.2.

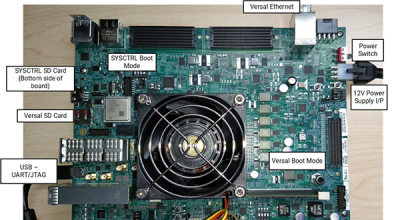

本文提供了一个基于VCK190 ES1开发板和2021.1 Vivado/Vitis的例子,用来简单介绍在Versal里实现数据从PL 经过 FPD CCI 到达 NoC DDR的一致性传输。

本文主要讲述了如何避免FSM输出毛刺。

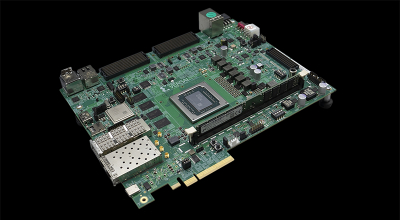

如果您正开发一款智能边缘应用,需要将处理能力融于超紧凑的封装中,那么我们要告诉您一个好消息:Zynq® UltraScale+™ ZU1 MPSoC 现正以更多样的封装形式出货,包括超紧凑 InFO 封装。

我在一个自定义平台上运行我的项目,而我的目标平台的Vivado项目在Vivado合成中使用了以下额外选项。当我运行Vitis链接器时,我看到以下错误。

本章描述了对您所执行的设计流程可能出现的各种问题进行调试的方法。

我们早已迫不及待,此刻终于可以正式发布搭载 AI 引擎的 Versal Premium 系列。新一代无线系统要求高性能信号处理,并能够处理进出计算器件的海量数据。

本文描述了如何在设计的早期阶段使用 Xilinx® Power Estimator (XPE) 工具进行功率分析。