HDMI_1.4_2.0_TX_Subsystem_IP介绍和基础debug建议

judy 在 周五, 03/25/2022 - 09:20 提交

Xilinx HDMI 1.4/2.0 TX的解决方案是由HDMI 1.4/2.0 Transmitter Subsystem IP作为MAC和Video PHY Controller IP作为PHY组成, 在板上, 还有SN65DP159被用作TMDS level shifter

Xilinx HDMI 1.4/2.0 TX的解决方案是由HDMI 1.4/2.0 Transmitter Subsystem IP作为MAC和Video PHY Controller IP作为PHY组成, 在板上, 还有SN65DP159被用作TMDS level shifter

本文介绍FPGA与X86 CPU高速通信的几种方案

目前在X86机箱里插VCK190测试。X86、PCIe Host、Host都是指X86运行的Linux环境。Versal、Endpoint、A72都是指A72运行的Linux环境。Endpoint有时使用EP来简化。

Xilinx HDMI 1.4/2.0 RX的解决方案是由HDMI 1.4/2.0 Receiver Subsystem IP作为MAC和Video PHY Controller IP作为PHY组成,在板上,由外部电阻来实现TMDS level shifter,还有TMDS181作为retimer

本文将介绍一种新型的小型LEO通信卫星的架构,通过实现RL LEOnida解决方案和嵌入式解调算法来提高终端和卫星之间的通信性能。

如何实现浮点累加的PIPELINE II=1?

本文描述了UltraScale™ FPGA的BPI配置和闪存编程技术。

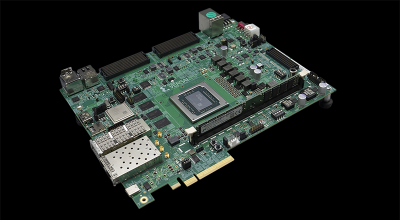

在本视频中,我们将演示 Xilinx Alveo SN1000 SmartNIC 自适应架构如何使客户能够通过易于使用的 P4 可编程框架自定义应用数据路径。

借助基于赛灵思自适应计算平台的SmartNIC,您的数据中心将更高效、更可盈利、更灵活应变并且更安全。

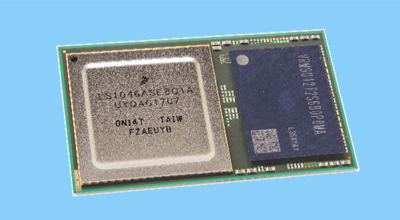

雪湖科技聚焦于智慧交通的的激光雷达 AI 感知,推出了嵌入式 AI 感知边缘计算机 LiDAREYE™。该平台内置赛灵思 Zynq® UltraScale+™ ZU7EV 和雪湖科技自研的 AI 硬件加速引擎与 AI 算法,专为激光雷达 3D 点云的 AI 感知计算而设计