快速上手Xilinx DDR3 IP核(3)——把MIG IP核封装成一个FIFO(上)(Native接口)

judy 在 周三, 03/02/2022 - 11:29 提交

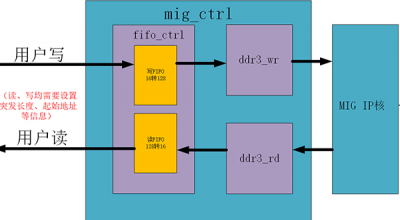

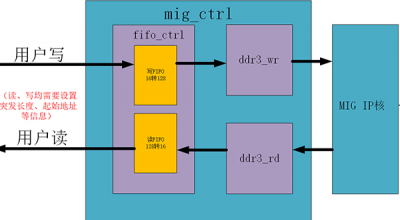

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。

本部分通过将 HLS IP 和 Testbench 设计发送给编译器进行编译和执行,来执行 HLS 流的 C仿真阶段。

本文介绍针对超大规模系统的多通道应用,并将多输入多输出、波束成形和可控延迟与射频通道设计的其他经典要求相结合。

在某些应用中,必须在允许 GTIS 背景校准使用训练信号收敛后冻结 ADC 校准。

使用DSP的方法一般有两种:让综合器自己推断、例化DSP原语。有的时候为了偷懒或者有的计数器之类的需要跑高速,则可以让计数器也使用DSP实现。

根据IDC最新发布数据,全球人工智能收入预计到2022年同比增长19.6%,达到4328亿美元,包括软件、硬件和服务。预计2023年将突破5000亿美元大关。

在Petalinux创建的应用程序模板,只支持编译一个C文件。使用下面的文件,可以编译目录下的所有C、C++文件。

云原生网络功能 (CNF) 是实现网络功能的云原生应用程序。CNF 由一个或多个微服务组成,使用云原生原则开发,包括不可变基础设施、声明性 API 和“可重复部署过程”。

Vivado支持工程模式(ProjectBased Mode)和非工程模式(NoneProject Mode)两种,且都能通过Tcl脚本批处理运行。目前,更多的人使用的是工程模式,今天我们就基于工程模式介绍几个Tcl命令的使用方法。

本文描述使用 STARTUPE3 原语的 Virtex® UltraScale™ FPGA 参考设计,通过专用 BPI 接口实现对 VCU108 板载并行 NOR 闪存的配置后读写访问。