Versal LP/DDR4 2D Eye Scan

judy 在 周五, 02/11/2022 - 09:28 提交

使用 Vivado 2021.1 或更高版本实现的所有 Versal 集成内存控制器接口都支持 2D 眼图扫描功能。2D Eye Scan 可用于检查每个字节通道的健康状况,并允许图形比较以快速识别布局和开发板相关问题。

使用 Vivado 2021.1 或更高版本实现的所有 Versal 集成内存控制器接口都支持 2D 眼图扫描功能。2D Eye Scan 可用于检查每个字节通道的健康状况,并允许图形比较以快速识别布局和开发板相关问题。

我们常说一句话:工欲善其事,必先利其器。作为一名FPGA工程师,我们的任务就是把某些特定的逻辑行为雕刻到FPGA芯片上,通过设计逻辑电路达到预期目的。

以前为ARM64编译软件包,直接在Makefile里指定交叉编译器、sysroot的路径,就能成功编译。

在 2021 OCP 大会上,Xilinx 网络与计算存储产品部负责人 Kartik Srinivasan 做了报告。该报告概括介绍 Xilinx 如何将异构加速引擎结合起来,为满足数据中心网络的动态需求提供最高效方法。

在 Zynq UltraScale+ MPSoC/RFSoC 器件中,Linux CPU Idle 默认启用。启用后,Linux 会在 CPU 内核空闲时关闭它们(与 WFI 相对)。当连接xsdb时,这可能会导致问题。

2022年PYNQ社区将推出更多易用的overlay帮助更多的年轻人入门AIOT,FPGA和软硬件设计。

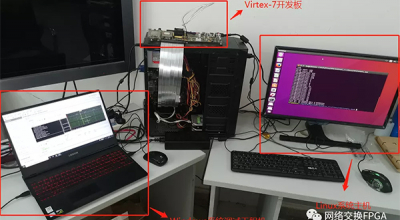

RIFFA 是一种开源通信架构,它允许通过 PCIe 在用户的 FPGA IP 内核和 CPU 的主存储器之间实时交换数据。为了建立其逻辑通道,RIFFA 在 CPU 端拥有一系列软件库,在 FPGA 端拥有 IP 核。本文主要针对其中的DMA性能(Scatter-Gather DMA)进行测试。

在开发FPGA绑定管脚时,经常会看到HP Bank、HR Bank和HD Bank,它们分别是什么意思?分别可以适用于哪些应用个?

人工智能、 5G 和车联网技术的发展,正在重新定义未来汽车的安全和人机交互体验。与此同时,各种智能驾驶技术的迭代与部署也日益加速。