Vitis AI 2.0 全新发布!

judy 在 周五, 01/28/2022 - 14:20 提交

本篇文章将会介绍新产品特性,具体包括模型、软件工具、深度学习处理单元以及最新的性能信息。

本篇文章将会介绍新产品特性,具体包括模型、软件工具、深度学习处理单元以及最新的性能信息。

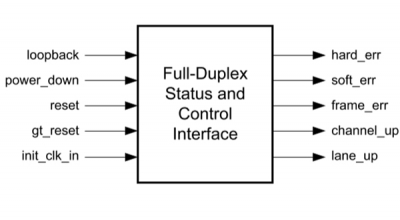

IP是什么?简单来讲,IP就是Xilinx或者第三方开发者把自己的逻辑模块封装成一个黑盒子,然后拿出来给别人用。那什么又是黑盒子?黑盒子就是你看不到里面的东西,你只能看到外面的接口。

本文将使用Tensorflow 2.0从零搭建并训练一个简单的CNN模型来进行数字手势识别,并部署运行在ZynqMP开发板上,来熟悉Vitis AI的工作流程。

想在Windows下完成Xilinx基于Linux的整套开发编译链?觉得虚拟机还是有各种不便?使用WSL2的时候遇到了各种问题?

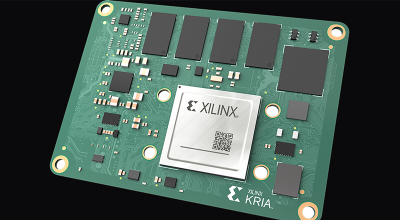

PYNQ官方发布了支持Kria SoM-KV260 Starter Kit)的镜像,此次发布中,Linux部分采用了Kria SoM官方的Ubuntu Linux镜像,所有已有KV260平台的用户可以不用重新烧写SD卡 Linux镜像

FPGA综合和物理实现工具产生许多种报告,包含了错误和警告、逻辑利用、设计频率、时序、时钟等信息。需要设计者了解大量有关设计工具的知识才能阅读报告,以及迅速找到所需信息

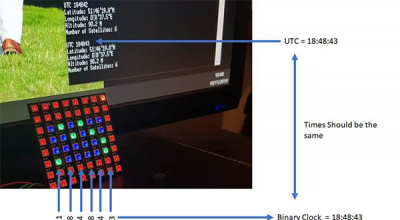

本方案是一个基于 FPGA 的二进制时钟,使用 GPS 作为时间参考。

本篇将重点学习解读后面三章内容:设计约束、设计实现和设计收敛。

Xilinx SDK 可帮助您使用远程主机中的 Xilinx Hardware Server(赛灵思硬件服务器)调试远程目标器件。

本文档描述了在 Kria™ K26 系统模块 (SOM) 基础上使用电源设计管理器的方式。