关于AXI4-FULL总线 多通道传输相同数据时,合并生成一组数据并对齐的研究讨论

judy 在 周五, 12/31/2021 - 09:31 提交

对于AXI4-FULL总线时,握手信号共有5路,包括写地址,写数据,写应答,读地址,读数据。当主机burst写时,每发起一次猝发交易,需要有一笔应答对应。

对于AXI4-FULL总线时,握手信号共有5路,包括写地址,写数据,写应答,读地址,读数据。当主机burst写时,每发起一次猝发交易,需要有一笔应答对应。

多看一些example design之后,你就会发现都是熟悉的配方~

可能很多FPGA初学者在刚开始学习FPGA设计的时候,经常听到类似于”这个信号需要打一拍、打两拍(寄存),以防止亚稳态问题的产生“这种话,但是对这个打拍和亚稳态问题还是一知半解,接下来结合一些资料谈下自己的理解。

在搭建完Block Design以及硬件代码后,生成bit;bit文件生成成功后,点击Export Hardware,导出xsa文件:(xsa做连接使用)

CCF体系结构专委会“开源定制计算”冬令营是主要面向研究生的免费公益活动。由CCF体系结构专委会主办,北京大学高能效计算与应用中心、赛灵思学术合作部联合承办。

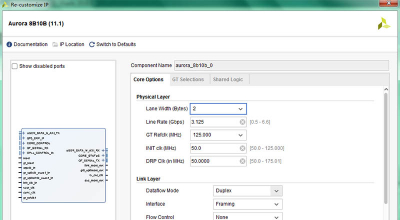

开门见山的说,跟DDR/PCIE/GTX这种复杂的IP相比,Aurora配置那是相当的简单。走着。

在Vitis HLS 工具中,要真正完成AXI总线突发,我们需要一个合适的代码风格并结合恰当的指令设置来达到这个目的。本章节带大家看看如何玩转AXI总线突发读写的代码风格-下。

基于ZYNQ的multiBoot测试

缺陷检测加速应用是一种机器视觉应用,可使用 Xilinx Vitis 视觉加速计算机视觉功能库自动检测缺陷、产品(例如水果、PCB)的成熟度以及在高速工厂管道中进行分类。

许多具有ASIC设计背景的Xllinx用户转向使用FPGA。这些工程师习惯于使用命令行模式下的工具流程,并希望在FPGA设计中继续使用类似的流程。