作者:Li Simon,AMD工程师;来源:AMD开发者社区

Example design simulation是同一个器件的GTM仿真。如果需要做两个芯片GTM对接的仿真,可以用两个GTM wizard,生成example,通过对Example的testbench里做适当修改来实现。

这个例子为了简化,假定两块板子的GTM同样的配置,只是做一个简单的demo。Vivado 2023.2,board:VPK120.

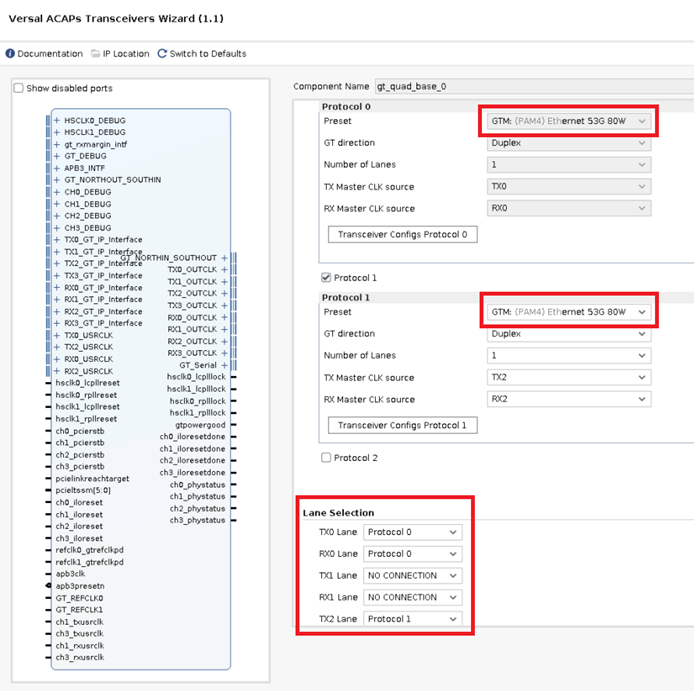

一. 用GTM wizard配置如下,两个通道分别用Ch0和Ch2,生成example design。

二. 参考生成的example design以及testbench,按照需求进行修改。

由于需要是对PAM4的0/1/2/3的进行模拟,因此需要根据当前的层级结构找到位于UNISIM对应的内部变量:CH{0/1/2/3} _GTM{T/R}X{P/N}_integer看,如:CH0_GTMTXN_integer。

以下是对应的_integer连接, PRBS设置,多次复位的一个例子的修改。其他的基本上都是两个参考设计的例子。

always @(*)

begin

//bd0 TX -> bd1 RX

force bd0_bd1_gtm_ch0_n = wrapper_inst_0.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.quad_inst.CH0_GTMTXN_integer;

force bd0_bd1_gtm_ch0_p = wrapper_inst_0.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.quad_inst.CH0_GTMTXP_integer;

force wrapper_inst_1.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.quad_inst.CH0_GTMRXN_integer = bd0_bd1_gtm_ch0_n;

force wrapper_inst_1.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.quad_inst.CH0_GTMRXP_integer = bd0_bd1_gtm_ch0_p;

其他ch1/ch2/ch3类似。

//bd1 TX -> bd0 RX

force bd1_bd0_gtm_ch0_n = wrapper_inst_1.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.quad_inst.CH0_GTMTXN_integer;

force bd1_bd0_gtm_ch0_p = wrapper_inst_1.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.quad_inst.CH0_GTMTXP_integer;

force bd1_bd0_gtm_ch1_n =

force wrapper_inst_0.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.quad_inst.CH0_GTMRXN_integer = bd1_bd0_gtm_ch0_n;

force wrapper_inst_0.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.quad_inst.CH0_GTMRXP_integer = bd1_bd0_gtm_ch0_p;

其他ch1/ch2/ch3类似

end

PRBS 设置:

always@(*) begin

//for wrapper_inst0 quad

force wrapper_inst_0.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.ch0_rxprbssel = 5;

force wrapper_inst_0.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.ch0_txprbssel = 5;

force wrapper_inst_1.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.ch0_rxprbssel = 5;

force wrapper_inst_1.gt_quad_base_0_exdes_bd_i.gt_quad_base_0.inst.ch0_txprbssel = 5;

end

initial

begin

rate_sel_ip0 = 4'h0;

rate_sel_ip1 = 4'h0;

gtresetip0 = 1'b0;

gtresetip1 = 1'b0;

#800ns;

gtresetip0 = 1'b1;

gtresetip1 = 1'b1;

#60ns;

gtresetip0 = 1'b0;

gtresetip1 = 1'b0;

//repeat 20 times reset ch2 and ch0

repeat (20) begin

#140000ns;

//gtresetip0 = 1'b1;

gtresetip1 = 1'b1;//reset ch2

#60ns;

//gtresetip0 = 1'b0;

gtresetip1 = 1'b0;//release ch2

#140000ns;

gtresetip0 = 1'b1;//reset ch0

//gtresetip1 = 1'b1;

#60ns;

gtresetip0 = 1'b0;

//gtresetip1 = 1'b0;//release ch0

end

end

Example simulation包括提供了free running的时钟和GTM参考钟,以及对reset模块的reset all。完成复位之后,会提供激励对link的检测。仿真脚本也包括了对PLL lock检测,时钟频率的检测,如果多速率切换的仿真。

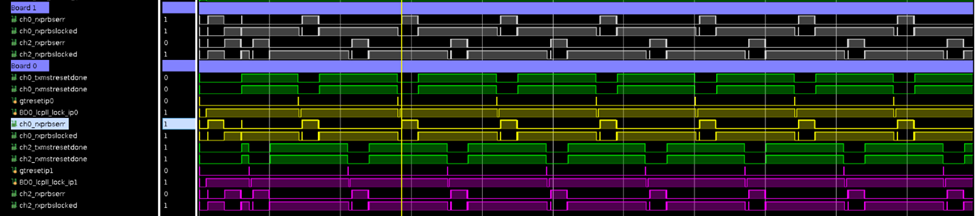

三.仿真结果如下,多次复位测试以及PRBS测试两块板子对接,附上测试的testbench:

更多信息可以参考PG315第7章,PG331的第5章。