FPGA的虚拟时钟如何使用?

judy 在 周二, 12/07/2021 - 10:06 提交

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟,但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟,但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

PetaLinux新特性,可以指定Linux configuration。Linux configuration文件要放在Linux代码的目录arch/arm64/configs里。使用petalinux-config配置时,指定文件名就可以,不用指定目录。

了解 Xilinx Alveo™ U50LV 加速卡如何为快手的 ASR 服务提供低延迟和高吞吐量优势。

作为与赛灵思合作最为紧密的技术分销伙伴,安富利将在下周携手赛灵思和安森美于12月7日-9日在福州市、厦门市、深圳市几个城市中巡回举办“Kria SOM Workshop”的活动。

Xilinx 发布的Linux Kernel,默认包含了以下选项

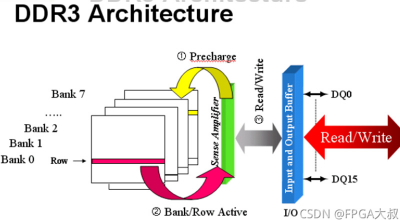

DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的

Xilinx FPGA MicroBlaze使用AXI 1G/2.5G Ethernet Subsystem(= Tri Mode Ethernet MAC + AXI Ethernet Buffer)以太网IP核驱动RTL8211FD千兆网口,并使用lwip2.1.2协议栈建立http服务器,支持IPv6

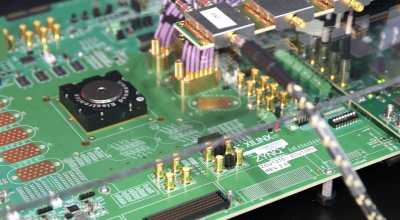

Kintex UltraScale FPGA KCU105 评估套件使用 MAX15301 及 MAX15303 PMBus 稳压器以及 MAX20751E 主控基于 Maxim PMBus 的电源系统。

MicroBlaze™处理器参考指南提供了有关32位和64位软处理器MicroBlaze的信息,它是Vivado®设计套件的一部分。该文件旨在作为MicroBlaze硬件架构的指南。

在IBERT测试中需要注意的有以下两个要点