Xilinx FPGA的DNA是什么?

judy 在 周一, 11/08/2021 - 09:47 提交

对于Xilinx的FPGA,每一片都有一个专门的ID,就像我们的身份证号一样,每个都不一样,Xilinx也形象的把这个ID叫做DNA。7系列以及之前FPGA的DNA有57bit,Ultrascale FPGA的DNA有96bit,Zynq Ultrascale+的FPGA有两个DNA,PL端一个,PS端也有一个。

对于Xilinx的FPGA,每一片都有一个专门的ID,就像我们的身份证号一样,每个都不一样,Xilinx也形象的把这个ID叫做DNA。7系列以及之前FPGA的DNA有57bit,Ultrascale FPGA的DNA有96bit,Zynq Ultrascale+的FPGA有两个DNA,PL端一个,PS端也有一个。

在全球电子工程领域知名媒体机构 ASPENCORE 主办的“2020 全球电子成就奖(World Electronics Achievement Awards)”上,赛灵思凭借 Kria 自适应系统模块 SOM 产品组合获得“2021 全球电子成就奖年度处理器/DSP/FPGA(Processor/DSP/FPGA of the Year)”殊荣。

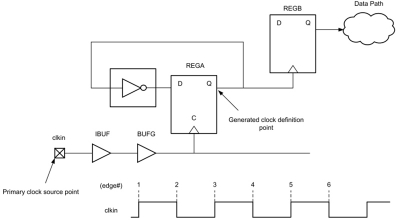

为了获得最佳精度路径覆盖信息,必须正确定义时钟。

时钟要定义在时钟树的根 pin 或 port 上,称为 source point。

时钟的边缘应该由周期和波形进行组合描述。

周期使用纳秒做为单位进行定义。它对应于波形重复的时间。

BittWare提供StreamSurge,这是一个用于BittWare的XUP-P3R加速卡的100G网络负载测试应用。StreamSurge作为预编译的比特流免费提供给XUP-P3R用户,使该卡成为一个简单的网络测试解决方案,只需支付硬件成本。

赛灵思2021自适应计算挑战赛自9月7日正式开赛以来,收到了来自全球各地区的FPGA软硬件开发者们的积极关注以及踊跃报名!通过挑战赛我们希望开发者能运用 Vivado 设计套件、Vitis 开发环境和 Vitis AI 统一软件平台发挥赛灵思自适应计算平台的强大功能,开启创新思路,解决实际问题。

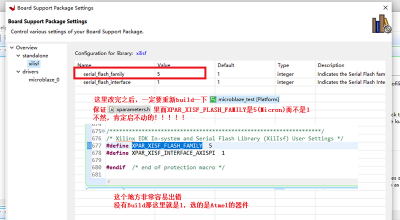

FPGA的型号为XC7A35TFGG484-2,开发板用的是米联客的。主程序hello_world运行于外部DDR3内存,SREC SPI Bootloader运行于FPGA片内BRAM。

本应用说明讨论了如何使用新颖的全数字压控晶体振荡器(VCXO)替代技术,利用Virtex-6 FPGA实现锁频的三倍速率直通设计。该设计完全在Virtex®-6 FPGA内部实现。

在前面的学习中,我们已经学会了使用Vivado及SDK开发环境,熟悉了硬件开发与Linux软件驱动之间的联系及开发流程。本系列教程我们学习SDSoc的开发,在SDSoc IDE中,Xilinx为我们集成了比较流行的开发板硬件平台,如果我们使用的是其中的一个,可以直接使用。但笔者使用的是米尔科技的7z010开发板,在开发之前首先要定义我们自己的硬件平台,作为之后创建应用的模板工程

分享面试中经常遇到的5个FPGA基本概念

今年的夏天,对赛灵思中国 AI产品团队来说是一个不平凡的夏季: 在相继举行的一年一度 2021 CVPR ,以及 2021 ICCV上,我们的团队每个大会各斩获两份荣誉,“双奖”连连,激动人心。无疑是对赛灵思 AI 产品团队在全球竞争领域技术实力和创新能力的高度认可和有力证明。