MCU创新先锋奖 | 投票

投票已结束!

投票已结束!

SOC、SOPC、MPSOC、RFSOC、SDSOC的概念及区别

第四期课程是 PowerVR 性能建议指南的简化版本。它包含了开发人员在编写应用程序时应使用的各种经验法则和建议。在应用程序中实施这些技巧可能会对 PowerVR 设备上的应用性能产生重大影响。

在Vitis AI library中的模型在自定义单板使用中,介绍了如何进行模型库编译,下一步要将模型加入到AI应用中进行编译,生成可执行文件。

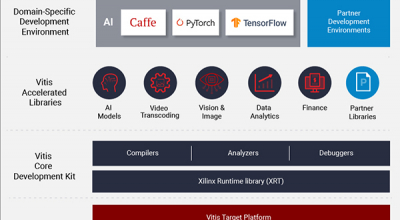

本系列笔记旨在更深入的探索Vitis以及Vitis内部所使用到的技术,本系列主要针对深度学习部署进行探索,比如自定义自己的深度学习硬件平台,深度学习模型量化、模型编译、TVM自动调优,多DPU核异构系统的调度计算等等。

本文通过使用 Design Gateway 的 TOE100G-IP 内核和 NVMeG4-IP 内核,在 Xilinx 的 KCU116 评估套件上演示了 TCP 卸载引擎网络和 NVMe SSD 实现的100Gbps 解决方案。

在Vitis AI设计中,构建模型是其中非常重要的一步。如果使用调用的模型库呢?

设计创新型无线通信设备需要跨多个学科密切合作。将算法模型部署到 FPGA 硬件可以快速完成原型设计及无线测试,直接从系统级算法自动生成 HDL 代码则可以消除耗时较长的实现和验证步骤。本白皮书通过一个 5G NR 小区搜索设计来说明该过程,介绍将 MATLAB® 算法和 Simulink® 模型直接转换为适用于 FPGA 的 HDL 的工作流。

双核S7-VU19P逻辑系统配置了双颗赛灵思 UltraScale+ VU19P FPGA,多套逻辑系统可堆叠或机架部署,以支持更大逻辑规模的设计。搭配芯神瞳协同仿真套件轻松实现将设计链接到原型验证环境,允许大量的事务级数据在 FPGA 与 PC 主机之间进行交互;同时可选配内置的深度调试套件 MDM Pro,用于多颗FPGA的深度调试

本篇博文中的分析是根据真实客户问题撰写的,该客户发现硬件中存在 DDR4 校准错误,不同板以及不同构建 (build) 之间出现的故障并不一致。本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。