Vitis AI DPU代码分析

judy 在 周四, 09/02/2021 - 14:42 提交

Vitis AI开发套件提供high-leve C++/Python APIs(VART)进行从云到边器件开发。对于边缘DPU,除了VART,还可以使用advanced low-level C++/Python APIs。

Vitis AI开发套件提供high-leve C++/Python APIs(VART)进行从云到边器件开发。对于边缘DPU,除了VART,还可以使用advanced low-level C++/Python APIs。

新兴的 5G 网络依托毫米波频谱运行,这意味着 5G 网络的性能优于 4G 网络,能够以更高的速度、更低的延迟传输更多数据。毫米波频谱技术发展前景广阔,但也使设备制造商面临大量设计挑战。例如,相比低频信号,毫米波频谱信号更易因大气及其他物体的阻隔而衰减。

Xilinx 多任务模型旨在同时完成不同的图像感知任务,同时实现高性能和高效率。凭借 MTLv3 模型,以及在 Vitis AI 的助力下,现可实现面向车辆检测、车道检测、分割、可行驶区域检测和深度评估的 5 个任务,基于一个模型,在边缘实时速度运行。

美国迪芝伦科技有限公司(Digilent)生产开发板和套件以及各种测试测量工具,借助便携式仪器的灵活性,为工程师、研究人员和学生提供专业级的分析能力。作为赛灵思技术的长期用户,该公司继续采用赛灵思 SoC 和 FPGA 器件,开发出两款功能强大的新型测试测量设备,为客户带来更高性能、更低成本和更强的灵活性。

今天,赛灵思与 DFRobot 宣布启动“科技女性创客马拉松”,号召大中华区科技女性利用赛灵思 Pynq 开源框架构建物联网应用,将创新想法变为现实。本次创客马拉松采取团队形式。赛灵思将为参赛者需提供基于 Python 的 Pynq 开发板,用于构建物联网设计。Pynq 开发板兼具树莓派和 Arduino 的强大功能,以及赛灵思 FPGA 的快速、并行特性和可定制逻辑。

赛灵思与魔视智能今日宣布,双方正合作推出一款面向汽车市场的解决方案。它将赛灵思车规级( XA ) Zynq® 片上系统( SoC )平台与魔视智能的卷积神经网络( CNN )IP 相结合,专门用于前视摄像头系统的车辆感知与控制。

欢迎参加Xilinx官方授权培训提供商-依元素科技举办的在线培训活动,专注于Versal®ACAP平台开发!了解最新的 Xilinx Versal ACAP 平台及其组成模块,支持更灵活地实现系统加速;Versal独有的功能特性,如人工智能引擎(AIE)和片上网络(NoC),将在Vitis统一软件工具流程中覆盖支持;

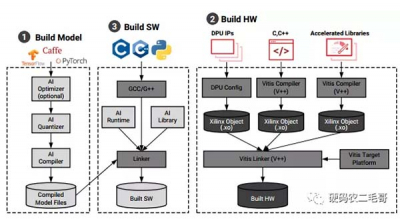

本文对vitis设计流程进行总结

第三期课程对 3D 图形中所有重要概念进行了详细解释,将为你在开始图形开发之旅打下坚实的基础。

在一些工业应用中不管出于成本还是功耗又或者集成难度可能不需要DDR,这些系统只需要很小的内存空间来存储和执行其应用程序,对于这些系统OCM可以满足其与存储器相关的需求。本文主要介绍在OCM空间不足时从flash执行应用程序时如何提高性能。